#### APPENDIX B

# SPICE DEVICE MODELS AND DESIGN SIMULATION EXAMPLES USING PSPICE AND MULTISIM

## Introduction

This appendix is concerned with the very important topic of using PSpice and Multisim to simulate the operation of electronic circuits. The need for and the role of computer simulation in circuit design was described in the preface. The appendix has three sections: Section B.1 presents a brief description of the models that SPICE uses to describe the operation of op amps, diodes, MOSFETs, and BJTs. Section B.2 presents design and simulation examples using PSpice. Finally, design and simulation examples utilizing Multisim are presented in Section B.3. The examples are keyed to the book chapters and are numbered in a way that makes this relationship transparent. Thus, Example PS.2.1 refers to the first PSpice simulation example on Chapter 2 material. Similarly, Example MS.5.2 refers to the second Multisim simulation example on Chapter 5 material.

Besides the descriptions presented in this appendix, the reader will find the complete simulation files for each example on the book website.

# **B.1 SPICE Device Models**

To the designer, the value of simulation results is a direct function of the quality of the models used for the devices. The more faithfully the model represents the various characteristics of the device, the more accurately the simulation results will describe the operation of an actual fabricated circuit. In other words, to see the effect on circuit performance of various imperfections in device operation, these imperfections must be included in the device model used by the circuit simulator.

# **B.1.1 The Op-Amp Model**

In simulating circuits that use one or more op amps, it is useful to utilize a **macromodel** to represent each op amp. A macromodel is based on the observed terminal characteristics of the op amp rather than on the modeling of every transistor in the op-amp internal circuit. Macromodels can be developed from data-sheet specifications without knowledge of the details of the internal circuitry of the op amp.

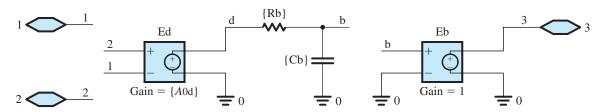

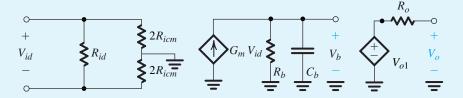

**Linear Macromodel** The schematic capture of a linear macromodel for an internally compensated op amp with finite gain and bandwidth is shown in Fig. B.1. In this equivalent-circuit model, the gain constant  $A_{0d}$  of the voltage-controlled voltage source  $E_d$  corresponds to the differential gain of the op amps at dc. Resistor  $R_b$  and capacitor  $C_b$  form a

single-time-constant (STC) filter with a corner frequency

$$f_b = \frac{1}{2\pi R_b C_b} \tag{B.1}$$

The low-pass response of this filter is used to model the frequency response of the internally compensated op amp. The values of  $R_b$  and  $C_b$  used in the macromodel are chosen such that  $f_b$  corresponds to the 3-dB frequency of the op amp being modeled. This is done by arbitrarily selecting a value for either  $R_b$  or  $C_b$  (the selected value does not need to be a practical one) and then using Eq. (B.1) to compute the other value. In Fig. B.1, the voltage-controlled voltage source  $E_b$  with a gain constant of unity is used as a buffer to isolate the low-pass filter from any load at the op-amp output. Thus any op-amp loading will not affect the frequency response of the filter and hence that of the op amp.

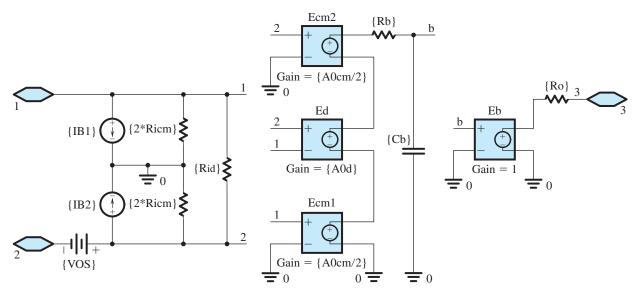

The linear macromodel in Fig. B.1 can be further expanded to account for other op-amp nonidealities. For example, the equivalent-circuit model in Fig. B.2 can be used to model an internally compensated op amp while accounting for the following op-amp nonidealities:

1. Input Offset Voltage ( $V_{os}$ ). The dc voltage source  $V_{os}$  models the op-amp input offset voltage.

Figure B.1 A linear macromodel used to model the finite gain and bandwidth of an internally compensated op amp.

Figure B.2 A comprehensive linear macromodel of an internally compensated op amp.

**2.** Input Bias Current  $(I_B)$  and Input Offset Current  $(I_{OS})$ . The dc current sources  $I_{B1}$  and  $I_{B2}$  model the input bias current at each input terminal of the op amp, with

$$I_{B1} = I_B + \frac{I_{OS}}{2}$$

and  $I_{B2} = I_B - \frac{I_{OS}}{2}$

where  $I_B$  and  $I_{OS}$  are, respectively, the input bias current and the input offset current specified by the op-amp manufacturer.

- **3.** Common-Mode Input Resistance ( $R_{icm}$ ). If the two input terminals of an op amp are tied together and the input resistance (to ground) is measured, the result is the common-mode input resistance  $R_{icm}$ . In the macromodel of Fig. B.2, we have split  $R_{icm}$  into two equal parts  $(2R_{icm})$ , each connected between one of the input terminals and ground.

- **4.** Differential-Input Resistance  $(R_{id})$ . The resistance seen between the two input terminals of an op amp is the differential input resistance  $R_{id}$ .

- 5. Differential Gain at DC  $(A_{0d})$  and Common-Mode Rejection Ratio (CMRR). The output voltage of an op amp at dc can be expressed as

$$V_3 = A_{0d} (V_2 - V_1) + \frac{A_{0cm}}{2} (V_1 + V_2)$$

(B.2)

where  $A_0d$  and  $A_{0cm}$  are, respectively, the differential and common-mode gains of the op amp at dc. For an op amp with a finite CMRR,

$$A_{0cm} = A_{0d} / \text{CMRR} \tag{B.3}$$

where CMRR is expressed in V/V (not in dB). In the macromodel of Fig. B.2, the voltage-controlled voltage sources  $E_{cm1}$  and  $E_{cm2}$  with gain constants of  $A_{0cm}/2$  account for the finite CMRR while source  $E_d$  models  $A_{0d}$ .

**6.** Unity-Gain Frequency  $(f_t)$ . From Eq. (2.46), the 3-dB frequency  $f_b$  and the unity-gain frequency (or gain-bandwidth product)  $f_t$  of an internally compensated op amp with an STC frequency response are related by

$$f_b = \frac{f_t}{A_{0d}} \tag{B.4}$$

As in Fig. B.1, the finite op-amp bandwidth is accounted for in the macromodel of Fig. B.2 by setting the corner frequency of the filter formed by resistor  $R_b$  and capacitor  $C_b$  (Eq. B.1) to equal the 3-dB frequency of the op amp,  $f_b$ .

7. Ouput Resistance  $(R_a)$ . The resistance seen at the output terminal of an op amp is the output resistance  $R_o$ .

The linear macromodels in Figs. B.1 and B.2 assume that the op-amp circuit is operating in its linear range and do not account for its nonideal performance when large signals are present at the output. Therefore, nonlinear effects, such as output saturation and slew rate, are not modeled.

**Nonlinear Macromodel** The linear macromodel in Fig. B.2 can be expanded to account for the op-amp nonlinear performance. For example, the finite output voltage swing of the op amp can be modeled by placing limits on the output voltage of the voltage-controlled voltage source E<sub>b</sub>. In PSpice, this can be done using the ETABLE component in the analog-behavioral-modeling (ABM) library and setting the output voltage limits in the lookup table of this component. Further details on how to build nonlinear macromodels for the op amp can be found in the references on SPICE simulation. In general, robust macromodels that account for the nonlinear effects in an IC are provided by the op-amp manufacturers. Most simulators include such macromodels for some of the popular off-the-shelf ICs in their libraries. For example, PSpice and Multisim include models for the  $\mu A741$ , the LF411, and the LM324 op amps.

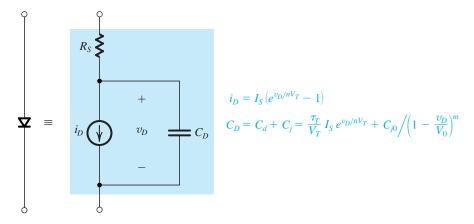

#### **B.1.2 The Diode Model**

The large-signal SPICE model for the diode is shown in Fig. B.3. The static behavior is modeled by the exponential i-v relationship. Here, for generality, a constant n is included in the exponential. It is known as the **emission cofficient**, and its value ranges from 1 to 2. In our study of the diode in Chapter 4, we assumed n=1. The dynamic behavior is represented by the nonlinear capacitor  $C_D$ , which is the sum of the diffusion capacitance  $C_d$  and the junction capacitance  $C_j$ . The series resistance  $R_S$  represents the total resistance of the p and n regions on both sides of the junction. The value of this parasitic resistance is ideally zero, but it is typically in the range of a few ohms for small-signal diodes. For small-signal analysis, SPICE uses the diode incremental resistance  $r_d$  and the incremental values of  $C_d$  and  $C_j$ .

Table B.1 provides a partial listing of the diode-model parameters used by SPICE, all of which should be familiar to the reader. But having a good device model solves only half of the modeling problem; the other half is to determine appropriate values for the model parameters. This is by no means an easy task. The values of the model parameters are determined using a combination of characterization of the device-fabrication process and specific measurements performed on the actual manufactured devices. Semiconductor manufacturers expend enormous effort and money to extract the values of the model parameters for their devices. For discrete diodes, the values of the SPICE model parameters can be determined from the diode data sheets, supplemented if needed by key measurements. Circuit simulators (such as PSpice) include in their libraries the model parameters of some of the popular off-the-shelf components. For instance, in Example PS4.1, we will use the commercially available D1N418 *pn*-junction diode whose SPICE model parameters are available in PSpice.

Figure B.3 The SPICE diode model.

| Table B.1 Param | eters of the SPICE D | viode Model (Partial Listing)              |       |

|-----------------|----------------------|--------------------------------------------|-------|

| SPICE Parameter | Book Symbol          | Description                                | Units |

| IS              | $I_S$                | Saturation current                         | A     |

| N               | n                    | Emission coefficient                       |       |

| RS              | $R_S$                | Ohmic resistance                           | Ω     |

| VJ              | $V_0$                | Built-in potential                         | V     |

| CJ0             | $C_i0$               | Zero-bias depletion (junction) capacitance | F     |

| M               | m                    | Grading coefficient                        |       |

| TT              | $	au_T$              | Transit time                               | S     |

| BV              | $V_{ZK}$             | Breakdown voltage                          | V     |

| IBV             | $I_{ZK}$             | Reverse current at $V_{ZK}$                | A     |

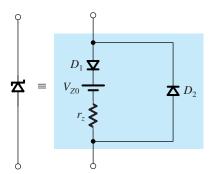

Figure B.4 Equivalent-circuit model used to simulate the zener diode in SPICE. Diode  $D_1$  is ideal and can be approximated in SPICE by using a very small value for n (say

#### **B.1.3 The Zener Diode Model**

The diode model in Fig. B.3 does not adequately describe the operation of the diode in the breakdown region. Hence, it does not provide a satisfactory model for zener diodes. However, the equivalent-circuit model shown in Fig B.4 can be used to simulate a zener diode in SPICE. Here, diode  $D_1$  is an ideal diode that can be approximated in SPICE by using a very small value for n (say n = 0.01). Diode  $D_2$  is a regular diode that models the forward-bias region of the zener (for most applications, the parameters of  $D_2$  are of little consequence).

#### **B.1.4 MOSFET Models**

To simulate the operation of a MOSFET circuit, a simulator requires a mathematical model to represent the characteristics of the MOSFET. The model we derived in Chapter 5 to represent the MOSFET is a simplified or first-order model. This model, called the **square-law model** because of the quadratic i-v relationship in saturation, works well for transistors with relatively *long* channels. However, for devices with *short* channels, especially deep-submicron transistors, many physical effects that we neglected come into play, with the result that the derived first-order model no longer accurately represents the actual operation of the MOSFET (see Sections 5.4.4 & 15.1.3).

The simple square-law model is useful for understanding the basic operation of the MOSFET as a circuit element and is indeed used to obtain approximate pencil-and-paper circuit designs. However, more elaborate models, which account for short-channel effects, are required to be able to predict the performance of integrated circuits with a certain degree of precision prior to fabrication. Such models have indeed been developed and continue to **B-6** Appendix B

be refined to more accurately represent the higher-order effects in short-channel transistors through a mix of physical relationships and empirical data. Examples include the Berkeley short-channel IGFET model (BSIM) and the EKV model, popular in Europe. Currently, semiconductor manufacturers rely on such sophisticated models to accurately represent the fabrication process. These manufacturers select a MOSFET model and then extract the values for the corresponding model parameters using both their knowledge of the details of the fabrication process and extensive measurements on a variety of fabricated MOSFETs. A great deal of effort is expended on extracting the model parameter values. Such effort pays off in fabricated circuits exhibiting performance very close to that predicted by simulation, thus reducing the need for costly redesign.

Although it is beyond the scope of this book to delve into the subject of MOSFET modeling and short-channel effects, it is important that the reader be aware of the limitations of the square-law model and of the availability of more accurate but, unfortunately, more complex MOSFET models. In fact, the power of computer simulation is more apparent when one has to use these complex device models in the analysis and design of integrated circuits.

SPICE-based simulators, like PSpice and Multisim, provide the user with a choice of MOSFET models. The corresponding SPICE model parameters (whose values are provided by the semiconductor manufacturer) include a parameter called LEVEL, which selects the MOSFET model to be used by the simulator. Although the value of this parameter is not always indicative of the accuracy, nor of the complexity of the corresponding MOSFET model, LEVEL = 1 corresponds to the simplest first-order model (called the Shichman-Hodges model), which is based on the square-law MOSFET equations presented in Chapter 5. For simplicity, we will use this model to illustrate the description of the MOSFET model parameters in SPICE and to simulate the example circuits in PSpice and Multisim. However, the reader is again reminded of the need to use a more sophisticated model than the level-1 model to accurately predict the circuit performance, especially for deep, submicron transistors.

MOSFET Model Parameters Table B.2 provides a listing of some of the MOSFET model parameters used in the level-1 model of SPICE. The reader should already be familiar with these parameters, except for a few, which are described next.

**MOSFET Diode Parameters** For the two reverse-biased diodes formed between each of the source and drain diffusion regions and the body (see Fig. B.4), the saturation-current density is modeled in SPICE by the parameter JS. Furthermore, based on the parameters specified in Table B.2, SPICE will calculate the depletion-layer (junction) capacitances discussed in Section 10.2.1 as

$$C_{db} = \frac{\text{CJ}}{\left(1 + \frac{V_{DB}}{\text{PB}}\right)^{\text{MJ}}} \text{AD} + \frac{\text{CJSW}}{\left(1 + \frac{V_{DB}}{\text{PB}}\right)^{\text{MJSW}}} \text{PD}$$

(B.5)

$$C_{sb} = \frac{\text{CJ}}{\left(1 + \frac{V_{SB}}{\text{PB}}\right)^{\text{MJ}}} \text{AS} + \frac{\text{CJSW}}{\left(1 + \frac{V_{SB}}{\text{PB}}\right)^{\text{MJSW}}} \text{PS}$$

(B.6)

where AD and AS are the areas, while PD and PS are the perimeters of, respectively, the drain and source regions of the MOSFET. The first capacitance term in Eqs. (B.5) and (B.6) represents the depletion-layer (junction) capacitance over the bottom plate of the drain and source regions. The second capacitance term accounts for the depletion-layer capacitance along the sidewall (periphery) of these regions. Both terms are expressed using the formula

| SPICE Parameter | Book Symbol | Description                                                                                                              | Units                |

|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

|                 |             | Basic Model Parameters                                                                                                   |                      |

| LEVEL           |             | MOSFET model selector                                                                                                    |                      |

| TOX             | $t_{ox}$    | Gate-oxide thickness                                                                                                     | m                    |

| COX             | $C_{ox}$    | Gate-oxide capacitance, per unit area                                                                                    | F/m <sup>2</sup>     |

| UO              | $\mu$       | Carrier mobility                                                                                                         | cm <sup>2</sup> /V·s |

| KP              | k'          | Process transconductance parameter                                                                                       | $A/V^2$              |

| LAMBDA          | λ           | Channel-length modulation coefficient                                                                                    | $V^{-1}$             |

|                 |             | Threshold Voltage Parameters                                                                                             |                      |

| VTO             | $V_{t0}$    | Zero-bias threshold voltage                                                                                              | V                    |

| GAMMA           | γ           | Body-effect parameter                                                                                                    | $V^{1/2}$            |

| NSUB            | $N_A, N_D$  | Substrate doping                                                                                                         | $\mathrm{cm}^{-3}$   |

| PHI             | $2\phi_f$   | Surface inversion potential                                                                                              | V                    |

|                 |             | MOSFET Diode Parameters                                                                                                  |                      |

| JS              |             | Body-junction saturation-current density                                                                                 | $A/m^2$              |

| CJ              |             | Zero-bias body-junction capacitance, per unit area over the drain/source region                                          | F/m <sup>2</sup>     |

| MJ              |             | Grading coefficient, for area component                                                                                  |                      |

| CJSW            |             | Zero-bias body-junction capacitance, per unit length<br>along F/m the sidewall (periphery) of the drain/source<br>region |                      |

| MJSW            |             | Grading coefficient, for sidewall component                                                                              |                      |

| PB              | $V_0$       | Body-junction built-in potential                                                                                         | V                    |

|                 |             | MOSFET Dimension Parameters                                                                                              |                      |

| LD              | $L_{ov}$    | Lateral diffusion into the channel                                                                                       | m                    |

|                 |             | from the source/drain diffusion regions                                                                                  |                      |

| WD              |             | Sideways diffusion into the channel                                                                                      | m                    |

|                 |             | from the body along the width                                                                                            |                      |

|                 |             | MOS Gate-Capacitance Parameters                                                                                          |                      |

| CGBO            |             | Gate-body overlap capacitance, per unit channel length                                                                   | F/m                  |

| CGDO            | $C_{ov}/W$  | Gate-drain overlap capacitance, per unit channel width                                                                   | F/m                  |

| CGSO            | $C_{ov}/W$  | Gate-source overlap capacitance, per unit channel width                                                                  | F/m                  |

developed in Section 3.6.1 (Eq. 3.56). The values of AD, AS, PD, and PS must be specified by the user based on the dimensions of the device being used.

MOSFET Dimension and Gate-Capacitance Parameters In a fabricated MOSFET, the effective channel length  $L_{\mathrm{eff}}$  is shorter than the nominal (or drawn) channel length L (as specified by the designer) because the source and drain diffusion regions extend slightly under the gate oxide during fabrication. Furthermore, the effective channel width  $W_{\rm eff}$  of the MOSFET is shorter than the nominal or drawn channel width W because of the sideways diffusion into the channel from the body along the width. Based on the parameters specified in Table B.2,

$$L_{\text{eff}} = L - 2LD \tag{B.7}$$

$$W_{\rm eff} = W - 2WD \tag{B.8}$$

In a manner analogous to using  $L_{ov}$  to denote LD, we will use the symbol  $W_{ov}$  to denote WD. Consequently, as indicated in Section 10.2.1, the gate-source capacitance  $C_{gs}$  and the gate-drain capacitance  $C_{gd}$  must be increased by an overlap component of, respectively,

$$C_{gs,ov} = W \text{ CGSO} \tag{B.9}$$

and

$$C_{pd,ov} = W \text{CGDO} \tag{B.10}$$

Similarly, the gate-body capacitance  $C_{gb}$  must be increased by an overlap component of

$$C_{ob\ ov} = L \text{CGBO} \tag{B.11}$$

The reader may have observed that there is a built-in redundancy in specifying the MOSFET model parameters in SPICE. For example, the user may specify the value of KP for a MOSFET or, alternatively, specify TOX and UO and let SPICE compute KP as UO TOX. Similarly, GAMMA can be directly specified, or the physical parameters that enable SPICE to determine it can be specified (e.g., NSUB). In any case, the user-specified values will always take precedence over (i.e., override) those values calculated by SPICE. As another example, note that the user has the option of either directly specifying the overlap capacitances CGBO, CGDO, and CGSO or letting SPICE compute them as CGDO = CGSO = LD COX and CGBO = WD COX.

Table B.3 provides typical values for the level-1 MOSFET model parameters of a modern 0.18-μm CMOS technology and for older 0.5-μm and 5-μm CMOS technologies. The corresponding values for the minimum channel length  $L_{\min}$ , minimum channel width  $W_{\min}$ and the maximum supply voltage  $(V_{DD} + |V_{SS}|)_{max}$  are as follows:

| Technology   | $L_{\scriptscriptstyle{ m min}}$ | $W_{ m min}$ | $\left(V_{DD} + \left V_{SS}\right \right)_{\max}$ |

|--------------|----------------------------------|--------------|----------------------------------------------------|

| 5-μm CMOS    | 5 μm                             | 12.5 μm      | 10 V                                               |

| 0.5-μm CMOS  | 0.5 μm                           | 1.25 μm      | 3.3 V                                              |

| 0.18-μm CMOS | 0.18 μm                          | 0.22 μm      | 1.8 V                                              |

When simulating a MOSFET circuit, the user needs to specify both the values of the model parameters and the dimensions of each MOSFET in the circuit being simulated. At least the channel length L and width W must be specified. The areas AD and AS and the perimeters PD and PS need to be specified for SPICE to model the body-junction capacitances (otherwise, zero capacitances would be assumed). The exact values of these geometry parameters depend on the actual layout of the device (Appendix A). However, to estimate these dimensions, we will assume that a metal contact is to be made to each of the source and drain regions of the MOSFET. For this purpose, typically, these diffusion regions must be extended past the end of the channel (i.e., in the L-direction in Fig. 5.1) by at least 2.75  $L_{\min}$ . Thus, the minimum area and perimeter of a drain/source diffusion region with a contact are, respectively,

$$AD = AS = 2.75 L_{min} W$$

(B.12)

| Table B.3 | Values of the Level-1 MOSFET Model Parameters for Two CMOS Technologies <sup>1</sup> |           |           |             |            |             |

|-----------|--------------------------------------------------------------------------------------|-----------|-----------|-------------|------------|-------------|

|           | 5-μm CMO                                                                             | S Process | 0.5-μm CM | IOS Process | 0.18-μm Cl | MOS Process |

|           | NMOS                                                                                 | PMOS      | NMOS      | PMOS        | NMOS       | PMOS        |

| LEVEL     | 1                                                                                    | 1         | 1         | 1           | 1          | 1           |

| TOX       | 8.50e-08                                                                             | 8.50e-08  | 9.50e-09  | 9.50e-09    | 4.08e-09   | 4.08e-09    |

| UO        | 750                                                                                  | 250       | 460       | 115         | 291        | 102         |

| LAMBDA    | 0.01                                                                                 | 0.03      | 0.1       | 0.2         | 0.08       | 0.11        |

| GAMMA     | 1.4                                                                                  | 0.65      | 0.5       | 0.45        | 0.3        | 0.3         |

| VTO       | 1                                                                                    | -1        | 0.7       | -0.8        | 0.5        | -0.45       |

| PHI       | 0.7                                                                                  | 0.65      | 0.8       | 0.75        | 0.84       | 0.8         |

| LD        | 7.00e-07                                                                             | 6.00e-07  | 8.00e-08  | 9.00e-08    | 10e-9      | 10e.9       |

| JS        | 1.00e-06                                                                             | 1.00e-06  | 1.00e-08  | 5.00e-09    | 8.38e-6    | 4.00e-07    |

| CJ        | 4.00e-04                                                                             | 1.80e-04  | 5.70e-04  | 9.30e-04    | 1.60e-03   | 1.00e-03    |

| MJ        | 0.5                                                                                  | 0.5       | 0.5       | 0.5         | 0.5        | 0.45        |

| CJSW      | 8.00e-10                                                                             | 6.00e-10  | 1.20e-10  | 1.70e-10    | 2.04e-10   | 2.04e-10    |

| MJSW      | 0.5                                                                                  | 0.5       | 0.4       | 0.35        | 0.2        | 0.29        |

| PB        | 0.7                                                                                  | 0.7       | 0.9       | 0.9         | 0.9        | 0.9         |

| CGBO      | 2.00e-10                                                                             | 2.00e-10  | 3.80e-10  | 3.80e-10    | 3.80e-10   | 3.50e-10    |

| CGDO      | 4.00e-10                                                                             | 4.00e-10  | 4.00e-10  | 3.50e-10    | 3.67e-10   | 3.43e-10    |

| CGSO      | 4.00e-10                                                                             | 4.00e-10  | 4.00e-10  | 3.50e-10    | 3.67e-10   | 3.43e-10    |

<sup>1</sup> In PSpice, we have created MOSFET parts corresponding to the above models. Readers can find these parts in the SEDRA.olb library, which is available online at www.oup.com/us/sedrasmith. The NMOS and PMOS parts for the 0.5-µm CMOS technology are labeled NMOS0P5\_BODY and PMOS0P5\_BODY, respectively. The NMOS and PMOS parts for the 5-µm CMOS technology are labeled NMOS5P0\_BODY and PMOS5P0\_BODY, respectively. Furthermore, parts NMOS5P0 and PMOS5P0 are created to correspond to, respectively, part NMOS0P5\_BODY with its body connected to net 0 and part PMOS0P5\_BODY with its body connected to net  $V_{DD}$ .

and

$$PD = PS = 2 \times 2.75 L_{min} + W$$

(B.13)

Unless otherwise specified, we will use Eqs. (B.12) and (B.13) to estimate the dimensions of the drain/source regions in our examples.

Finally, we note that SPICE computes the values for the parameters of the MOSFET small-signal model based on the dc operating point (bias point). These are then used by SPICE to perform the small-signal analysis (ac, or hand, analysis).

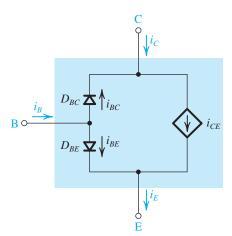

#### **B.1.5 The BJT Model**

SPICE uses a general form of the BJT model that we discussed in Chapter 6 (Fig. 6.5). Known as the transport form of the Ebers-Moll model, it is shown in Fig. B.5. Here, the currents of the base–emitter diode  $(D_{\it BE})$  and the base–collector diode  $(D_{\it BC})$  are given, respectively, by

$$i_{BE} = \frac{I_S}{\beta_F} \left( e^{v_{BE}/n_F V_T} - 1 \right)$$

(B.14)

and

$$i_{BC} = \frac{I_S}{\beta_R} \left( e^{v_{BC}/n_R V_T} - 1 \right)$$

(B.15)

where  $n_F$  and  $n_R$  are the emission coefficients of the BEJ and BCJ, respectively. These coefficients are generalizations of the constant n of the pn-junction diode (Fig. B.3).

**Figure B.5** The transport form of the Ebers–Moll model for an *npn* BJT.

(We have so far assumed  $n_F = n_R = 1$ ). The parameters  $\beta_F$  and  $\beta_R$  are, respectively, the forward and reverse  $\beta$  of the BJT. The reverse  $\beta$  is the current gain obtained when the collector and emitter are interchanged and is much smaller than the forward  $\beta$ . In fact,  $\beta_R \ll 1$ . The controlled current-source  $i_{CE}$  in the transport model is defined as

$$i_{CE} = I_S \left( e^{U_{BE}/n_F V_T} - e^{U_{BC}/n_R V_T} \right)$$

(B.16)

Observe that  $i_{CE}$  represents the current component of  $i_C$  and  $i_E$  that arises as a result of the minority carrier diffusion across the base, or **carrier transport** across the base (hence the name transport model).

The transport model can account for the Early effect in a forward-biased BJT by including the factor  $(1 - v_{BC}/V_A)$  in the expression for the transport current  $i_{CE}$  as follows:

$$i_{CE} = I_S \left( e^{v_{BE}/n_F V_T} - e^{v_{BC}/n_R V_T} \right) \left( 1 - \frac{v_{BC}}{V_A} \right)$$

(B.17)

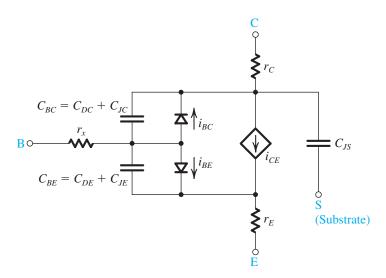

Figure B.6 shows the model used in SPICE. Here, resistors  $r_x$ ,  $r_E$ , and  $r_C$  are added to represent the ohmic resistance of, respectively, the base, emitter, and collector regions. The dynamic operation of the BJT is modeled by two nonlinear capacitors,  $C_{BC}$  and  $C_{BE}$ . Each of these capacitors generally includes a diffusion component (i.e.,  $C_{DC}$  and  $C_{DE}$ ) and a depletion or junction component (i.e.,  $C_{JC}$  and  $C_{JE}$ ) to account for the charge-storage effects within the BJT (as described in Section 10.6.2). Furthermore, the BJT model includes a depletion junction capacitance  $C_{JS}$  to account for the collector–substrate junction in integrated-circuit BJTs, where a reverse-biased pn junction is formed between the collector and the substrate (which is common to all components of the IC).

For small-signal (ac) analysis, the SPICE BJT model is equivalent to the hybrid- $\pi$  model of Fig. 7.24, but augmented with  $r_E$ ,  $r_C$ , and (for IC BJTs)  $C_{JS}$ . Furthermore, the model includes a large resistance  $r_\mu$  between the base and collector (in parallel with  $C_\mu$ ) to account for the dependence of  $i_1$  on  $v_{CB}$ . The resistance  $r_\mu$  is very large, typically greater than  $10\beta r_o$ .

Although Fig. B.5 shows the SPICE model for the *npn* BJT, the corresponding model for the *pnp* BJT can be obtained by reversing the direction of the currents and the polarity of the diodes and terminal voltages.

**Figure B.6** The SPICE large-signal model for an *npn* BJT.

The SPICE Gummel-Poon Model of the BJT The BJT model described above lacks a representation of some second-order effects present in actual devices. One of the most important such effects is the variation of the current gains,  $\beta_F$  and  $\beta_R$ , with the current  $i_C$ . The Ebers-Moll model assumes  $\beta_F$  and  $\beta_R$  to be constant, thereby neglecting their current dependence (as depicted in Fig. 6.19). To account for this, and other second-order effects, SPICE uses a more accurate, yet more complex, BJT model called the Gummel-Poon model (named after H. K. Gummel and H. C. Poon, two pioneers in this field). This model is based on the relationship between the electrical terminal characteristics of a BJT and its base charge. It is beyond the scope of this book to delve into the model details. However, it is important for the reader to be aware of the existence of such a model.

In SPICE, the Gummel-Poon model automatically simplifies to the Ebers-Moll model when certain model parameters are not specified. Consequently, the BJT model to be used by SPICE need not be explicitly specified by the user (unlike the MOSFET case in which the model is specified by the LEVEL parameter). For discrete BJTs, the values of the SPICE model parameters can be determined from the data specified on the BJT data sheets, supplemented (if needed) by key measurements. For instance, in Example PS5.6.1, we will use the Q2N3904 npn BJT (from Fairchild Semiconductor) whose SPICE model is available in PSpice. In fact, the PSpice and Multisim library already includes the SPICE model parameters for many of the commercially available discrete BJTs. For IC BJTs, the values of the SPICE model parameters are determined by the IC manufacturer (using both measurements on the fabricated devices and knowledge of the details of the fabrication process) and are provided to the IC designers.

Table B.4 provides a listing of some of the BJT model parameters used in SPICE. The reader should be already familiar with these parameters. In the absence of a user-specified value for a particular parameter, SPICE uses a default value that typically results in the corresponding effect being ignored. For example, if no value is specified for the forward Early voltage (VAF), SPICE assumes that  $VAF = \infty$  and does not account for the Early effect. Although ignoring VAF can be a serious issue in some circuits, the same is not true, for example, for the value of the reverse Early voltage (VAR).

The BJT Model Parameters BF and BR in SPICE Before leaving the SPICE model, a comment on  $\beta$  is in order. SPICE interprets the user-specified model parameters BF and BR as the *ideal maximum* values of the forward and reverse dc current gains, respectively, versus the operating current. These parameters are not equal to the constant-current-independent parameters  $\beta_F(\beta_{dc})$  and  $\beta_R$  used in the Ebers-Moll model for the forward and reverse dc current gains of the BJT. SPICE uses a current-dependent model for  $\beta_F$  and  $\beta_R$ , and the user can specify other parameters (not shown in Table B.4) for this model. Only when such parameters are not specified, and the Early effect is neglected, will SPICE assume that  $\beta_F$  and  $\beta_R$  are constant and equal to BF and BR, respectively. Furthermore, SPICE computes values for both  $\beta_{dc}$  and  $\beta_{ac}$ , the two parameters that we generally assume to be approximately equal. SPICE then uses  $\beta_{ac}$  to perform small-signal (ac) analysis.

| Table B.4 | Parameters of the SP          | ICE BJT Model (Partial Listing)                                |       |

|-----------|-------------------------------|----------------------------------------------------------------|-------|

| SPICE     | Book                          |                                                                |       |

| Parameter | Symbol                        | Description                                                    | Units |

| IS        | $I_S$                         | Saturation current                                             | A     |

| BF        | $oldsymbol{eta}_F$            | Ideal maximum forward current gain                             |       |

| BR        | $eta_R$                       | Ideal maximum reverse current gain                             |       |

| NF        | $n_F$                         | Forward current emission coefficient                           |       |

| NR        | $n_R$                         | Reverse current emission coefficient                           |       |

| VAF       | $V_A$                         | Forward Early voltage                                          | V     |

| VAR       |                               | Reverse Early voltage                                          | V     |

| RB        | $r_x$                         | Zero-bias base ohmic resistance                                | Ω     |

| RC        | $r_C$                         | Collector ohmic resistance                                     | Ω     |

| RE        | $r_E$                         | Emitter ohmic resistance                                       | Ω     |

| TF        | $	au_F$                       | Ideal forward transit time                                     | S     |

| TR        | $\tau_{\scriptscriptstyle R}$ | Ideal reverse transit time                                     | S     |

| CJC       | $C_{\mu0}$                    | Zero-bias base–collector depletion (junction) capacitance      | F     |

| MJC       | $m_{ m BCJ}$                  | Base-collector grading coefficient                             |       |

| VJC       | $V_{0c}$                      | Base-collector built-in potential                              | V     |

| CJE       | $C_{je0}$                     | Zero-bias base-emitter depletion (junction) capacitance        | F     |

| MJE       | $m_{ m BEJ}$                  | Base-emitter grading coefficient                               |       |

| VJE       | $V_{0e}$                      | Base-emitter built-in potential                                | V     |

| CJS       |                               | Zero-bias collector–substrate depletion (junction) capacitance | F     |

| MJS       |                               | Collector-substrate grading coefficient                        |       |

| VJS       |                               | Collector–substrate built-in potential                         | V     |

# **B.2 PSpice Examples**

# **Example PS.2.1**

#### **Performance of a Noninverting Amplifier**

Consider an op amp with a differential input resistance of 2 M $\Omega$ , an input offset voltage of 1 mV, a dc gain of 100 dB, and an output resistance of 75  $\Omega$ . Assume the op amp is internally compensated and has an STC frequency response with a gain-bandwidth product of 1 MHz.

- (a) Create a subcircuit model for this op amp in PSpice.

- (b) Using this subcircuit, simulate the closed-loop noninverting amplifier in Fig. 2.12 with resistors  $R_1 =$ 1 k $\Omega$  and  $R_2 = 100 \text{ k}\Omega$  to find:

- (i) Its 3-dB bandwidth  $f_{3dB}$ .

- (ii) Its output offset voltage  $V_{OSout}$ .

- (iii) Its input resistance  $R_{in}$ .

- (iv) Its output resistance  $R_{out}$ .

- (c) Simulate the step response of the closed-loop amplifier, and measure its rise time  $t_c$ . Verify that this time agrees with the 3-dB frequency measured above.

#### Solution

To model the op amp in PSpice, we use the equivalent circuit in Fig. B.2, but with  $R_{id} = 2 \text{ M}\Omega$ ,  $R_{icm} = \infty$ (open circuit),  $I_{B1} = I_{B2} = 0$  (open circuit),  $V_{OS} = 1$  mV,  $A_{0d} = 10^5$  V/V,  $A_{0cm} = 0$  (short circuit), and  $R_o = 75 \Omega$ . Furthermore, we set  $C_b = 1 \mu F$  and  $R_b = 15.915 k\Omega$  to achieve an  $f_t = 1 MHz$ .

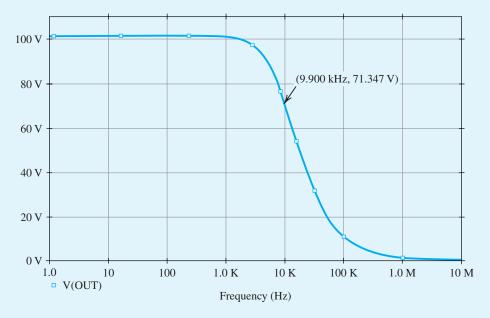

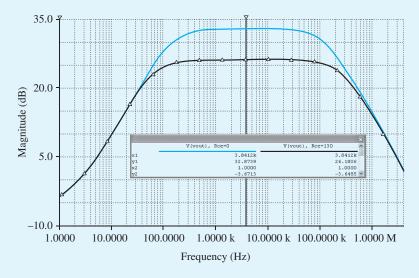

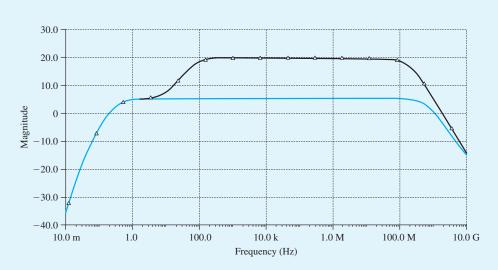

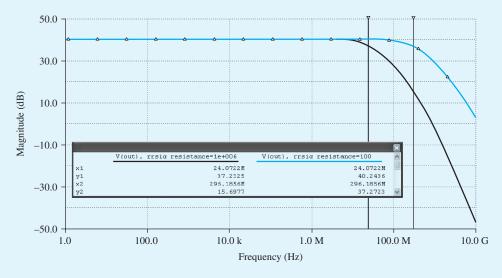

To measure the 3-dB frequency of the closed-loop amplifier, we apply a 1-V ac voltage at its input, perform an ac-analysis simulation in PSpice, and plot its output versus frequency. The output voltage, plotted in Fig. B.7, corresponds to the gain of the amplifier because we chose an input voltage of 1 V.

**Figure B.7** Frequency response of the closed-loop amplifier in Example PS.2.1.

#### Example PS.2.1 continued

Thus, from Fig. B.7, the closed-loop amplifier has a dc gain of  $G_0 = 100.9 \text{ V/V}$ , and the frequency at which its gain drops to  $G_0/\sqrt{2} = 71.35 \text{ V/V}$  is  $f_{3dB} = 9.9 \text{ kHz}$ , which agrees with Eq. (B.7).

The input resistance R<sub>in</sub> corresponds to the reciprocal of the current drawn out of the 1-V ac voltage source used in the above ac-analysis simulation at 0.1 Hz. (Theoretically,  $R_{\rm in}$  is the small-signal input resistance at dc. However, ac-analysis simulations must start at frequencies greater than zero, so we use 0.1 Hz to approximate the dc point.) Accordingly,  $R_{in}$  is found to be 2 G $\Omega$ .

To measure  $R_{out}$ , we short-circuit the amplifier input to ground, inject a 1-A ac current at its output, and perform an ac-analysis simulation.  $R_{out}$  corresponds to the amplifier output voltage at 0.1 Hz and is found to be 76 m $\Omega$ . Although an ac test voltage source could equally well have been used to measure the output resistance in this case, it is a good practice to attach a current source rather than a voltage source between the output and ground. This is because an ac current source appears as an open circuit when the simulator computes the dc bias point of the circuit while an ac voltage source appears as a short circuit, which can erroneously force the dc output voltage to zero. For similar reasons, an ac test voltage source should be attached in series with the biasing dc voltage source for measuring the input resistance of a voltage amplifier.

A careful look at  $R_{\rm in}$  and  $R_{\rm out}$  of the closed-loop amplifier reveals that their values have, respectively, increased and decreased by a factor of about 1000, relative to the corresponding resistances of the op amp. Such a large input resistance and small output resistance are indeed desirable characteristics for a voltage amplifier. This improvement in the small-signal resistances of the closed-loop amplifier is a direct consequence of applying negative feedback (through resistors  $R_1$  and  $R_2$ ) around the open-loop op amp. We will study negative feedback in Chapter 11, where we will also learn how the improvement factor (1000 in this case) corresponds to the ratio of the open-loop op-amp gain  $(10^5)$  to the closed-loop amplifier gain (100).

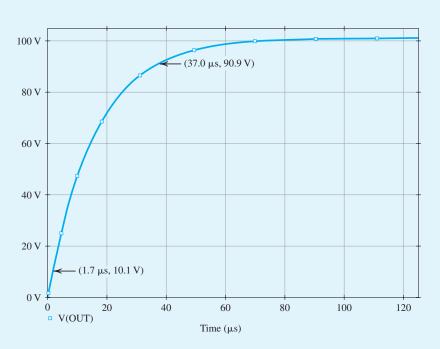

From Eqs. (2.55) and (2.53), the closed-loop amplifier has an STC low-pass response given by

$$\frac{V_o(s)}{V_i(s)} = \frac{G_0}{1 + \frac{s}{2\pi f_{s,ip}}}$$

As described in Appendix E, the response of such an amplifier to an input step of height  $V_{\text{step}}$  is given by

$$v_O(t) = V_{\text{final}} \left( 1 - e^{-t/\tau} \right) \tag{B.18}$$

where  $V_{\text{final}} = G_0 V_{\text{step}}$  is the final output-voltage value (i.e., the voltage value toward which the output is heading) and  $\tau = 1/(2\pi f_{3dB})$  is the time constant of the amplifier. If we define  $t_{10\%}$  and  $t_{90\%}$  to be the time it takes for the output waveform to rise to, respectively, 10% and 90% of  $V_{\text{final}}$ , then from Eq. (B.18),  $t_{10\%}$  $\simeq 0.1\tau$  and  $t_{90\%} \simeq 2.3\tau$ . Therefore, the rise time  $t_r$  of the amplifier can be expressed as

$$t_r = t_{90\%} - t_{10\%} = 2.2\tau = \frac{2.2}{2\pi f_{3dB}}$$

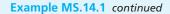

Therefore, if  $f_{3dB} = 9.9 \,\mathrm{kHz}$ , then  $t_r = 35.4 \,\mathrm{\mu s}$ . To simulate the step response of the closed-loop amplifier, we apply a step voltage at its input, using a piecewise-linear (PWL) source (with a very short rise time); then perform a transient-analysis simulation, and measure the voltage at the output versus time. In our simulation, we applied a 1-V step input, plotted the output waveform in Fig. B.8, and measured  $t_r$  to be 35.3  $\mu$ s.

The linear macromodels in Figs. B.1 and B.2 assume that the op-amp circuit is operating in its linear range; they do not account for its nonideal performance when large signals are present at the output. Therefore, nonlinear effects, such as output saturation and slew rate, are not modeled. This is why, in the step response of Fig. B.8, we could see an output voltage of 100 V when we applied a 1-V step input. However, IC op amps are not capable of producing such large output voltages. Hence, a designer must be very careful when using these models.

**Figure B.8** Step response of the closed-loop amplifier in Example PS.2.1.

It is important to point out that we also saw output voltages of 100 V or so in the ac analysis of Fig. B.7, where for convenience we applied a 1-V ac input to measure the gain of the closed-loop amplifier. So, would we see such large output voltages if the op-amp macromodel accounted for nonlinear effects (particularly output saturation)? The answer is yes, because in an ac analysis PSpice uses a linear model for nonlinear devices with the linear-model parameters evaluated at a bias point. Thus, we must keep in mind that the voltage magnitudes encountered in an ac analysis may not be realistic. In this case, the voltage and current ratios (e.g., the output-to-input voltage ratio as a measure of voltage gain) are of importance to the designer.

# **Example PS.2.2**

#### Characteristics of the 741 Op Amp

Consider the µA741 op amp whose macromodel is available in PSpice. Use PSpice to plot the open-loop gain and hence determine f<sub>t</sub>. Also, investigate the SR limitation and the output saturation of this op amp.

#### Solution

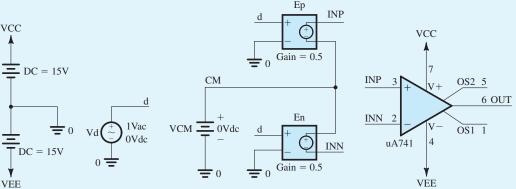

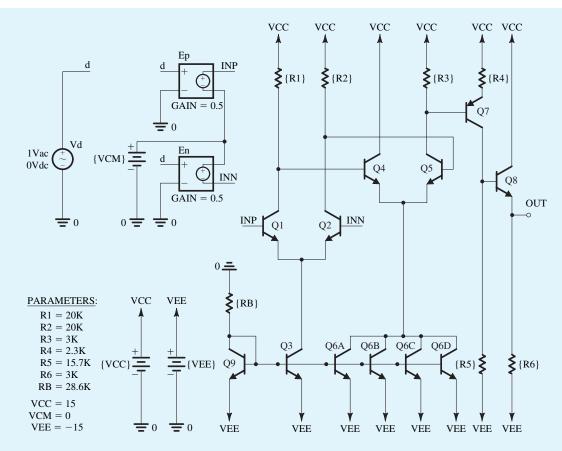

Figure B.9 shows the schematic capture used to simulate the frequency response of the  $\mu$ A741 op amp. The μA741 part has seven terminals. Terminals 7 and 4 are, respectively, the positive and negative

<sup>&</sup>lt;sup>1</sup>The reader is reminded that the schematic capture diagram and the corresponding PSpice simulation files of all SPICE examples in this book can be found on the text's website (www.oup.com/us/sedrasmith).

# Example PS.2.2 continued

Figure B.9 Simulating the frequency response of the μA741 op-amp in Example PS.2.2.

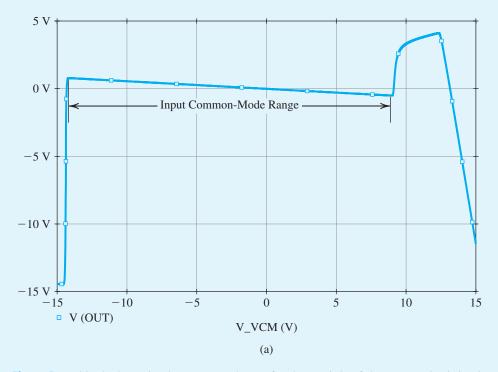

dc power-supply terminals of the op amp. The 741-type op amps are typically operated from  $\pm 15$ -V power supplies; therefore we connected the dc voltage sources  $V_{CC} = +15 \text{ V}$  and  $V_{EE} = -15 \text{ V}$  to terminals 7 and 4, respectively. Terminals 3 and 2 of the µA741 part correspond to the positive and negative input terminals, respectively, of the op amp. In general, as outlined in Section 2.1.3, the op-amp input signals are expressed as

$$v_{\mathit{INP}} = V_{\mathit{CM}} + \frac{V_{\mathit{d}}}{2}$$

$$v_{\mathit{INN}} = V_{\mathit{CM}} - \frac{V_{\mathit{d}}}{2}$$

where  $v_{INP}$  and  $v_{INN}$  are the signals at, respectively, the positive- and negative-input terminals of the op amp with  $V_{CM}$  being the common-mode input signal (which sets the dc bias voltage at the op-amp input terminals) and  $V_d$  being the differential input signal to be amplified. The dc voltage source  $V_{CM}$  in Fig. B.9 is used to set the common-mode input voltage. Typically,  $V_{CM}$  is set to the average of the dc power-supply voltages  $V_{CC}$  and  $V_{EE}$  to maximize the available input signal swing. Hence, we set  $V_{CM} = 0$ . The voltage source  $V_d$  in Fig. B.9 is used to generate the differential input signal  $V_d$ . This signal is applied differentially to the op-amp input terminals using the voltage-controlled voltage sources  $E_n$  and  $E_n$ , whose gain constants are set to 0.5.

Terminals 1 and 5 of part  $\mu$  A741 are the offset-nulling terminals of the op amp (as depicted in Fig. 2.36). However, a check of the PSpice netlist of this part (by selecting Edit → PSpice Model, in the Capture menus), reveals that these terminals are floating; therefore the offset-nulling characteristic of the op amp is not incorporated in this macromodel.

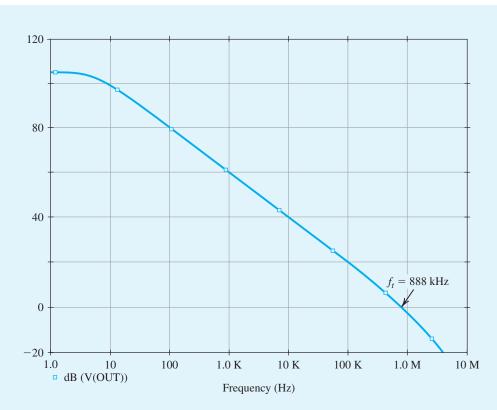

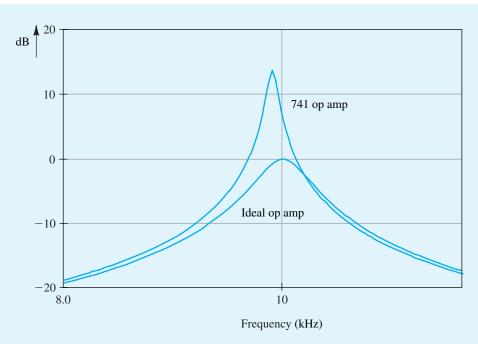

To measure  $f_t$  of the op amp, we set the voltage of source  $V_d$  to be 1-V ac, perform an ac-analysis simulation in PSpice, and plot the output voltage versus frequency as shown in Fig. B.10. Accordingly, the frequency at which the op-amp voltage gain drops to 0 dB is  $f_t = 0.9$  MHz (which is close to the 1-MHz value reported in the data sheets for 741-type op amps).

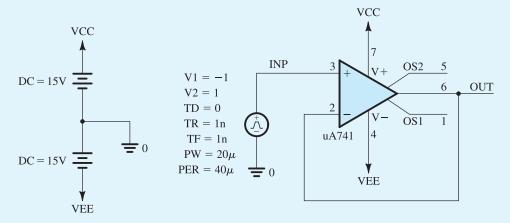

To determine the slew rate of the  $\mu$ A741 op amp, we connect the op amp in a unity-gain configuration, as shown in Fig. B.11, apply a large pulse signal at the input with very short rise and fall times to

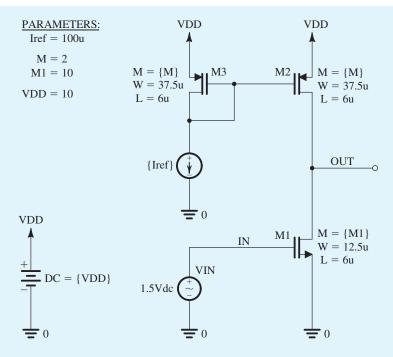

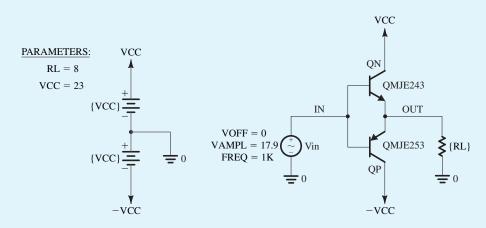

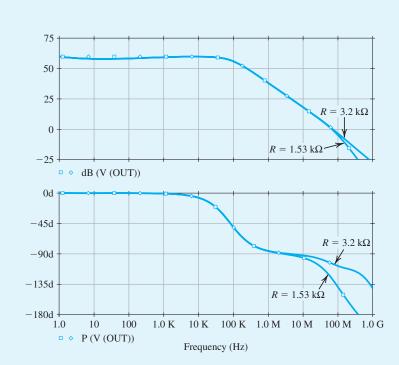

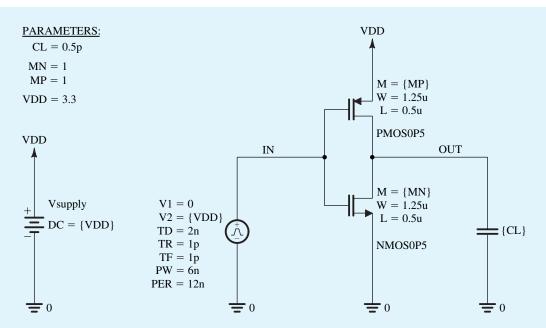

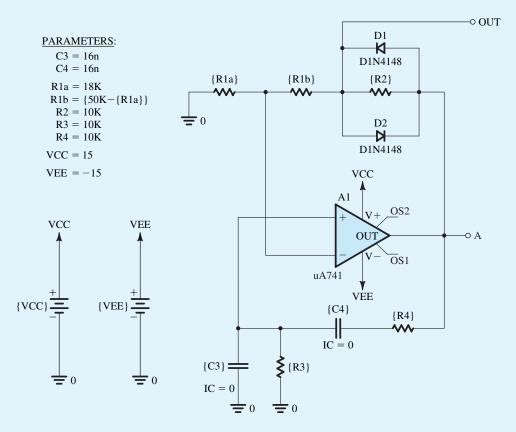

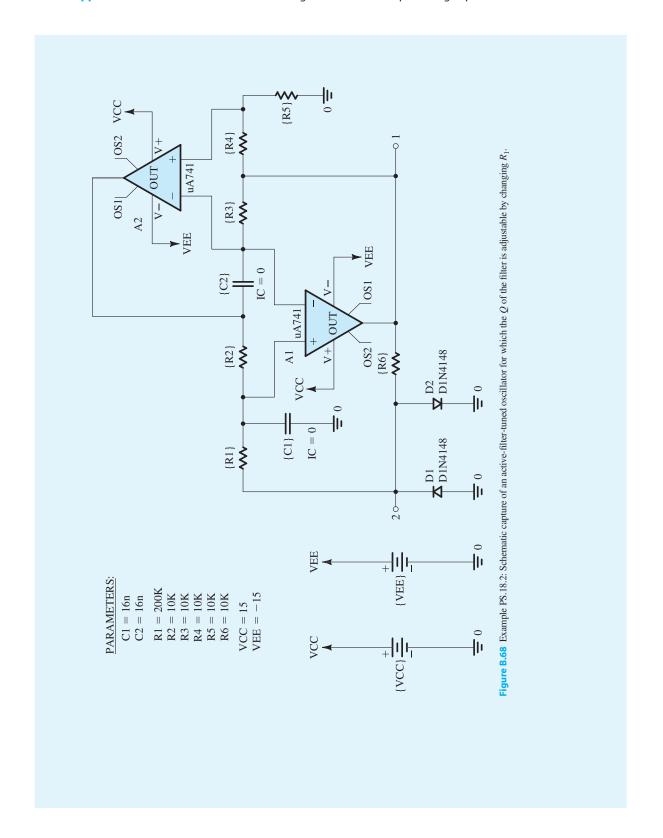

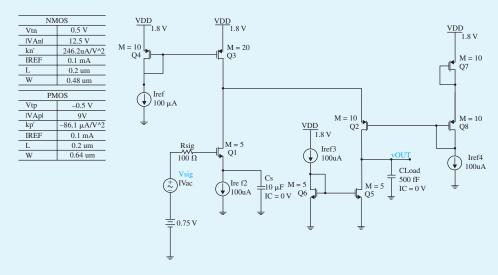

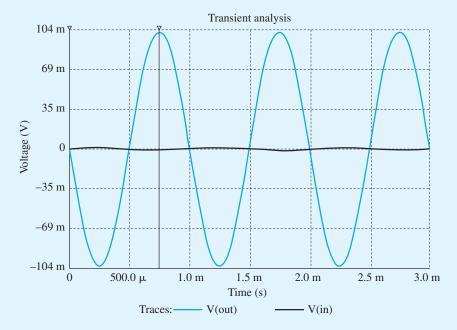

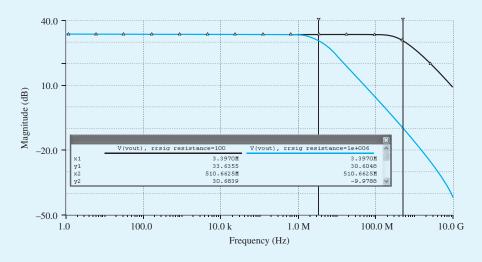

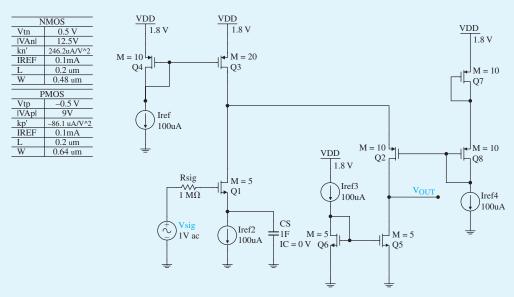

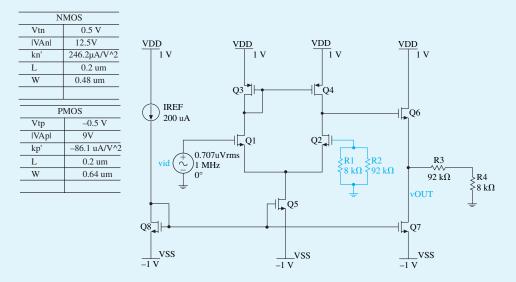

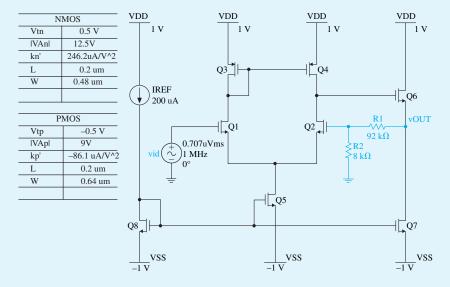

In these schematics (as shown in Fig. B.13), we use variable parameters to enter the values of the various circuit components. This allow one to investigate the effect of changing component values by simply changing the corresponding parameter values.

**Figure B.10** Frequency response of the μA741 op amp in Example PS.2.2.

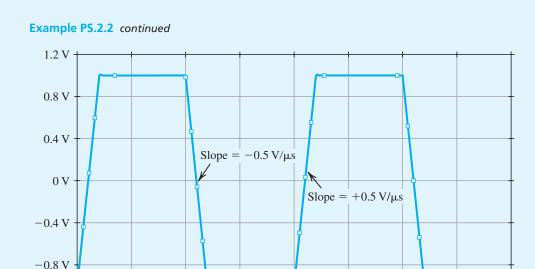

cause slew-rate limiting at the output, perform a transient-analysis simulation in PSpice, and plot the output voltage as shown in Fig. B.12. The slope of the slew-rate limited output waveform corresponds to the slew-rate of the op amp and is found to be  $SR = 0.5 \text{ V/}\mu\text{s}$  (which agrees with the value specified in the data sheets for 741-type op amps).

Figure B.11 Circuit for determining the slew rate of the  $\mu$ A741 op amp in Example PS.5.2.2.

Figure B.12 Square-wave response of the  $\mu$ A741 op amp connected in the unity-gain configuration shown in Fig. B.11.

40

Time (µs)

50

60

70

80

To determine the maximum output voltage of the  $\mu$ A741 op amp, we set the dc voltage of the differential voltage source  $V_d$  in Fig. B.9 to a large value, say +1 V, and perform a bias-point simulation in PSpice. The corresponding dc output voltage is the positive-output saturation voltage of the op amp. We repeat the simulation with the dc differential input voltage set to -1 V to find the negative-output saturation voltage. Accordingly, we find that the  $\mu$ A741 op amp has a maximum output voltage  $V_{omax} = 14.8 \text{ V}$ .

# **Example PS.4.1**

-1.2 V

#### **Design of a DC Power Supply**

10

□ V(OUT)

20

30

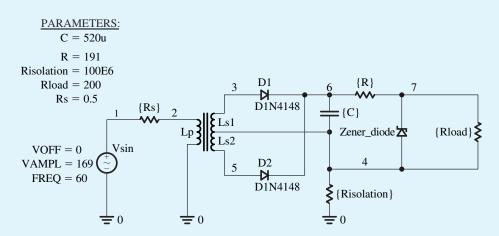

In this example, we will design a dc power supply using the rectifier circuit whose capture schematic is shown in Fig. B.13. This circuit consists of a full-wave diode rectifier, a filter capacitor, and a zener voltage regulator. The only perhaps puzzling component is the  $R_{\rm isolation}$ , the 100-M $\Omega$  resistor between the secondary winding of the transformer and ground. This resistor is included to provide dc continuity and thus "keep SPICE happy"; it has little effect on circuit operation.

Let it be required that the power supply (in Fig. B.13) provide a nominal dc voltage of 5 V and be able to supply a load current  $I_{\rm load}$  as large as 25 mA; that is,  $R_{\rm load}$  can be as low as 200  $\Omega$ . The power supply is fed from a 120-V (rms) 60-Hz ac line. Note that in the PSpice schematic (Fig. B.13), we use a sinusoidal voltage source with a 169-V peak amplitude to represent the 120-V rms supply (as 120-V rms = 169-V peak). Assume the availability of a 5.1-V zener diode having  $r_z = 10 \Omega$  at  $I_Z = 20$  mA (and thus  $V_{z0} = 4.9$  V), and that the required minimum current through the zener diode is  $I_{Zmin} = 5$  mA.

**Figure B.13** Schematic capture of the 5-V dc power supply in Example PS.4.1.

An approximate first-cut design can be obtained as follows: The 120-V (rms) supply is stepped down to provide 12-V (peak) sinusoids across each of the secondary windings using a 14:1 turns ratio for the center-tapped transformer. The choice of 12 V is a reasonable compromise between the need to allow for sufficient voltage (above the 5-V output) to operate the rectifier and the regulator, while keeping the PIV ratings of the diodes reasonably low. To determine a value for R, we can use the following expression:

$$R = \frac{V_{C\min} - V_{Z0} - r_z I_{Z\min}}{I_{Z\min} + I_{L\max}}$$

where an estimate for  $V_{Cmin}$ , the minimum voltage across the capacitor, can be obtained by subtracting a diode drop (say, 0.8 V) from 12 V and allowing for a ripple voltage across the capacitor of, say,  $V_r = 0.5$  V. Thus,  $V_{S \text{ min}} = 10.7 \text{ V}$ . Furthermore, we note that  $I_{L \text{ max}} = 25 \text{ mA}$  and  $I_{Z \text{min}} = 5 \text{ mA}$ , and that  $V_Z 0 = 4.9 \text{ V}$  and  $r_z = 10 \Omega$ . The result is that  $R = 191 \Omega$ .

Next, we determine C using a restatement of Eq. (4.33) with  $V_n/R$  replaced by the current through the 191- $\Omega$  resistor. This current can be estimated by noting that the voltage across C varies from 10.7 V to 11.2 V, and thus has an average value of 10.95 V. Furthermore, the desired voltage across the zener is 5 V. The result is  $C = 520 \,\mu\text{F}$ .

Now, with an approximate design in hand, we can proceed with the SPICE simulation. For the zener diode, we use the model of Fig. B.4, and assume (arbitrarily) that  $D_1$  has  $I_2 = 100$  pA and n = 0.01 while  $D_2$ has  $I_s = 100 \text{ pA}$  and n = 1.7. For the rectifier diodes, we use the commercially available 1N4148 type<sup>2</sup> (with  $I_S = 2.682 \text{ nA}, n = 1.836, R_S = 0.5664 \Omega, V_0 = 0.5 \text{ V}, C_{i0} = 4 \text{ pF}, m = 0.333, \tau_T = 11.54 \text{ ns}, V_{ZK} = 100 \text{ V},$

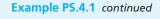

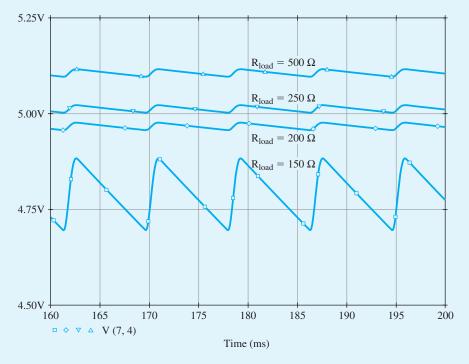

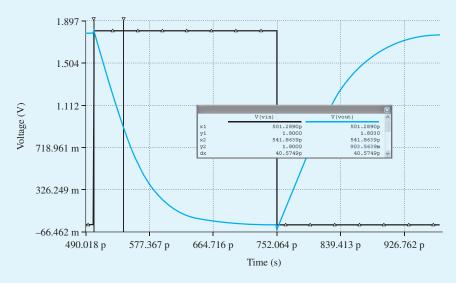

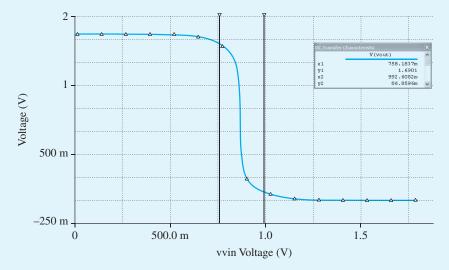

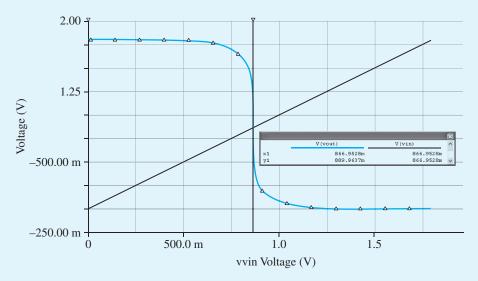

In PSpice, we perform a transient analysis and plot the waveforms of both the voltage  $v_c$  across the smoothing capacitor C and the voltage  $v_0$  across the load resistor  $R_{\text{load}}$ . The simulation results for  $R_{\rm load} = 200 \,\Omega$  ( $I_{\rm load} \simeq 25$  mA) are presented in Fig. B.14. Observe that  $v_C$  has an average of 10.85 V and a ripple of  $\pm$  0.21 V. Thus,  $V_1 = 0.42$  V, which is close to the 0.5-V value that we would expect from the chosen value of C. The output voltage  $v_0$  is very close to the required 5 V, with  $v_0$  varying between 4.957 V and 4.977 V for a ripple of only 20 mV. The variations of  $v_0$  with  $R_{load}$  are illustrated in Fig. B.15

<sup>&</sup>lt;sup>2</sup>The 1N4148 model is included in the evaluation (EVAL) library of PSpice.

Figure B.14 The voltage  $v_{\hat{o}}$  across the smoothing capacitor C and the voltage  $v_{\hat{o}}$  across the load resistor  $R_{\text{load}} = 200 \,\Omega$  in the 5-V power supply of Example PS.4.1.

**Figure B.15** The output-voltage waveform from the 5-V power supply (in Example PS.4.1) for various load resistances:  $R_{\text{load}} = 500 \,\Omega$ ,  $250 \,\Omega$ ,  $200 \,\Omega$ , and  $150 \,\Omega$ . The voltage regulation is lost at a load resistance of  $150 \,\Omega$ .

for  $R_{\rm load}=500~\Omega,\,250~\Omega,\,200~\Omega,$  and  $150~\Omega.$  Accordingly,  $v_o$  remains close to the nominal value of 5 V for  $R_{\rm load}$  as low as  $200 \,\Omega(I_{\rm load} \simeq 25 \, {\rm mA})$ . For  $R_{\rm load} = 150 \,\Omega$  (which implies  $I_{\rm load} \simeq 33.3 \, {\rm mA}$ , greater than the maximum designed value), we see a significant drop in  $v_0$  (to about 4.8 V), as well as a large increase in the ripple voltage at the output (to about 190 mV). This is because the zener regulator is no longer operational; the zener has in fact cut off.

We conclude that the design meets the specifications, and we can stop here. Alternatively, we may consider using further runs of PSpice to help with the task of fine-tuning the design. For instance, we could consider what happens if we use a lower value of C, and so on. We can also investigate other properties of the present design (e.g., the maximum current through each diode) and ascertain whether this maximum is within the rating specified for the diode.

#### **EXERCISE**

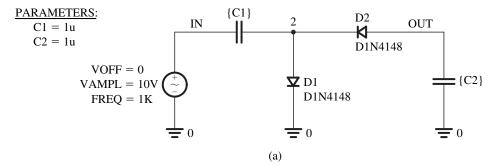

**B.1** Use PSpice to investigate the operation of the voltage doubler whose schematic capture is shown in Fig. B.16(a). Specifically, plot the transient behavior of the voltages  $v_2$  and  $v_{OUT}$  when the input is a sinusoid of 10-V peak and 1-kHz frequency. Assume that the diodes are of the 1N4148 type (with  $I_S = 2.682$  nA, n = 1.836,  $R_S = 0.5664$   $\Omega$ ,  $V_0 = 0.5$  V,  $C_i = 0.5$  V,  $C_i = 0.333$ ,  $\tau_T = 11.54$  ns,  $V_{ZK} = 100 \text{ V}, I_{ZK} = 100 \text{ } \mu\text{A}).$

Ans. The voltage waveforms are shown in Fig. B.16(b).

Figure EB.16 (a) Schematic capture of the voltage-doubler circuit in Exercise B.1. (b) Various voltage waveforms in the voltage-doubler circuit. The top graph displays the input sine-wave voltage signal, the middle graph displays the voltage across diode  $D_1$ , and the bottom graph displays the voltage that appears at the output.

Figure EB.16 continued

# **Example PS.7.1**

#### The CS Amplifier

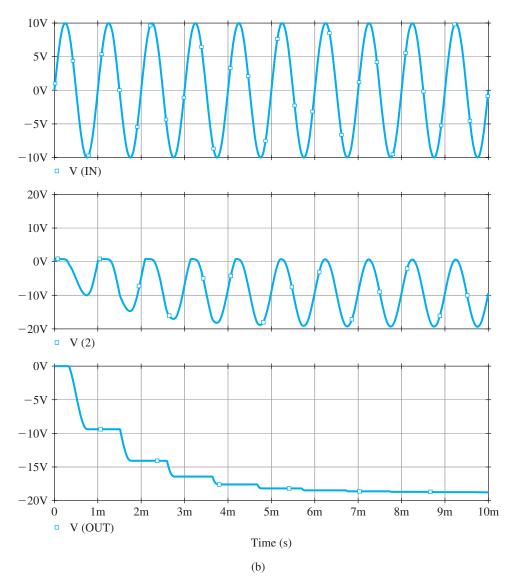

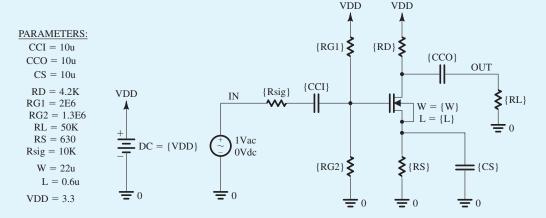

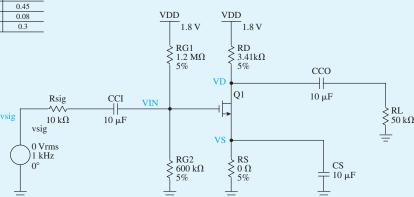

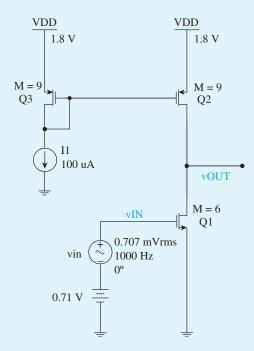

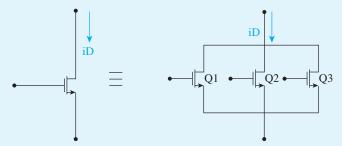

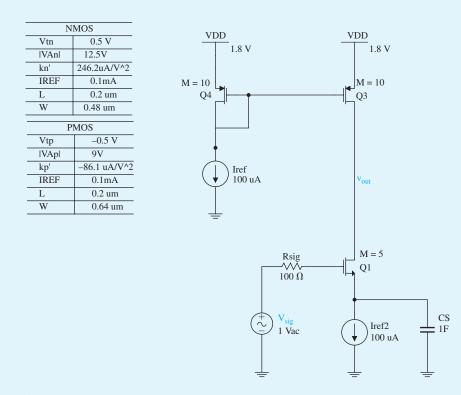

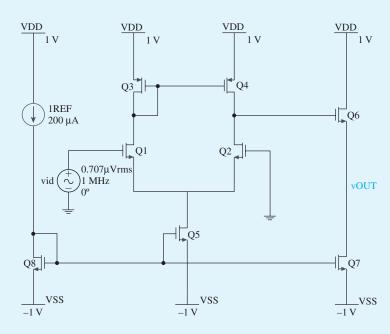

In this example, we will use PSpice to analyze and verify the design of the CS amplifier whose capture schematic is shown in Fig. B.17.3 Observe that the MOSFET has its source and body connected in order to cancel the body effect. We will assume a 0.5-µm CMOS technology for the MOSFET and use the SPICE level-1 model parameters listed in Table B.3. We will also assume a signal-source resistance  $R_{\rm sig}=10~{\rm k}\Omega$ , a load resistance  $R_L = 50 \text{ k}\Omega$ , and bypass and coupling capacitors of 10  $\mu$ F. The targeted specifications for this CS amplifier are a midband gain  $A_M = 10 \text{ V/V}$  and a maximum power consumption P = 1.5 mW. As should always be the case with computer simulation, we will begin with an approximate pencil-and-paper design. We will then use PSpice to fine-tune our design and to investigate the performance of the final design. In this way, maximum advantage and insight can be obtained from simulation.

With a 3.3-V power supply, the drain current of the MOSFET must be limited to  $I_D$  $P/V_{DD} = 1.5 \,\mathrm{mW/3.3~V} = 0.45 \,\mathrm{mA}$  to meet the power consumption specification. Choosing  $V_{OV} = 0.3 \,\mathrm{V}$ (a typical value in low-voltage designs) and  $V_{DS} = V_{DD}/3$  (to achieve a large signal swing at the output), the MOSFET can now be sized as

$$\frac{W}{L_{\text{eff}}} = \frac{I_D}{\frac{1}{2} k'_n V_{OV}^2 \left(1 + \lambda V_{DS}\right)} = \frac{0.45 \times 10^{-3}}{\frac{1}{2} \left(170.1 \times 10^{-6}\right) (0.3)^2 [1 + 0.1(1.1)]} \simeq 53$$

(B.19)

where  $k'_n = \mu_n C_{ox} = 170.1 \,\mu\text{A/V}^2$  (from Table B.3). Here,  $L_{\text{eff}}$  rather than L is used to more accurately compute  $I_D$ . The effect of using  $W_{\rm eff}$  rather than W is much less important because typically  $W\gg W_{\sigma v}$ . Thus, choosing  $L=0.6\,\mu\mathrm{m}$  results in  $L_{\mathrm{eff}}=L-2L_{ov}=0.44\,\mu\mathrm{m}$  and  $W=23.3\,\mu\mathrm{m}$ . Note that we chose L slightly larger than  $L_{\min}$ . This is a common practice in the design of analog ICs to minimize the effects of fabrication nonidealities on the actual value of L. As shown in the text, this is particularly important when

Figure B.17 Schematic capture of the CS amplifier in Example PS.7.1.

<sup>&</sup>lt;sup>3</sup>The reader is reminded that the schematic capture diagrams and the corresponding PSpice simulation files of all SPICE examples in this book can be found on the text's website (www.oup.com/us/sedrasmith). In these schematics (as shown in Fig. B.17), we used variable parameters to enter the values of the various circuit components, including the dimensions of the MOSFET. This will allow the reader to investigate the effect of changing component values by simply changing the corresponding parameter values.

#### Example PS.7.1 continued

the circuit performance depends on the matching between the dimensions of two or more MOSFETs (e.g., in the current-mirror circuits studied in Chapter 8).

Next,  $R_D$  is calculated based on the desired voltage gain:

$$|A_v| = g_m(R_D||R_L||r_o) = 10 \text{ V/V} \Rightarrow R_D \simeq 4.2 \text{ k}\Omega$$

(B.20)

where  $g_m = 3.0$  mA/V and  $r_o = 22.2$  k $\Omega$ . Hence, the output bias voltage is  $V_O = V_{DD} - I_D R_D = 1.39$  V. An  $R_S = (V_O - V_{DD}/3)/I_D = 630$   $\Omega$  is needed to bias the MOSFET at a  $V_{DS} = V_{DD}/3$ . Finally, resistors  $R_{G1} = 2$  M $\Omega$  and  $R_{G2} = 1.3$  M $\Omega$  are chosen to set the gate bias voltage at  $V_G = I_D R_S + V_{OV} + V_m \simeq 1.29$  V. Using large values for these gate resistors ensures that both their power consumption and the loading effect on the input signal source are negligible. Note that we neglected the body effect in the expression for  $V_G$  to simplify our hand calculations.

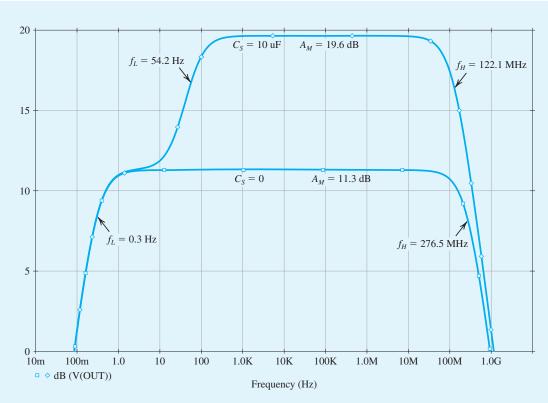

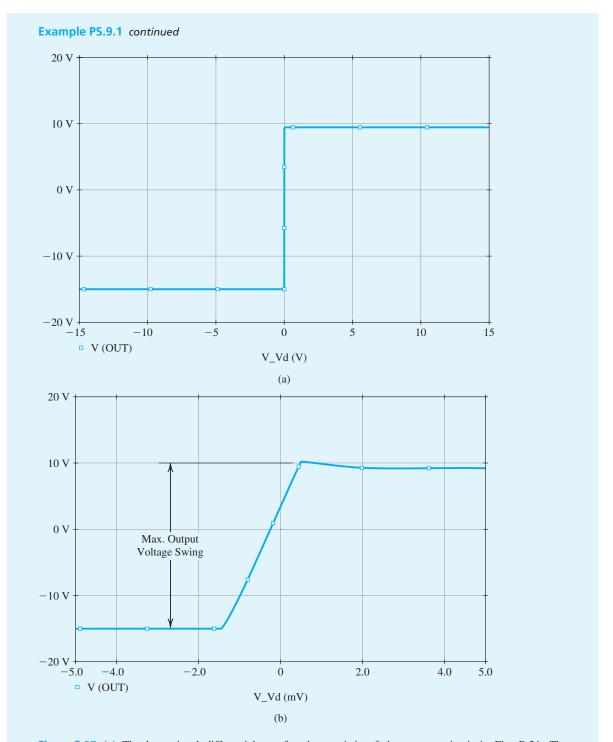

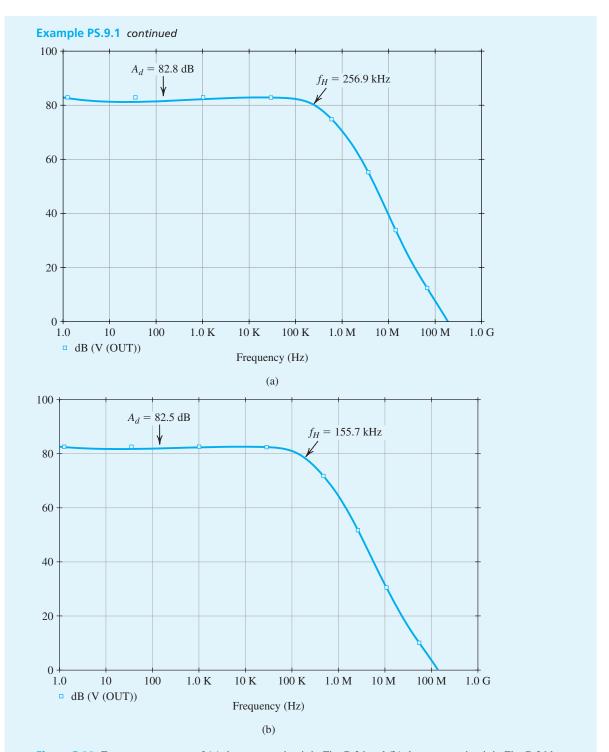

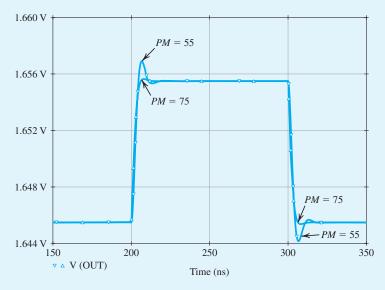

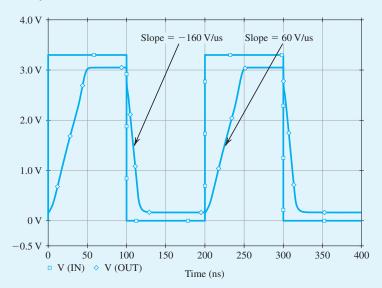

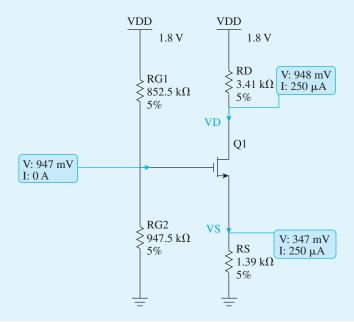

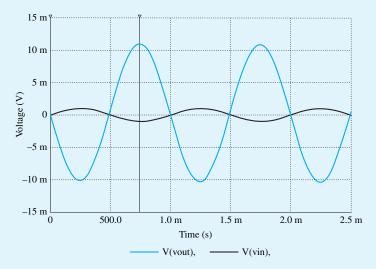

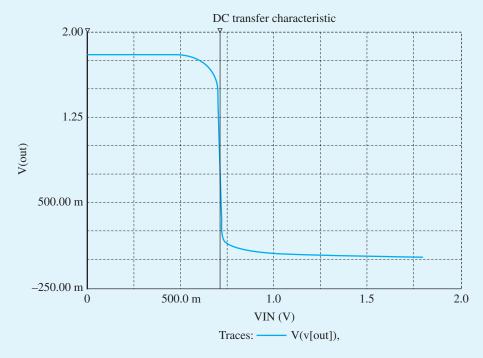

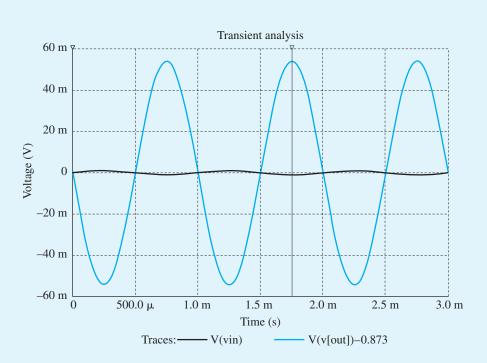

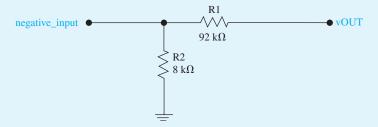

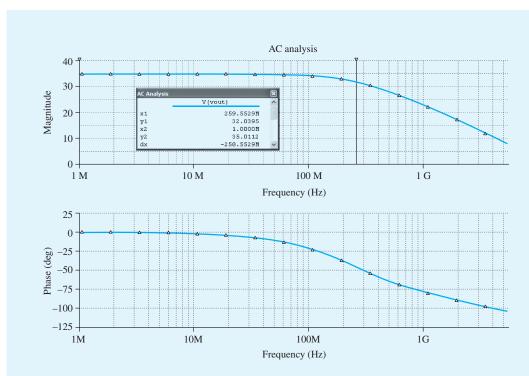

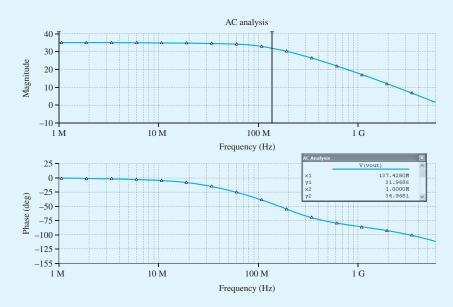

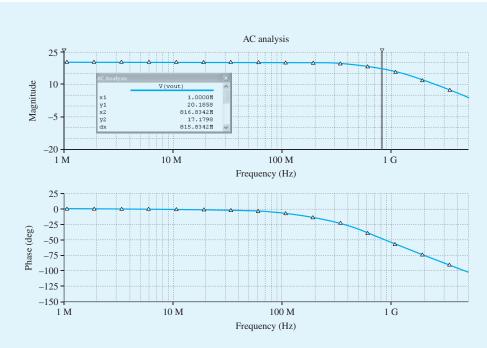

We will now use PSpice to verify our design and investigate the performance of the CS amplifier. We begin by performing a bias-point simulation to verify that the MOSFET is properly biased in the saturation region and that the dc voltages and currents are within the desired specifications. Based on this simulation, we have decreased the value of W to 22  $\mu$ m to limit  $I_D$  to about 0.45 mA. Next, to measure the midband gain  $A_M$  and the 3-dB frequencies  $f_L$  and  $f_H$ , we apply a 1-V ac voltage at the input, perform an ac-analysis simulation, and plot the output-voltage magnitude (in dB) versus frequency as shown in Fig. B.18. This corresponds to the magnitude response of the CS amplifier because we chose a 1-V input signal. Accordingly, the midband gain is  $A_M = 9.55$  V/V and the 3-dB bandwidth is  $BW = f_H - f_L \simeq 122.1$  MHz. Figure B.18 further shows that the gain begins to fall off at about 300 Hz but flattens out again at about 10 Hz. This flattening in the gain at low frequencies is due to a real transmission zero<sup>6</sup> introduced in the transfer function of the amplifier by  $R_s$  together with  $C_s$ . This zero occurs at a frequency  $f_z = 1/(2\pi R_s C_s) = 25.3$  Hz, which is typically between the break frequencies  $f_{P2}$ and  $f_{p_3}$  derived in Section 10.1.1. So, let us now verify this phenomenon by resimulating the CS amplifier with a  $C_s = 0$  (i.e., removing  $C_s$ ) in order to move  $f_Z$  to infinity and remove its effect. The corresponding frequency response is plotted also in Fig. B.18. As expected, with  $C_s = 0$ , we do not observe any flattening in the low-frequency response of the amplifier. However, because the CS amplifier now includes a source resistor  $R_s$ ,  $A_M$  has dropped by a factor of 2.6. This factor is approximately equal to  $(1 + g_m R_s)$ , as expected from our study of the CS amplifier with a source-degeneration resistance in Section 7.3.4. Note that the bandwidth BW has increased by approximately the same factor as the drop in gain  $A_M$ . As we will learn in Chapter 11 when we study negative feedback, the source-degeneration resistor  $R_s$  provides negative feedback, which allows us to trade off gain for wider bandwidth.

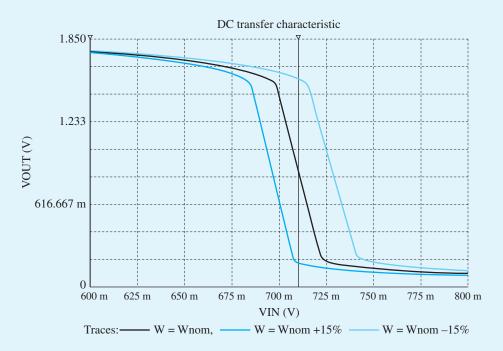

To conclude this example, we will demonstrate the improved bias stability achieved when a source resistor  $R_S$  is used (see the discussion in Section 7.1.1 & 7.1.7). Specifically, we will change (in the MOSFET level-1 model for part NMOS0P5) the value of the zero-bias threshold voltage parameter VTO by  $\pm 15\%$  and perform a bias-point simulation in PSpice. Table B.5 shows the corresponding variations in  $I_D$  and  $V_O$  for the case in which  $R_S = 630 \Omega$ . For the case without source degeneration, we use an  $R_S = 0$  in the

<sup>&</sup>lt;sup>4</sup>No detailed knowledge of frequency-response calculations is required for this example; all that is needed is Section 7.5.3. Nevertheless, after the study of the frequency response of the CS amplifier in Sections 10.1 through 10.3, the reader will benefit by returning to this example and using PSpice to experiment further with the circuit. <sup>5</sup>The reader should not be alarmed about the use of such a large signal amplitude. Recall that in a small-signal (ac) simulation, SPICE first finds the small-signal equivalent circuit at the bias point and then analyzes this linear circuit. Such ac analysis can, of course, be done with any ac signal amplitude. However, a 1-V ac input is convenient to use because the resulting ac output corresponds to the voltage gain of the circuit.

<sup>&</sup>lt;sup>6</sup>Readers who have not yet studied poles and zeros can skip these few sentences.

Figure B.18 Frequency response of the CS amplifier in Example PS.7.1 with  $C_S = 10 \,\mu\text{F}$  and  $C_S = 0$  (i.e.,  $C_S$ removed).

schematic of Fig. B.17. Furthermore, to obtain the same  $I_D$  and  $V_O$  in both cases (for the nominal threshold voltage  $V_{10} = 0.7$  V), we use an  $R_{G2} = 0.88$  M $\Omega$  to reduce  $V_G$  to around  $V_{OV} + V_m = 1$  V. The corresponding variations in the bias point are shown in Table B.5. Accordingly, we see that the source-degeneration resistor makes the bias point of the CS amplifier less sensitive to changes in the threshold voltage. In fact, the reader can show for the values displayed in Table B.5 that the variation in bias current  $(\Delta I/I)$ is reduced by approximately the same factor,  $(1 + g_m R_s)$ . However, unless a large bypass capacitor  $C_s$  is used, this reduced sensitivity comes at the expense of a reduction in the midband gain (as we observed in this example when we simulated the frequency response of the CS amplifier with a  $C_s = 0$ ).

| Table B.5 Va | riations in the Bias Point w | vith the MOSFET Threshol | d Voltage  |                                |

|--------------|------------------------------|--------------------------|------------|--------------------------------|

|              | $R_S = 0$                    | 630 Ω                    | $R_S=0$    |                                |

| $V_{tn0}$    | $I_D$ (mA)                   | $V_{O}\left( V\right)$   | $I_D$ (mA) | $V_{O}\left(\mathbf{V}\right)$ |

| 0.60         | 0.56                         | 0.962                    | 0.71       | 0.33                           |

| 0.7          | 0.46                         | 1.39                     | 0.45       | 1.40                           |

| 0.81         | 0.36                         | 1.81                     | 0.21       | 2.40                           |

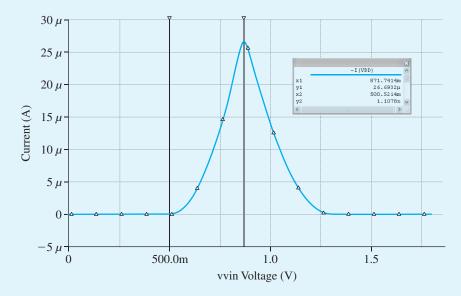

# **Example PS.6.1**

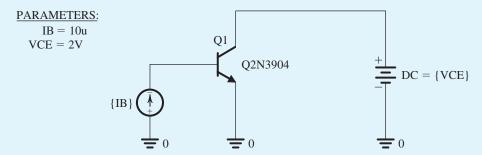

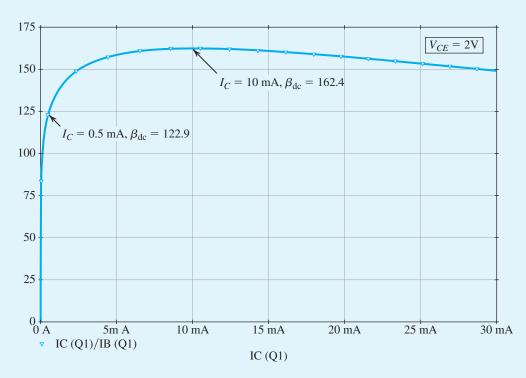

#### Dependence of the BJT $\beta$ on the Bias Current

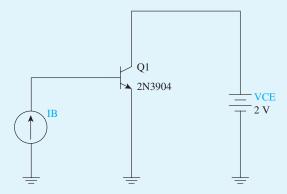

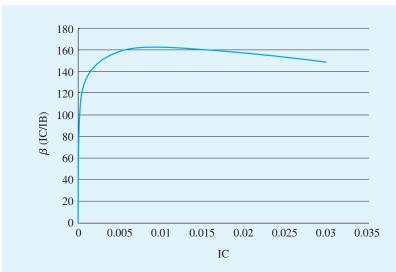

In this example, we use PSpice to simulate the dependence of  $\beta_{\rm dc}$  on the collector bias current for the Q2N3904 discrete BJT (from Fairchild Semiconductor) whose model parameters are listed in Table B.6 and are available in PSpice. As shown in the schematic capture of Fig. B.19, the  $V_{CE}$  of the BJT is fixed using a constant voltage source (in this example,  $V_{CE} = 2$  V) and a dc current source  $I_B$  is applied at the base. To illustrate the dependence of  $\beta_{\rm dc}$  on the collector current  $I_C$ , we perform a dc-analysis simulation in which the sweep variable is the current source  $I_B$ . The  $\beta_{\rm dc}$  of the BJT, which corresponds to the ratio of the collector current  $I_C$  to the base current  $I_B$ , can then be plotted versus  $I_C$  using Probe (the graphical interface of PSpice), as shown in Fig. B.20. We see that to operate at the maximum value of  $\beta_{\rm dc}$  (i.e.,  $\beta_{\rm dc} = 163$ ), at  $V_{CE} = 2$  V, the BJT must be biased at an  $I_C = 10$  mA. Since increasing the bias current of a transistor increases the power dissipation, it is clear from Fig. B.20 that the choice of current  $I_C$  is a trade-off between the current gain  $\beta_{\rm dc}$  and the power dissipation. Generally speaking, the optimum  $I_C$  depends on the application and technology in hand. For example, for the Q2N3904 BJT operating at  $V_{CE} = 2$  V, decreasing  $I_C$  by a factor of 20 (from 10 mA to 0.5 mA) results in a drop in  $\beta_{\rm dc}$  of about 25% (from 163 to 123)

Figure B.19 The PSpice test bench used to demonstrate the dependence of  $\beta_{de}$  on the collector bias current  $I_c$  for the Q2N3904 discrete BJT (Example PS.6.1).

| l | Table B.6 Spice | e Model Parame | eters of the Q2 | N3904 Discrete | BJT          |             |              |

|---|-----------------|----------------|-----------------|----------------|--------------|-------------|--------------|

|   | IS=6.734F       | XTI = 3        | EG = 1.11       | VAF = 74.03    | BF = 416.4   | NE = 1.259  | ISE = 6.734F |

| ı | IKF = 66.78M    | XTB = 1.5      | BR = .7371      | NC = 2         | ISC = 0      | IKR = 0     | RC = 1       |

| ı | CJC = 3.638P    | MJC = .3085    | VJC = .75       | FC = .5        | CJE = 4.493P | MJE = .2593 | VJE = .75    |

|   | TR = 239.5N     | TF = 301.2P    | ITF = .4        | VTF = 4        | XTF = 2      | RB = 10     |              |

<sup>&</sup>lt;sup>7</sup>The Q2N3904 model is included in the evaluation (EVAL) library of PSpice, which is available on the website accompanying this book.

<sup>&</sup>lt;sup>8</sup>The reader is reminded that the schematic diagrams and the corresponding PSpice simulation files of all SPICE examples in this book can be found on the text's website (www.oup.com/us/sedrasmith). In these schematics (as shown in Fig. B.19), we use variable parameters to enter the values of the various circuit components. This allows one to investigate the effect of changing component values by simply changing the corresponding parameter values.

**Figure B.20** Dependence of  $\beta_{dc}$  on  $I_C$  (at  $V_{CE} = 2$  V) in the Q2N3904 discrete BJT (Example PS.6.1).

# **Example PS.7.2**

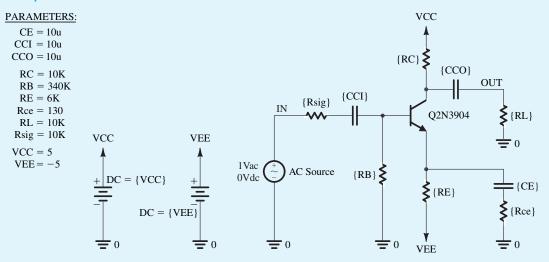

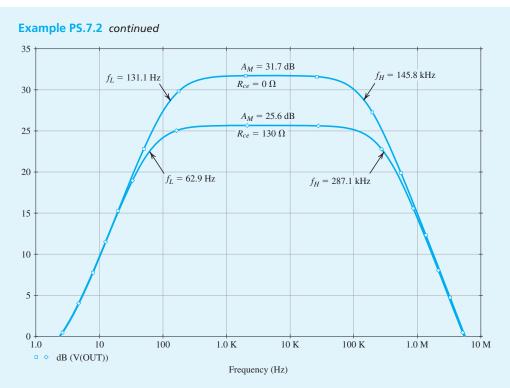

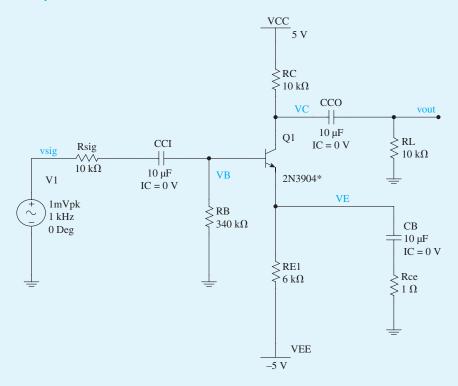

#### The CE Amplifier with Emitter Resistance

In this example, we use PSpice to analyze and verify the design of the CE amplifier. A schematic capture of the CE amplifier is shown in Fig. B.21. We will use part Q2N3904 for the BJT and a  $\pm$ 5-V power supply. We will also assume a signal source resistor  $R_{\text{sig}} = 10 \text{ k}\Omega$ , a load resistor  $R_L = 10 \text{ k}\Omega$ , and bypass and coupling capacitors of 10 µF. To enable us to investigate the effect of including a resistance in the signal path of the emitter, a resistor  $R_{ce}$  is connected in series with the emitter bypass capacitor  $C_E$ . Note that the roles of  $R_E$ and  $R_{ce}$  are different. Resistor  $R_E$  is the **dc emitter-degeneration resistor** because it appears in the dc path between the emitter and ground. It is therefore used to help stabilize the bias point for the amplifier. The equivalent resistance  $R_e = R_E \parallel R_{ce}$  is the small-signal emitter-degeneration resistance because it appears in the ac (small-signal) path between the emitter and ground and helps stabilize the gain of the amplifier. In this example, we will investigate the effects of both  $R_E$  and  $R_e$  on the performance of the CE amplifier. However, as should always be the case with computer simulation, we will begin with an approximate pencil-and-paper design. In this way, maximum advantage and insight can be obtained from simulation.

Based on the plot of  $\beta_{dc}$  versus  $I_C$  in Fig. B.20, a collector bias current  $I_C$  of 0.5 mA is selected for the BJT, resulting in  $\beta_{dc} = 123$ . This choice of  $I_C$  is a reasonable compromise between power dissipation and current gain. Furthermore, a collector bias voltage  $V_C$  of 0 V (i.e., at the mid-supply rail) is selected to

#### Example PS.7.2 continued

Figure B.21 Schematic capture of the CE amplifier in Example PS.7.2.

achieve a high signal swing at the amplifier output. For  $V_{CE} = 2$  V, the result is that  $V_E = -2$  V requires bias resistors with values

$$R_C = \frac{V_{CC} - V_C}{I_C} = 10 \,\mathrm{k}\Omega$$

and

$$R_E = \frac{V_E - V_{EE}}{I_C} = 6 \,\mathrm{k}\Omega$$

Assuming  $V_{\rm BE} = 0.7$  V and using  $\beta_{\rm dc} = 123$ , we can determine

$$R_B = -\frac{V_B}{I_B} = -\frac{0 - (V_{BE} + V_E)}{I_C / \beta_{dc}} = 320 \,\mathrm{k}\Omega$$

Next, the formulas of Section 7.3.4 can be used to determine the input resistance  $R_{\rm in}$  and the midband voltage gain  $|A_{\rm M}|$  of the CE amplifier:

$$R_{\rm in} = R_B \| (\beta_{\rm ac} + 1) \| (r_e + R_e)$$

(B.21)

$$\left| A_{M} \right| = \left| -\frac{R_{\text{in}}}{R_{\text{sig}} + R_{\text{in}}} \times \frac{R_{C} \parallel R_{L}}{r_{e} + R_{e}} \right| \tag{B.22}$$

For simplicity, we will assume  $\beta_{\rm ac} \simeq \beta_{\rm dc} = 123$ , resulting in

$$r_e = \left(\frac{\beta_{\rm ac}}{\beta_{\rm ac} + 1}\right) \left(\frac{V_T}{I_C}\right) = 49.6 \,\Omega$$

Thus, with no small-signal emitter degeneration (i.e.,  $R_{ce} = 0$ ),  $R_{in} = 6.1 \,\mathrm{k}\Omega$  and  $|A_M| = 38.2 \,\mathrm{V/V}$ . Using Eq. (B.22) and assuming  $R_B$  is large enough to have a negligible effect on  $R_{in}$ , it can be shown that

the emitter-degeneration resistor  $R_e$  decreases the voltage gain  $|A_M|$  by a factor of

$$\frac{1 + \frac{R_e}{r_e} + \frac{R_{\text{sig}}}{r_{\pi}}}{1 + \frac{R_{\text{sig}}}{r_{\pi}}}$$

Therefore, to limit the reduction in voltage gain to a factor of 2, we will select

$$R_e = r_e + \frac{R_{\text{sig}}}{\beta_{co} + 1} \tag{B.23}$$

Thus,  $R_{ce} \simeq R_e = 130 \,\Omega$ . Substituting this value in Eqs. (B.21) and (B.22) shows that  $R_{in}$  increases from  $6.1\,\mathrm{k}\Omega$  to  $20.9\,\mathrm{k}\Omega$  while  $|A_M|$  drops from  $38.2\,\mathrm{V/V}$  to  $18.8\,\mathrm{V/V}$ .

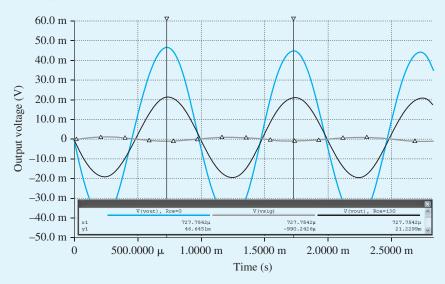

We will now use PSpice to verify our design and investigate the performance of the CE amplifier. We begin by performing a bias-point simulation to verify that the BJT is properly biased in the active region and that the dc voltages and currents are within the desired specifications. Based on this simulation, we have increased the value of  $R_B$  to 340 k $\Omega$  in order to limit  $I_C$  to about 0.5 mA while using a standard 1% resistor value (Appendix H). Next, to measure the midband gain  $A_M$  and the 3-dB frequencies  $f_L$  and  $f_H$ , we apply a 1-V ac voltage at the input, perform an ac-analysis simulation, and plot the output-voltage magnitude (in dB) versus frequency as shown in Fig. B.22. This corresponds to the magnitude response of the CE amplifier because we chose a 1-V input signal. 10 Accordingly, with no emitter degeneration, the midband gain is  $|A_M| = 38.5 \text{ V/V} = 31.7 \text{ dB}$  and the 3-dB bandwidth is  $BW = f_H - f_L = 145.7 \text{ kHz}$ . Using an  $R_{ce}$  of 130  $\Omega$  results in a drop in the midband gain  $|A_M|$  by a factor of 2 (i.e., 6 dB). Interestingly, however, BW has now increased by approximately the same factor as the drop in  $|A_M|$ . As we learned in Chapter 10 in our study of negative feedback, the emitter-degeneration resistor  $R_{ce}$  provides negative feedback, which allows us to trade off gain for other desirable properties, such as a larger input resistance and a wider bandwidth.

To conclude this example, we will demonstrate the improved bias-point (or dc operating-point) stability achieved when an emitter resistor  $R_F$  is used (see the discussion in Section 7.4.2). Specifically, we will increase/decrease the value of the parameter BF (i.e., the ideal maximum forward current gain) in the SPICE model for part Q2N3904 by a factor of 2 and perform a bias-point simulation. The corresponding change in BJT parameters ( $\beta_{ac}$  and  $\beta_{ac}$ ) and bias-point (including  $I_C$  and CE) are presented in Table B.7 for the case of  $R_E = 6 \,\mathrm{k}\Omega$ . Note that  $\beta_{\mathrm{ac}}$  is not equal to  $\beta_{\mathrm{dc}}$  as we assumed, but is slightly larger. For the case without emitter degeneration, we will use  $R_E = 0$  in the schematic of Fig. B.21. Furthermore, to maintain the same  $I_C$  and  $V_C$  in both cases at the values obtained for nominal BF, we use  $R_R = 1.12 \text{ M}\Omega$  to limit  $I_C$ to approximately 0.5 mA. The corresponding variations in the BJT bias point are also shown in Table B.7. Accordingly, we see that emitter degeneration makes the bias point of the CE amplifier much less sensitive to changes in  $\beta$ . However, unless a large bypass capacitor  $C_E$  is used, this reduced bias sensitivity comes at the expense of a reduction in the midband gain (as we observed in this example when we simulated the frequency response of the CE amplifier with an  $R_e = 130 \,\Omega$ ).

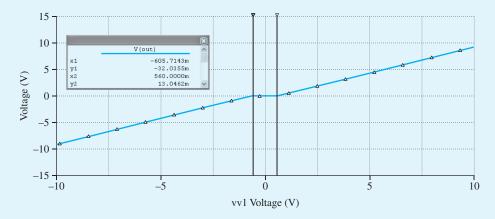

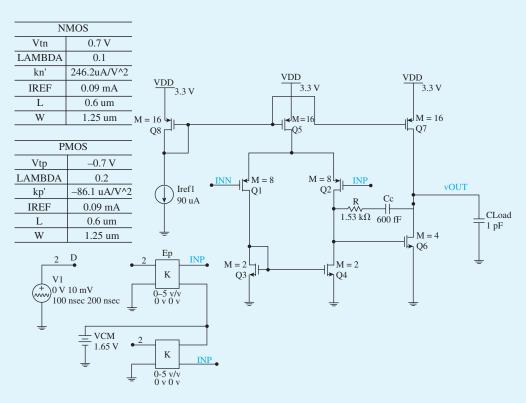

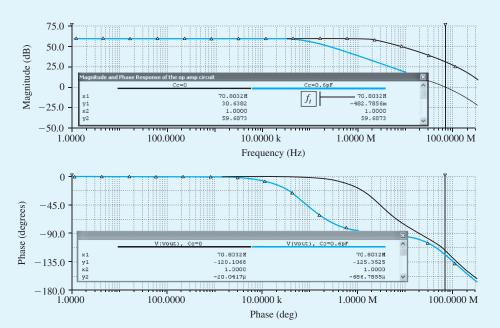

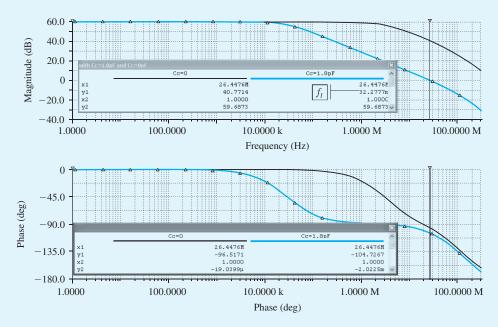

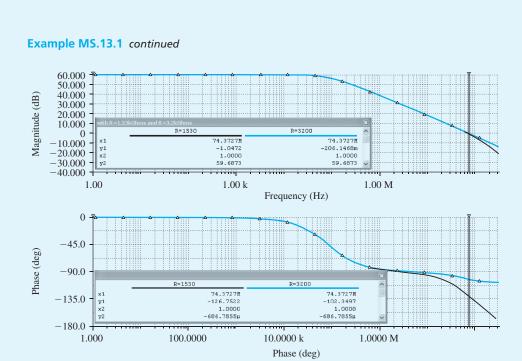

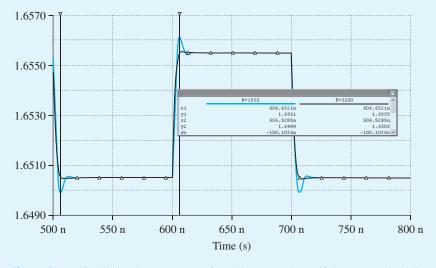

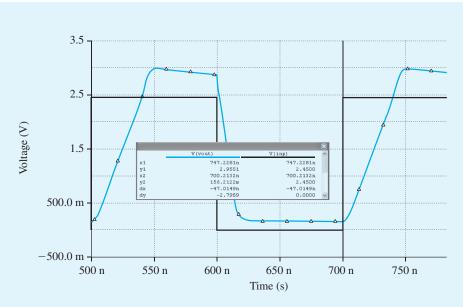

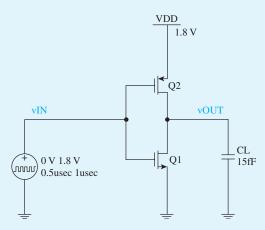

<sup>&</sup>lt;sup>9</sup>No detailed knowledge of frequency-response calculations is required for this example; all that is needed is Section 7.4.2. Nevertheless, after the study of the frequency of the CE amplifier in Sections 10.1 through 10.3, the reader will benefit by returning to this example to experiment further with the circuit using PSpice.