en

#### ©SICK STEGMANN GmbH

All rights reserved. No component of the description may by copied or processed in any other way without the written consent of the company.

This documentation applies to the HIPERFACE DSL<sup>®</sup>, release version 1.06, release date May 31, 2014.

Subject to modification without notice.

SICK STEGMANN GmbH accepts no responsibility for the non-infringement of patent rights, e.g. in the case of recommendations for circuit designs or processes.

The trade names listed are the property of the relevant companies.

HIPERFACE® and HIPERFACE DSL® are registered trademarks of SICK STEGMANN GmbH.

SICK STEGMANN GmbH Dürrheimer Strasse 36 78166 Donaueschingen, Germany Tel.: +(49) 771 / 807 – 0 Fax: +(49) 771 / 807 – 100 Internet: http://www.sick.com/ E-mail: info@sick.com

Made in Germany, 2014.

#### Table of contents

| 1.<br>1.1.<br>1.2.<br>1.3.<br>1.4.                 | Scope of application of the document<br>Symbols used<br>HIPERFACE DSL <sup>®</sup> for Motor Feedback Systems<br>Features of HIPERFACE DSL <sup>®</sup><br>Associated documents          | . 5<br>. 6<br>. 7          |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| 2.<br>2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.         | Protocol overview<br>Process data channel<br>Safe Channel 1<br>Safe Channel 2<br>Parameters Channel<br>SensorHub Channel                                                                 | 12<br>12<br>13<br>13       |  |  |

| 3.<br>3.1.<br>3.2.<br>3.3.                         | Hardware installation<br>Interface circuit<br>FPGA IP Core<br>Cable specification                                                                                                        | 15<br>18                   |  |  |

| 4.<br>4.1.<br>4.2.<br>4.3.<br>4.4.                 | Interfaces<br>Drive interface<br>SPI PIPE Interface<br>Control signals<br>Test signals                                                                                                   | 25<br>25<br>28             |  |  |

| 5.<br>5.1.<br>5.2.<br>5.3.<br>5.4.                 | Register diagram<br>Explanation of the registers<br>Online Status<br>DSL Master function register<br>Function register for the DSL Slave                                                 | 34<br>35<br>37             |  |  |

| 6.<br>6.1.<br>6.2.<br>6.3.<br>6.4.<br>6.5.<br>6.6. | Central functions<br>System start<br>System diagnostics<br>Fast position<br>Safe position, Channel 1<br>Parameters Channel<br>Status and error messages                                  | 71<br>72<br>74<br>81<br>82 |  |  |

| 7.<br>7.1.<br>7.2.                                 | Motor feedback system resources       1         Access to resources       1         Resources list       1                                                                               | 00                         |  |  |

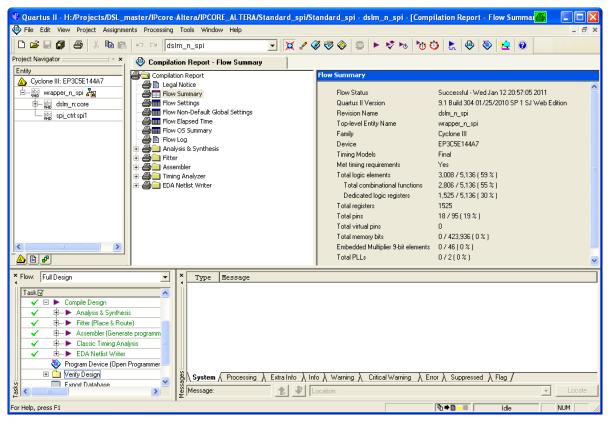

| 8.<br>8.1.<br>8.2.<br>8.3.                         | FPGA IP-Core       1         Interface blocks       1         Implementation of the IP Core for Xilinx Spartan-3E/6       1         Installation of the IP Core for Altera FPGAs       1 | 61<br>76                   |  |  |

| Keywo                                              | rds index1                                                                                                                                                                               | 92                         |  |  |

|                                                    | ry1                                                                                                                                                                                      |                            |  |  |

| Versior                                            | Versions19                                                                                                                                                                               |                            |  |  |

# Table of figures

| Figure 1: Drive system with HIPERFACE DSL <sup>®</sup>                         | 6    |

|--------------------------------------------------------------------------------|------|

| Figure 2: Length of protocol packages                                          | . 10 |

| Figure 3: Data channels in HIPERFACE DSL <sup>®</sup>                          | . 11 |

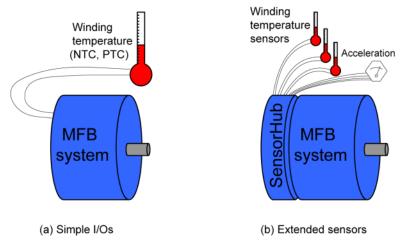

| Figure 4: HIPERFACE DSL <sup>®</sup> SensorHub interface                       | . 14 |

| Figure 5: Interface circuit with separate encoder cable                        | . 16 |

| Figure 6: Interface circuit with two core cable (integrated in cable)          | . 16 |

| Figure 7: Block diagrams of the "standard" DSL Master IP Core with interfaces  | . 18 |

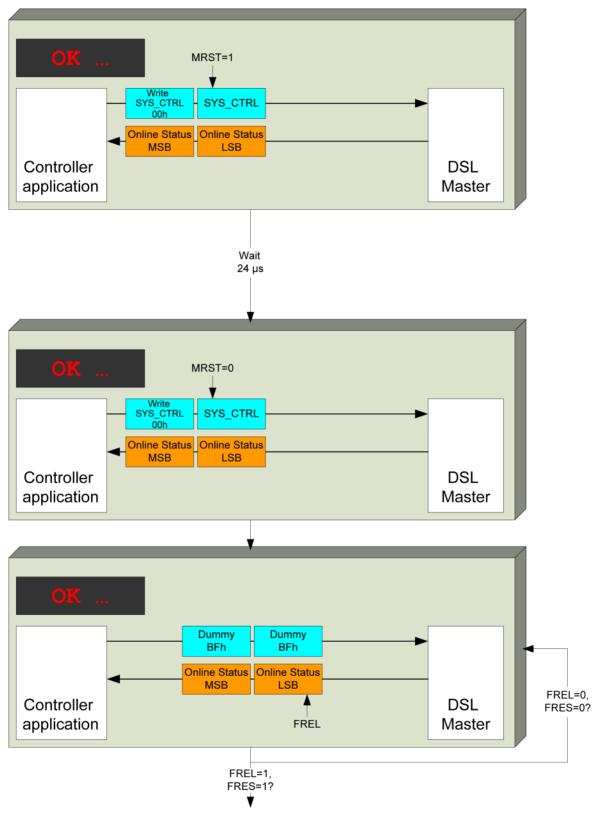

| Figure 8: Reset procedure                                                      | . 21 |

| Figure 9: Cross section of the separate encoder cable with four encoder cables | . 22 |

| Figure 10: Cross section of the integrated cable with two encoder cables       | . 23 |

| Figure 11: DSL system interfaces                                               | . 24 |

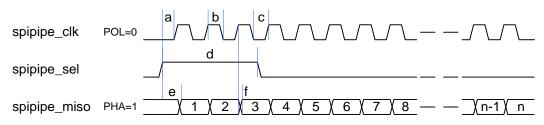

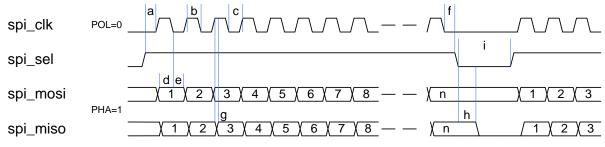

| Figure 12: SPI-PIPE interface time control                                     | . 26 |

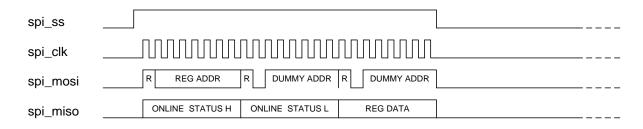

| Figure 13: "Read Pipeline" transaction                                         | . 27 |

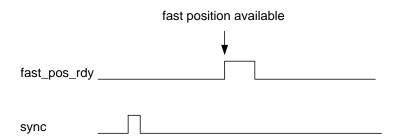

| Figure 14: fast_pos_rdy indication                                             | . 29 |

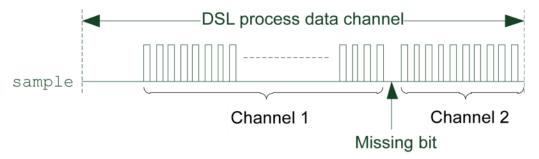

| Figure 15: Sample signal                                                       | . 30 |

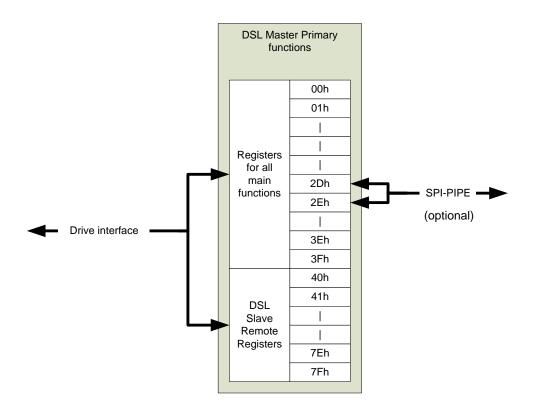

| Figure 16: Register block overview                                             | . 33 |

| Figure 17: Interrupt masking                                                   | . 46 |

| Figure 18: DSL Slave status and summary                                        | . 55 |

| Figure 19: Sequence of the bytes to calculate the CRC                          | . 57 |

| Figure 20: Status table for DSL system start                                   | . 71 |

| Figure 21: Position value format                                               | . 74 |

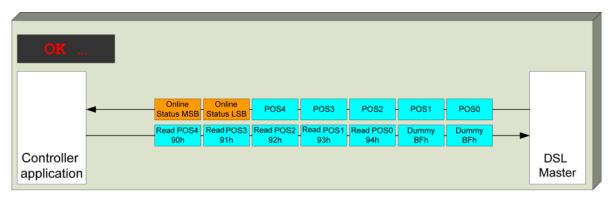

| Figure 22: Polling of position registers in free running mode                  | . 77 |

| Figure 23: Polling of rotation speed registers in free running mode            | . 77 |

| Figure 24. SYNC mode signals                                                   | . 79 |

| Figure 25: Polling registers for the fast position in SYNC mode                | . 80 |

| Figure 26: Polling of rotation speed registers in SYNC mode                    | . 80 |

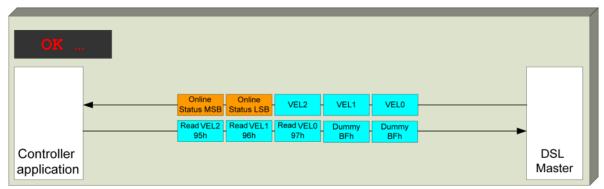

| Figure 27: Polling the safe position                                           | . 81 |

| Figure 28: Reading from remote register                                        | . 83 |

| Figure 29: "Long message" characteristics                                      | . 85 |

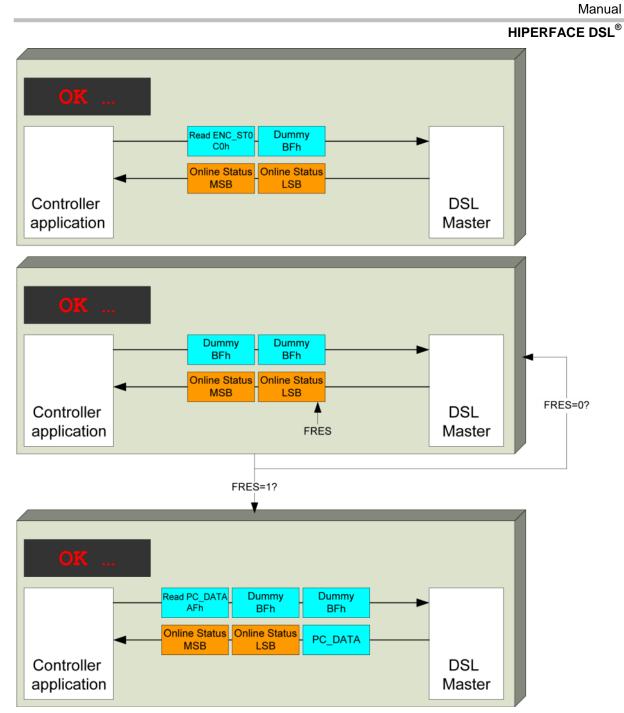

| Figure 30: Example of a "long message" read command                            | . 88 |

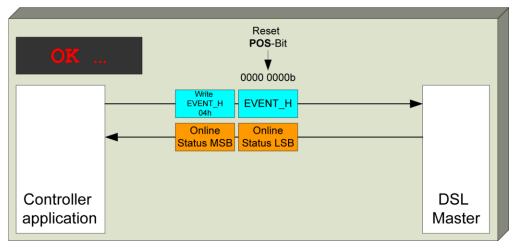

| Figure 31: Reset of the Parameters Channel                                     | . 90 |

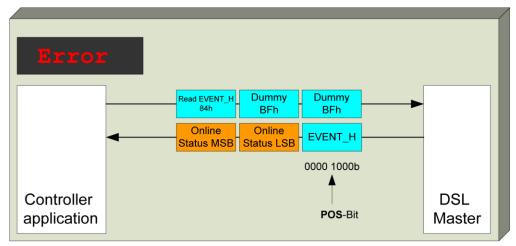

| Figure 32: Acknowledgment of event bits                                        | . 91 |

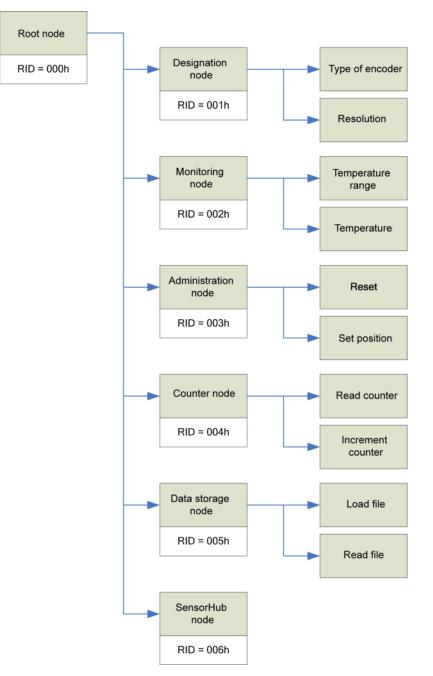

| Figure 33: Tree structure of the resources database                            | 101  |

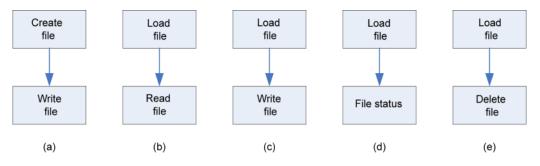

| Figure 34: Workflows for data storage 1                      | 144 |

|--------------------------------------------------------------|-----|

| Figure 35: SensorHub categories 1                            | 153 |

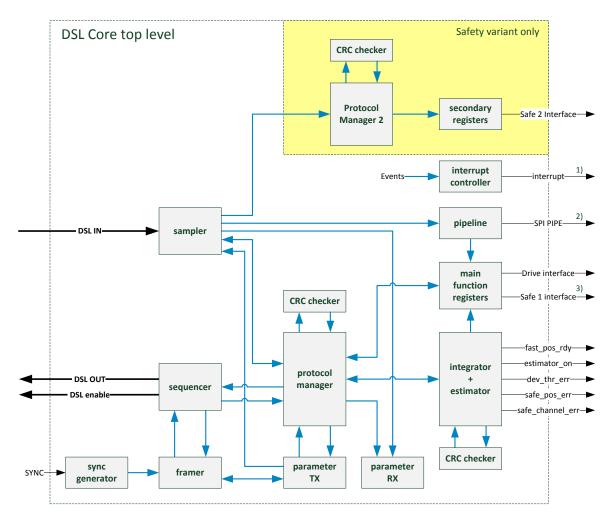

| Figure 36: Block circuit diagram of the DSL Master IP Core 1 | 157 |

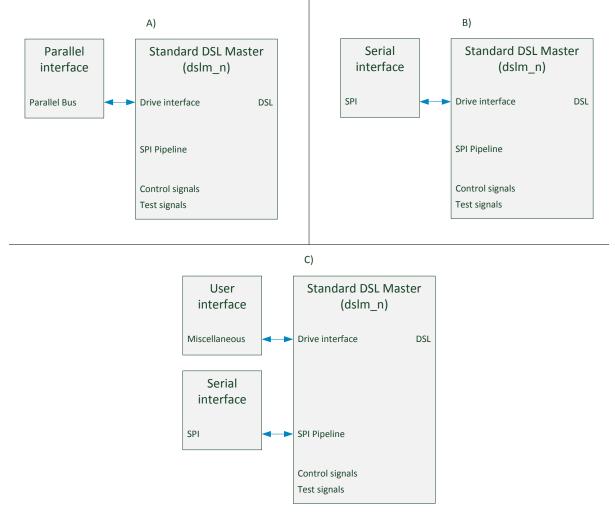

| Figure 37: Combination examples of interface blocks 1        | 161 |

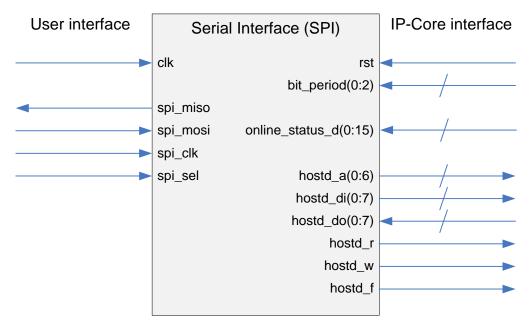

| Figure 38: Serial interface block signals 1                  | 162 |

| Figure 39: Time control of the SPI 1                         | 164 |

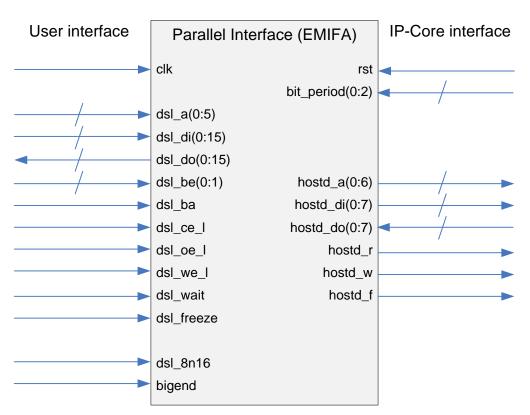

| Figure 40: Parallel interface block signals 1                | 168 |

| Figure 41: Allocation of parallel interface block to host 1  | 170 |

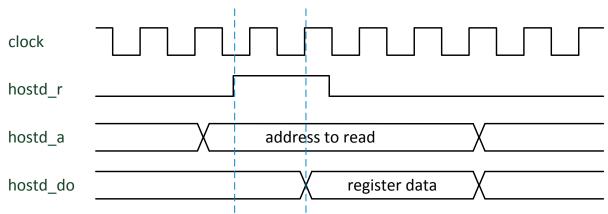

| Figure 42: Read access basic interface 1                     | 173 |

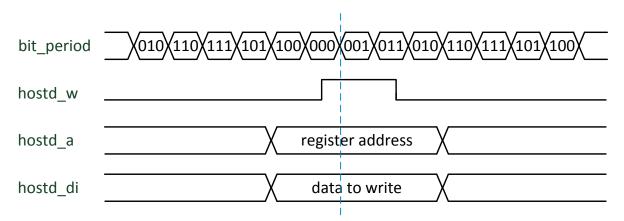

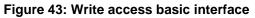

| Figure 43: Write access basic interface 1                    | 173 |

# **1. Scope of application of the document**

This document is for a standard HIPERFACE DSL<sup>®</sup> application. For safety applications, please <u>only</u> refer to the document "HIPERFACE DSL<sup>®</sup> safety manual (8017596).

## 1.1. Symbols used

#### Note/tip

Notes refer to special features of the device. Please pay attention to these notes. They often contain important information. Tips provide additional information that facilitates using the documentation.

#### Safety notes

Safety notes contain information about specific or potential dangers, and misuse of the application. This information is to prevent injury. Read and follow the safety notes carefully.

# **1.2. HIPERFACE DSL<sup>®</sup> for Motor Feedback Systems**

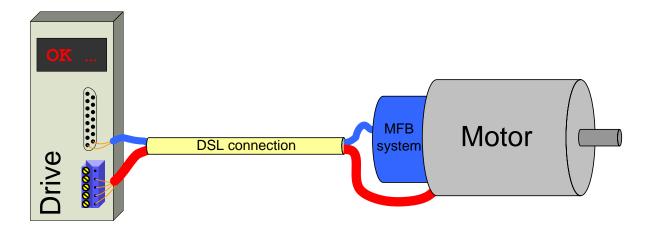

This document describes the use and implementation of the HIPERFACE DSL<sup>®</sup> data protocol installed in motor feedback systems of servo drives.

HIPERFACE DSL<sup>®</sup> is a purely digital protocol that requires a minimum of connection cables between frequency inverter and motor feedback system. The robustness of the protocol enables the connection to the motor feedback system via the motor connection cable.

Motor feedback systems with the HIPERFACE DSL<sup>®</sup> interface can be used across all performance ranges and substantially simplify the installation of an encoder system in the drive:

- Standardized digital interface (RS485)

- Analog components for the encoder interface are not required

- Standardized interface between the frequency inverter application and the protocol logic

#### Figure 1: Drive system with HIPERFACE DSL<sup>®</sup>

Based on the name for the predecessor protocol, the SICK HIPERFACE<sup>®</sup>, the name HIPERFACE DSL<sup>®</sup> stands for HIgh PERformance InterFACE Digital Servo Link.

This interface takes into account all the current requirements of digital motor feedback systems and also contains future enhancements for the manufacturers of frequency inverters.

# **1.3.** Features of HIPERFACE DSL<sup>®</sup>

Some of the main advantages of HIPERFACE  $DSL^{\mathbb{B}}$  are based on the opportunity for connection of the encoder:

- A digital interface on the frequency inverter for all communication with the motor feedback system. The interface complies with the RS485 standard with a transfer rate of 9.375 MBaud.

- Communication with the encoder via a dual cable

- Power supply and communication with the encoder can be carried out using the same dual cable. This is possible by the enhancement of the frequency inverter with a transformer.

- The connection cables to the encoder can be routed as a shielded, twistedpair cable in the power supply cable to the motor. This means that no encoder plug connector to the motor and to the frequency inverter is necessary.

- The cable length between the frequency inverter and the motor feedback system can be up to 100 m, without degradation of the operating performance.

The digital HIPERFACE DSL<sup>®</sup> protocol can be used for a variety of frequency inverter applications:

- For the feedback cycle of the frequency inverter's synchronous cyclic data that enables synchronous processing of position and rotation speed of the encoder.

- Shortest possible cycle time: 12.1 µs.

- Transmission of the safe position of the motor feedback system with a maximum cycle time of 192  $\mu s.$

- Redundant transmission of the safe position of the motor feedback system with a maximum cycle time of 192  $\mu$ s, so that suitable motor feedback systems can be used in SIL2 applications (in accordance with IEC 61508).

- Transmission of the safe position of the motor feedback system on a second channel with a maximum cycle time of 192 µs, so that suitable motor feedback systems can be used in SIL3 applications (in accordance with IEC 61508).

- Parameter data channel for bi-directional general data transfer with a band width of up to 340 kBaud. This data includes an electronic type label for designation of the motor feedback system and for storage of frequency inverter data in the motor feedback system.

- SensorHub channel via which motor data from external sensors is transmitted, that are connected by the HIPERFACE DSL<sup>®</sup> SensorHub protocol to the motor feedback system.

The protocol is integrated into the frequency inverter in the form of hardware logic. This logic circuit is supplied by several manufacturers as an IP Core for FPGA components (FPGA = Field Programmable Gate Array).

- The available protocol logic enables free routing when installing the HIPERFACE DSL<sup>®</sup> IP Core. The protocol circuit can be installed along with the frequency inverter application on the same FPGA.

- Choice between full-duplex SPI interface (SPI = serial peripheral interface) or parallel interface between protocol logic and frequency inverter applications for standardized access to process data (position, rotation speed) and parameters.

- Fast additional full-duplex SPI interface between protocol logic and frequency inverter applications for standardized access to secondary position data

- Additional configurable SPI interfaces for output of the data from external sensors.

- Configurable interrupt output

#### **1.4.** Associated documents

Along with this manual, the following documents are relevant for the use of the HIPERFACE  $DSL^{\$}$  interface:

| Document number               | Title                                    | Status     |  |  |

|-------------------------------|------------------------------------------|------------|--|--|

| 8017596                       | HIPERFACE DSL <sup>®</sup> safety manual | 2014-05-31 |  |  |

| Table 1. Associated decuments |                                          |            |  |  |

Table 1: Associated documents

Individual encoder types with the HIPERFACE DSL<sup>®</sup> interface are described with the following documents:

- Data sheet

- Operating instructions

- Errata document

# 2. Protocol overview

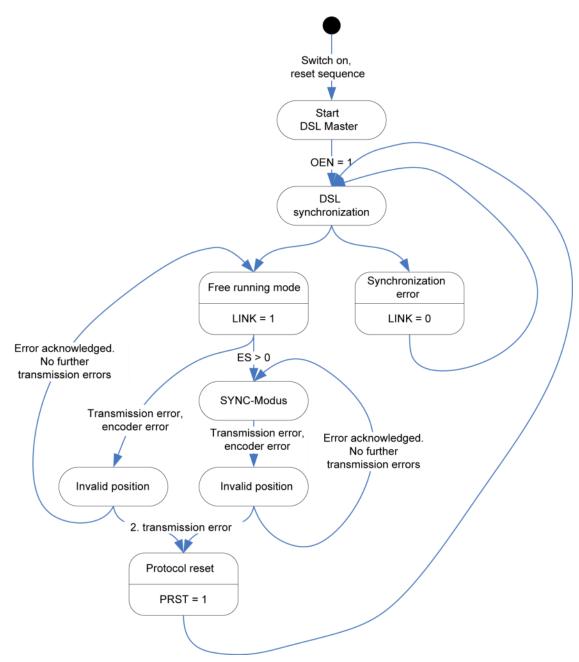

HIPERFACE DSL<sup>®</sup> is a fast digital protocol for motor feedback systems for the connection between servo drive and motor feedback system. The protocol is installed in the transport layer in the frequency inverter using a digital logic circuit (DSL Master IP Core).

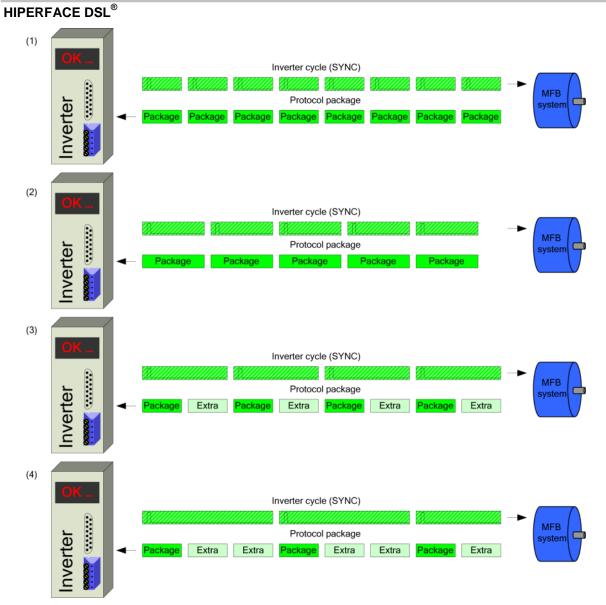

The position data are generated in two different ways in HIPERFACE DSL<sup>®</sup>, either in free running mode, in which the position values are sampled and transmitted as quickly as possible, or in SYNC mode, in which the position data are sampled and transmitted synchronously with a defined clock signal. With a frequency inverter application, this clock signal is normally the clock feedback of the frequency inverter.

In SYNC mode the protocol matches the time points for the sampling of the data without time fluctuations with the clock coming from the frequency inverter.

For each frequency inverter cycle at least one position value is sampled and transmitted with constant latency to the DSL Master. As the protocol matches the internal data transfer speed to the frequency inverter cycle, the overall transfer rate of the HIPERFACE DSL<sup>®</sup> depends on the frequency inverter clock.

The protocol package is matched to the various lengths, see Figure 2. Provided the frequency inverter cycle is long enough, additional sampling points can be positioned in the frequency inverter cycle, known as "extra" packages. The number of additional packages is programmed by the user with a distribution value.

The number of packages transmitted per frequency inverter cycle cannot be selected at random, as the lower and upper range length of a protocol package must be adhered to. This must be taken into account when setting the distribution value.

In free running mode, the frequency inverter cycle is not taken into account for sampling and transmission and the protocol uses the minimum package length.

It must be noted that the minimum package length in free running mode is shorter than the minimum package length in SYNC mode.

Table 2 shows the dependency of the lengths of the protocol packages using examples for the length of the frequency inverter cycle.

Manual

Figure 2: Length of protocol packages

| Inverter cycle frequency<br>(kHz) | Length of the<br>frequency inverter<br>cycle (µs) | Length of the protocol<br>package<br>(μs) | Protocol<br>packages per<br>frequency inverter<br>cycle |

|-----------------------------------|---------------------------------------------------|-------------------------------------------|---------------------------------------------------------|

| 2                                 | 500                                               | 12.50                                     | 40                                                      |

| 4                                 | 250                                               | 12.50                                     | 20                                                      |

| 6.25                              | 160                                               | 13.33                                     | 12                                                      |

| 8                                 | 125                                               | 12.50                                     | 10                                                      |

| 16                                | 62.5                                              | 12.50                                     | 5                                                       |

| 40                                | 25                                                | 12.50                                     | 2                                                       |

| 37 to 84                          | 27 to 12.1                                        | 27 to 12.1                                | 1                                                       |

| Free running                      |                                                   | 11.52                                     |                                                         |

Table 2: Frequency inverter cycle and length of protocol packages

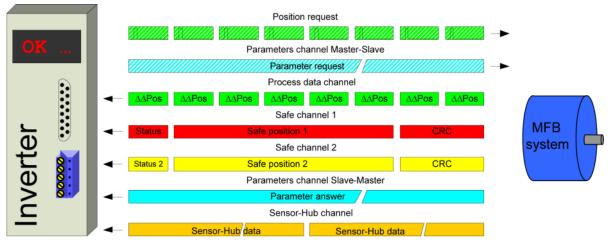

In HIPERFACE DSL<sup>®</sup>, the data are transmitted over several channels. Each individual channel is adapted to different requirements according to its content. The cycle time of each individual channel varies with the length of the basic protocol package.

Figure 3: Data channels in HIPERFACE DSL<sup>®</sup>

Table 3 gives an overview of the characteristics of the various channels.

It should be noted that the minimum cycle time and the maximum band width only apply if the maximum number of sample points per frequency inverter cycle was programmed (refer to "Register synchronization control", section 5.3.2).

| Channel in<br>HIPERFACE DSL <sup>®</sup> | Function                                      | Cycle time<br>(µs) | Band width<br>(kBaud) |

|------------------------------------------|-----------------------------------------------|--------------------|-----------------------|

| Process data channel                     | Fast position, rotation speed                 | 12.1 to 27.0       | 1321 to 669           |

| Safe Channel 1                           | Absolute / safe position, status of Channel 1 | 96.8 to 216.0      | 660 to 334            |

| Safe Channel 2                           | Absolute / safe position, status of Channel 2 | 96.8 to 216.0      | 660 to 334            |

| Parameter channel                        | General data, parameters                      | Variable           | 330 to 167            |

| SensorHub channel                        | External data                                 | 12.1 to 27.0       | 660 to 334            |

Table 3: Channels for protocol data

## 2.1. Process data channel

The fast position value of the motor feedback system is transferred on the process data channel synchronously with the position requests that are controlled by the signal at the SYNC input of the frequency inverter cycle.

The process data channel is the fastest channel of the HIPERFACE DSL<sup>®</sup> protocol. Every protocol package transferred contains a complete update of the content of this channel.

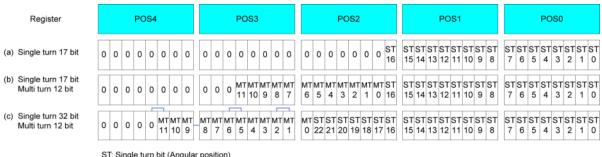

This content consists of increments to rotation speed and fast position that are used as feedback parameters for the control loop of the motor drive (see sections 5.3.11 and 5.3.12).

If the fast position from the process data channel cannot be calculated (either due to transmission or due to sensor errors), estimation is made by the DSL Master based on the last two available position values of Safe Channel 1. The worst case deviation from the actual mechanical position is also provided.

For reliable position estimation, the user needs to provide application specific information about maximum speed and maximum acceleration. Please see section 6.3.1 for details.

# 2.2. Safe Channel 1

The safe position value of the motor feedback system is transferred on the Safe Channel as an absolute value. In addition, the status of the encoder is reported on this channel in the form of errors and warnings.

The safe position value transferred on the Safe Channel is not synchronous with the frequency inverter cycle signal at the SYNC input.

The safe position is used by the DSL Master IP Core to check the fast position value of the process data channel and can be used by the frequency inverter application for the same purpose.

Where there are deviations between the safe and the fast position values, an error message is generated (see section 4.4.2). In this case, the protocol replaces the fast position with the estimated position. Please see section 6.3.1 for details.

In each package of the safe channel, a collection of status bits is transferred that reflects the error and warning condition of the motor feedback system.

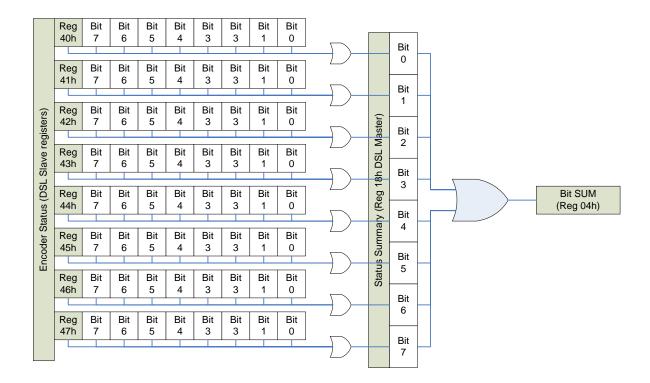

It should be noted that each bit of the summary byte of the Safe Channel refers to one status byte the motor feedback system. Each status byte of the encoder can be read with a "short message" (see section 6.5.1).

# 2.3. Safe Channel 2

In Safe Channel 2, copies of the absolute position value and the status of the motor feedback system are transferred. This information can be discarded in standard applications.

The Safe Channel 2 is only accessible in the safety variants of the DSL Master IP Core.

## 2.4. Parameters Channel

The Parameters Channel is the interface, over which the frequency inverter application reads and writes parameters of the motor feedback system.

In addition to the main task of position measurement, motor feedback systems with the HIPERFACE DSL<sup>®</sup> interface also have various internal resources installed. These resources are accessible via the Parameters Channel.

Examples of these resources are temperature measurements, monitoring - mechanisms for correct functioning, product data (the "electronic type label") or freely programmable data fields.

It should be noted that the resources actually installed for DSL products differ and are listed in the relevant product data sheet.

There are two types of communication on the Parameters Channel:

- "Short message" transaction

- "Long message" transaction

A "short message" transaction allows access to resources that have an influence on the HIPERFACE DSL<sup>®</sup> protocol interface and are used for monitoring them. This includes detailed status and error messages for the motor feedback system and indications of the signal strength on the DSL connection. As a "short message" transaction is processed directly by the interface logic of the motor feedback system, this transaction is completed in a comparatively short time.

A "long message" transaction allows access to all the other resources of the motor feedback system. Unlike a "short message" transaction, a "long message" normally requires processing by the motor feedback system processor and therefore has does not have a response time that can be defined in advance.

It should be noted that in HIPERFACE DSL<sup>®</sup>, a maximum of one "short message" and one "long message" are processed at any time.

HIPERFACE DSL®

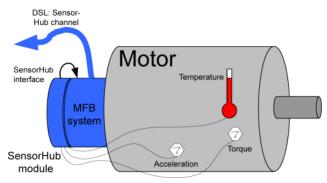

## 2.5. SensorHub Channel

Data from additional external sensors can be transferred on the SensorHub Channel that can be used in the frequency inverter system. External sensors must be connected to the motor feedback system via the HIPERFACE DSL<sup>®</sup> SensorHub interface. Various sensors or sensor networks are accessible via this interface and can be selected using HIPERFACE DSL<sup>®</sup>.

The configuration of external sensors is carried out via the Parameters Channel, whilst the data are selected via the SensorHub Channel. The transfer of protocol packages in the SensorHub Channel takes place synchronously with the DSL transfer and as an extension of the frequency inverter cycle signal that is present at the DSL Master SYNC input. Depending on the use of the SensorHub interface, external data can therefore be sampled and transferred synchronously.

The protocol in the SensorHub Channel is not monitored by HIPERFACE DSL<sup>®</sup>. Apart from the monitoring of the data transfer quality, there are no protocol mechanisms on this channel.

Figure 4: HIPERFACE DSL<sup>®</sup> SensorHub interface

# 3. Hardware installation

The installation of HIPERFACE DSL<sup>®</sup> in a drive system requires an interface circuit with special components as well as the installation of a digital logic core for an FPGA component.

The interface circuit is described thoroughly in this chapter. The chapter also contains recommendations for the selection of components.

The digital logic core (IP Core) is supplied by SICK for prescribed FPGA types.

In addition, the type of cable recommended for the connection between the frequency inverter and the motor feedback system is described thoroughly in this chapter.

It may also be possible to use other sorts of cable. These must be tested before use, however.

As a physical layer, HIPERFACE DSL<sup>®</sup> uses a transfer in accordance with EIA-485 (RS-485). Valid RS-485 interface drivers must comply with the conditions in Table 4.

| Characteristic                           | Value     | Units |

|------------------------------------------|-----------|-------|

| Transfer rate                            | >20       | MBaud |

| Permitted common mode voltage            | -7 to +12 | V     |

| Receiver: Differential threshold voltage | < 200     | mV    |

| Load resistance                          | < 55      | Ohm   |

| Receiver running time delay              | < 60      | ns    |

| Sender running time delay                | < 60      | ns    |

| Sender power-up delay                    | < 80      | ns    |

| Sender power-down delay                  | < 80      | ns    |

| Sender rise time                         | < 10      | ns    |

| Sender dropout time                      | < 10      | ns    |

| Protection against short-circuit         |           |       |

| Protection against bus conflict          |           |       |

Table 4: Valid RS-485 interface drivers

## 3.1. Interface circuit

HIPERFACE DSL<sup>®</sup> can be used in connection with two different interface circuit configurations. Each configuration requires a different sort of connection cable (see section 3.3).

Please note that the use of four core cable is no longer recommended for the motor cable.

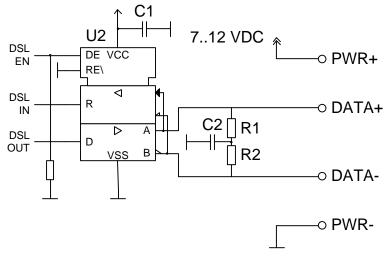

#### 3.1.1. Separate encoder cable - four core cable

When using a separate encoder cable (see section 3.3.1), the smallest interface circuit can be used. The separate encoder cable requires a four core connection.

In connection with the associated table, Figure 5 below gives the specification of the interface circuit.

#### HIPERFACE DSL®

Figure 5: Interface circuit with separate encoder cable

| Component |                   | Part         | Manufacturer      |

|-----------|-------------------|--------------|-------------------|

| C1        | Ceramic capacitor | 100 nF       |                   |

| C2        | Ceramic capacitor | 2.2 μF, 16 V |                   |

| R1, R2    | Resistors         | 56R          |                   |

| U2        | RS485 transceiver | SN65LBC176A  | Texas Instruments |

|           |                   | SN75LBC176A  | Texas Instruments |

Recommended components for the interface circuit are set out in Table 5

Table 5: Components for the interface circuit with separate encoder cable.

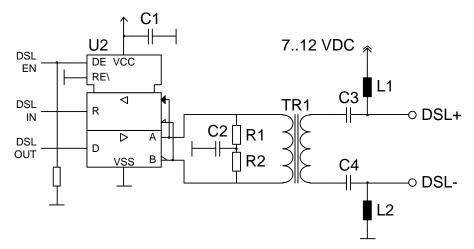

#### 3.1.2. Integrated cable - two core cable

For a connection via a two core cable integrated in the motor cable, (see section 3.3.2), the data cables must be provided with a transformer to raise the common mode rejection ratio. To feed the supply voltage into the data cables choke coils are also required.

In connection with the associated table, Figure 6 below gives the specification of the interface circuit.

#### Figure 6: Interface circuit with two core cable (integrated in cable) Recommended components for the interface circuit are set out in Table 6.

| Component |                   | Part               | Manufacturer      |

|-----------|-------------------|--------------------|-------------------|

| C1        | Ceramic capacitor | 100 nF             |                   |

| C2        | Ceramic capacitor | 2.2 μF, 16 V       |                   |

| C3, C4    | Ceramic capacitor | 470 nF, 50 V       |                   |

| L1, L2    | Choke coils       | 744043101, 100 µH  | Würth Elektronik  |

|           |                   | ELL6SH101M, 100 µH | Panasonic         |

| R1, R2    | Resistors         | 56R                |                   |

| U2        | RS485 transceiver | SN65LBC176A        | Texas Instruments |

|           |                   | SN75LBC176A        | Texas Instruments |

| TR1       | Transformer       | PE-68386NL         | Pulse Engineering |

|           |                   | 78602/1C           | Murata            |

|           |                   | B78304B1030A003    | Epcos             |

|           |                   | 78602/1C           | Epcos             |

Table 6: Components of the interface circuit with two core cable (integrated in cable)

#### Motor feedback voltage supply 3.1.3.

Motor feedback systems with HIPERFACE  $DSL^{\text{®}}$  have been developed for operation with a supply voltage of 7 to 12 V. The voltage supply is measured at the encoder plug connector.

Table 7 below describes the specification for the power supply.

| Parameter               | Value                       |

|-------------------------|-----------------------------|

| Switch-on voltage ramp  | Max. 180 ms from 0 to 7 V   |

| Inrush current          | Max. 3.5 A (0 to100 µs)     |

| infush current          | Max. 1 A (100 µs to 400 µs) |

| Operating current       | Max. 250 mA at 7 V          |

| Table 7: Voltage supply |                             |

Table 7: Voltage supply

#### HIPERFACE DSL®

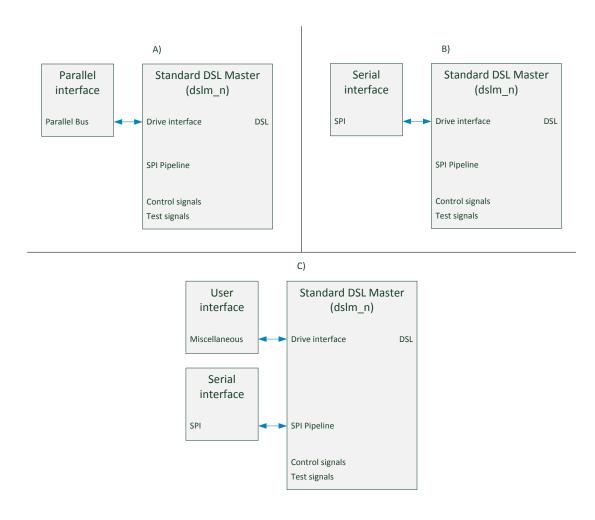

## 3.2. FPGA IP Core

The frequency inverter system communicates with the DSL motor feedback system via a special protocol logic circuit that is designated as the DSL Master. The circuit is supplied by SICK and must be installed in an FPGA component. It is supplied as an Intellectual Property Core (IP Core). The DSL Master IP Core is supplied in different forms, depending on the FPGA vendor preferred by the user (compiled netlist or encrypted VHDL). If there is sufficient space in the FPGA being used, the DSL Master can be installed in the same component as the frequency inverter application.

There are two different IP Cores available, one for standard and one for safety applications. This manual only describes the standard variant. Please choose according to the desired system.

For interfacing the IP Core, several options are available. For details of those interface blocks see section 8.1.

The following figure show the possible combinations of IP Core and interface block variants.

|                                                   | Value        |         |              |                    |                                                                           |

|---------------------------------------------------|--------------|---------|--------------|--------------------|---------------------------------------------------------------------------|

| Parameter                                         | Mini-<br>mum | Typical | Maxi-<br>mum | Units              | Remarks                                                                   |

| System Clock                                      | 74.9925      | 75.0000 | 75.0075      | MHz                | ± 100 ppm                                                                 |

| Interface characteristics                         |              |         |              |                    | · · · ·                                                                   |

| Cable transfer rate                               |              | 9.375   |              | MBd                |                                                                           |

| Reset duration                                    | 0.02         | 0.06    |              | μs                 | Reset is High active                                                      |

| Recovery time after                               |              |         | 727          |                    |                                                                           |

| communication errors                              |              |         | 121          | μs                 |                                                                           |

| Characteristics of the motor feedb                | ack systen   | n       |              |                    |                                                                           |

| Position resolution per rotation                  |              | 24      | 40           | Bit                | The total can be                                                          |

| Number of resolved rotations                      |              | 16      | 40           | Bit                | a maximum of 40 bits                                                      |

| Rotation speed                                    |              |         | 262,000      | rad/s              | 24 bit/rotation                                                           |

| Acceleration                                      |              |         | 670,000      | rad/s <sup>2</sup> | 24 bit/rotation                                                           |

| Sampling latency                                  |              | 10.5    |              | μs                 | SYNC trigger up to valid position                                         |

| Characteristics of the host interfac              | ce           |         |              |                    |                                                                           |

| Frequency inverter cycle time                     | 12.1         |         | 1,950        | μs                 | in SYNC mode                                                              |

| Frame cycle time                                  | 12.1         |         | 27           | μs                 | in SYNC mode                                                              |

| Frame cycle time                                  |              | 11.52   |              | μs                 | In free running mode                                                      |

| Duration of the SYNC signal                       | 0.04         |         |              | μs                 | The SYNC signal<br>must be inactive for<br>at least 0.04 µs per<br>cycle. |

| Jitter of the SYNC signal frequency               |              | 26      |              | ns                 | ± 2 system clock<br>cycles                                                |

|                                                   |              | _       |              |                    |                                                                           |

| Characteristics of the SPI-PIPE int               | erface bloc  | cks     | 1            | 1                  | 1                                                                         |

| SPI-PIPE clock                                    |              |         | 10           | MHz                |                                                                           |

| Characteristics of the Parameters                 |              |         |              | <u>.</u> .         |                                                                           |

| Theoretical transfer rate                         | 166          |         | 334          | kBd                |                                                                           |

| Duration of access to the communications resource | 167          |         | 1,100        | μs                 | "Short message"                                                           |

| Duration of access to the encoder resource        | 263          |         | 764          | μs                 | "Long message"                                                            |

| Characteristics of the SensorHub                  | Channel      |         |              |                    |                                                                           |

| Transfer rate                                     | 334          |         | 669          | kBd                |                                                                           |

Table 8: Characteristics of the DSL Master IP Core

# 3.2.1. DSL Master inputs / outputs

| Signal name      | Туре        | Function                                |  |  |

|------------------|-------------|-----------------------------------------|--|--|

| rst*             | Input       | Master reset (High active)              |  |  |

| clk*             | Input       | Clock input                             |  |  |

| sync*            | Input       | Position sampling resolution            |  |  |

| interrupt        | Output      | Configurable interrupt                  |  |  |

| link             | Output      | Connection indication                   |  |  |

| pos_ready        | Output      | Position data availability indication   |  |  |

| sync_locked      | Output      | Position sampling resolution locked     |  |  |

| bigend           | Input       | Byte sequence choice                    |  |  |

| fast_pos_rdy     | Output      | Fast position update indication         |  |  |

| sample           | Output      | DSL bit sampling information            |  |  |

| estimator_on     | Output      | Postion Estimator activated             |  |  |

| safe_channel_err | Output      | Transmission error in safe channel 1    |  |  |

| safe_pos_err     | Output      | Safe position not valid                 |  |  |

| acceleration_err | Output      | Fast channel / position error           |  |  |

|                  |             | Fast channel / position threshold error |  |  |

| encoding_err     | Output      | DSL message encoding error              |  |  |

| dev_thr_err      | Output      | Estimator deviation threshold reached   |  |  |

| aux_signals      | Output (12) | Auxiliary signals                       |  |  |

| dsl_in*          | Input       | DSL cable, input data                   |  |  |

| dsl_out*         | Output      | DSL cable, output data                  |  |  |

| dsl_en*          | Output      | DSL cable transceiver, activation       |  |  |

| spipipe_ss       | Input       | SensorHub SPI choice                    |  |  |

| spipipe_clk      | Input       | Serial clock for SPI SensorHub          |  |  |

| spipipe_miso     | Output      | SPI SensorHub, master output data/slave |  |  |

|                  |             | input data                              |  |  |

| online_status_d  | Output (16) | IP Core status information              |  |  |

| hostd_a          | Input (7)   | Host interface address                  |  |  |

| hostd_di         | Input (8)   | Host interface data in                  |  |  |

| hostd_do         | Output (8)  | Host interface data out                 |  |  |

| hostd_r          | Input       | Host interface data read                |  |  |

| hostd_w          | Input       | Host interface data write               |  |  |

| hostd_f Input    |             | Host interface register freeze          |  |  |

Table 9: Pin functions of the IP Core interface

\* these signals must be assigned to physical pins of the FPGA.

## SYNC signal:

The HIPERFACE DSL communication can be established in "SYNC mode" or "free running mode". In free running mode, the IP-Core will use the fastest possible transmission timing and this input should be low (0). Please note that the IP-Core is not bound to any timing of the frequency inverter in this mode.

In SYNC mode the frequency inverter clock must be supplied to this input/pin. Please refer to table 8 for the signal specification. This signal triggers position sampling of the DSL encoder. The polarity of the edge can be programmed using the SPOL bit in the SYS\_CTRL register.

As the frame cycle time must always be within a limited range, a divider for the SYNC frequency has to be chosen accordingly. The divider value needs to be written to the SYNC\_CTRL register.

In case of the SYNC frequency changing, the IP-Core will synchronize automatically. During this synchronization the former sampling frequency is used. Please note that this synchronization takes a few SYNC periods.

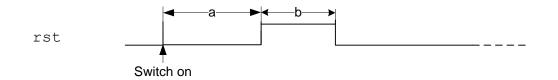

#### Reset signal:

rst is the reset input (high active) of the DSL Master IP Core.

After start-up (switching on) of the frequency inverter, a reset procedure is mandatory to return the DSL Master IP Core to its initialization condition.

The reset procedure is established by the parameters listed in Table10 and quoted in Figure 8.

#### Figure 8: Reset procedure

| Diagram reference              | Parameters in Table 8        | Value (cf. Table 8) |  |  |  |

|--------------------------------|------------------------------|---------------------|--|--|--|

| а                              | Reset delay                  | Variable            |  |  |  |

| b                              | Duration of the reset signal | >60 ns              |  |  |  |

| Table 40: Deast time assurance |                              |                     |  |  |  |

Table 10: Reset time sequence.

Additional pin functions are described in detail in chapter 4.

# 3.3. Cable specification

The cable recommended for connecting the frequency inverter to the HIPERFACE DSL<sup>®</sup> motor feedback system is specified by the parameters set out in Table 10. These technical data apply to all configurations.

In the case of integrated cables (see section 3.3.2), the motor cables are not listed.

| Characteristic            | Minimum | Typical | Maximum | Units |  |

|---------------------------|---------|---------|---------|-------|--|

| Length                    |         |         | 100     | m     |  |

| Impedance at 10 MHz       | 100     | 110     | 120     | Ω     |  |

| DC loop resistance        |         |         | 0.1     | Ω/m   |  |

| Velocity ratio            | 0.66    |         |         | С     |  |

| Propagation delay         |         | 5       |         | ns/m  |  |

| Limit frequency           | 25      |         |         | MHz   |  |

| Maximum current per cable | 0.25    |         |         | А     |  |

| Operating temperature     | -40     |         | 125     | °C    |  |

Table 11: Technical data for the HIPERFACE DSL<sup>®</sup> cable

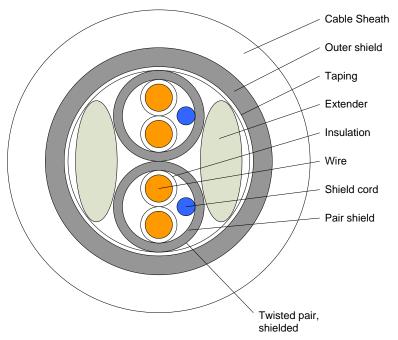

#### 3.3.1. Separate encoder cable - four core cables

The recommended cross section of the separate encoder cable with four encoder cables is given in Figure 9.

Figure 9: Cross section of the separate encoder cable with four encoder cables

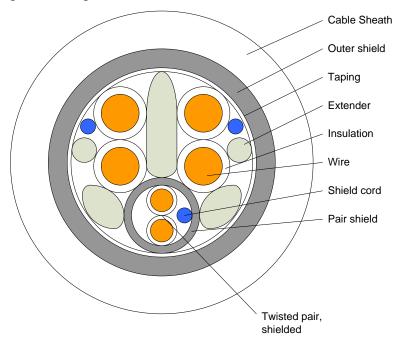

#### 3.3.2. Integrated cable - two core cable

The recommended cross section of the integrated cable with two encoder cables is given in Figure 10.

Figure 10: Cross section of the integrated cable with two encoder cables

More information relating cable construction and installation are available on the Whitepaper "Cable and Connector for HIPERFACE DSL<sup>®</sup> Motor and Drive Applications".

http://www.sick.com/group/EN/home/products/technologies/hiperfacedsl/Pages/hiperfacedsl\_documentation.aspx

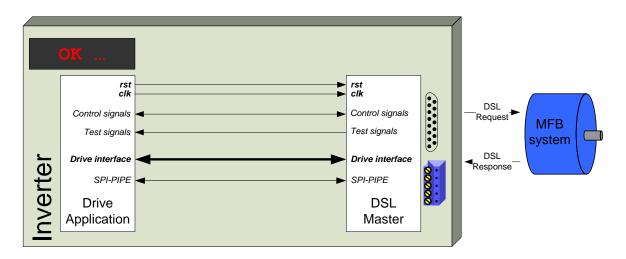

# 4. Interfaces

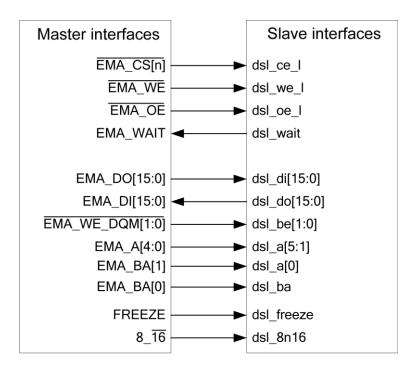

The IP Core of the DSL Master includes interfaces to the motor feedback system (DSL Slave) and to the frequency inverter application (see Figure 11).

The motor feedback system communicates via a DSL connection with the DSL Master. All data channels between the DSL Master and DSL Slave are routed via this connection.

The frequency inverter is connected via one interface (choice of SPI or parallel bus) and several control signals. In addition, the frequency inverter provides a clock signal (CLK) and a reset signal (RST) to the DSL Master IP Core. By means of these signals, a defined start-up performance is achieved.

According to the requirements of the particular application, an optional serial interface (SPI-PIPE) can be employed to use the SensorHub Channel (see Section 2.5, SensorHub Channel).

The various interfaces correspond to the tasks described in Table 12.

Figure 11: DSL system interfaces

| Interface       | Туре                 | Function                                                 |  |  |

|-----------------|----------------------|----------------------------------------------------------|--|--|

| Drive interface | Full duplex SPI      | Register-based access to all DSL Master and DSL Slave    |  |  |

|                 | -or-                 | functions                                                |  |  |

|                 | Parallel bus         |                                                          |  |  |

| SPI PIPE        | SPI with read access | Optional register-based access to SensorHub Channel data |  |  |

| Control signals | Digital in/outputs   | DSL Master indication and control signals                |  |  |

| Test signals    | Digital outputs      | Test signals for development or fault-finding for a DSL  |  |  |

|                 |                      | controller                                               |  |  |

| CLK             | Digital input        | Clock signal for the IP Core circuit                     |  |  |

| RST             | Digital input        | Reset signal for the IP Core circuit                     |  |  |

| DSL             | Half duplex RS485    | Connection to the motor feedback system                  |  |  |

Table 12: Interface functions

# 4.1. Drive interface

The drive interface forms the central communications interface between the frequency inverter application and the DSL Master IP Core. Absolute and fast position data can be read via this interface. The functions of the motor feedback system are also accessible via this interface.

| Pin name              | Туре        | Function                         |

|-----------------------|-------------|----------------------------------|

| online_status_d(0:15) | Output      | IP Core status (see section 5.2) |

| hostd_a(0:6)          | Input       | Register address bus             |

| hostd_di(0:7)         | Input       | Register input data bus          |

| hostd_do(0:7)         | Output      | Register output data bus         |

| hostd_r               | Input       | Read signal                      |

| hostd_w               | Input       | Write signal                     |

| hostd_f               | Input       | Freeze signal                    |

| Table 12 Drive interf | aaa alanala |                                  |

The following signals are used for Drive interface:

Table 13. Drive interface signals.

Example installations of interface blocks for the Drive interface of the DSL Master are supplied together with the IP Core. These examples include a serial SPI interface and a parallel Texas Instruments EMIFA interface. For more information please see section 8.1.

# 4.2. SPI PIPE Interface

The SPI PIPE is a write-protected Serial Peripheral Interface (SPI). SPI PIPE is an optional communication channel between the frequency inverter application and the DSL Master IP Core. Read processes on the SensorHub Channel can be carried out via this interface. Alternatively, this data can also be read from the registers by standard transactions via Drive interface.

The type of access to the SensorHub Channel is selected by setting or deleting the **SPPE** bits in the **SYS\_CTRL** register (see section 5.3.1). If the **SPPE** bit is deleted, the data and the status of the SensorHub channel are accessible via the DSL Master **PIPE\_S** (2Dh) and **PIPE\_D** (2Eh) registers. If the **SPPE** bit is set, the SensorHub Channel is read using the SPI PIPE "Read Pipeline" transaction.

SPI PIPE should be activated if, at a fast frequency inverter cycle, the bandwidth of Drive interface is insufficient to access position and pipeline data, or if the pipeline data is being processed by another frequency inverter application resource.

It should be noted that in every case, the configuration of external sensor components at the SensorHub is carried out via the DSL Master Parameters Channel. The SPI PIPE provides only one read access to the SensorHub Channel (see section 2.5, SensorHub Channel).

The SensorHub Channel data is kept in a FIFO (First In First Out) buffer that can hold 8 bytes. In addition, for each data byte, status information is also stored in the FIFO buffer (see sections 5.3.21 and 5.3.22).

It should be noted that the FIFO buffer can only store 8 bytes of SensorHub Channel data. If the buffer is not read quickly enough, old data will be overwritten. This is indicated by a flag in the FIFO buffer status information.

The SPI Master for the SPI PIPE is the frequency inverter application. The SPI functions "Slave Selection" (Pin: spipipe\_sel) and "clock" (Pin: spipipe\_clk) are controlled by the frequency inverter application. The SPI function "Data, Master input Slave output" (Pin: spipipe miso) is controlled by the DSL Master.

SPI PIPE has the following SPI characteristics:

- PHA = 1 (Sampling for clock trailing edge, data changes for clock leading edge)

- POL = 0 (Basic clock value)

The data with the highest value bit (MSB) is given first.

When accessing the SensorHub Channel via the SPI PIPE, the first four bits of the status buffer (0101) show a different value for each transaction, in order to check the correct function of the interface.

#### 4.2.1. SPI-PIPE timing

The time sequence for SPI PIPE is shown in the time sequence diagram (Figure 12) below and in Table 15.

Figure 12: SPI-PIPE interface time control

| Diagram<br>reference | Description                                | Minimum | Maximum | Units |

|----------------------|--------------------------------------------|---------|---------|-------|

| А                    | Creation of spipipe_sel before spipipe_clk | 30      |         | ns    |

| В                    | Time for spipipe_clk high                  | 30      |         | ns    |

| С                    | Time for spipipe clk low                   | 30      |         | ns    |

| D                    | spipipe sel <b>pulse width</b>             | 30      |         | ns    |

| E                    | Delay spipipe_miso after spipipe_sel high  | 25      | 70      | ns    |

| F                    | Delay spipipe_miso after spipipe_clk high  | 25      | 70      | ns    |

Table 14: SPI-PIPE time control

#### 4.2.2. Read pipeline

The SPI PIPE transaction "Read Pipeline" is used for access to the FIFO buffer values that contain the data and status of the SensorHub Channel.

| Symbol                                | Meaning                                       |  |  |  |

|---------------------------------------|-----------------------------------------------|--|--|--|

| PIPE STATUS                           | SensorHub Channel status (see section 5.3.20) |  |  |  |

| PIPE DATA                             | SensorHub Channel data (see section 5.3.21)   |  |  |  |

| Table 45: "Dead Dinaling" transaction |                                               |  |  |  |

Table 15: "Read Pipeline" transaction

| spipipe_sel  |             |           |  |

|--------------|-------------|-----------|--|

| spipipe_clk  |             |           |  |

| spipipe_miso | PIPE STATUS | PIPE DATA |  |

Figure 13: "Read Pipeline" transaction

#### 4.3. Control signals

Various control signals are available between the DSL Master and the frequency inverter application to configure the performance of the IP Core or to carry out fast monitoring of the IP Core status.

#### 4.3.1. SYNC signal

sync is a DSL Master digital input.

One edge on this pin triggers a position sampling. The polarity of the edge can be programmed using the **SPOL** bit in the **SYS\_CTRL** (00h) register. The protocol requires a constant frequency of the signal at this pin, with deviations permitted within a set tolerance band. At start-up, the protocol synchronizes the protocol frame with the signal frequency at sync.

If the sync signal frequency is outside the tolerance range, re-synchronization of the protocol is triggered. During the time that the re-synchronization is taking place, sampling is carried out with the former sync frequency until the re-synchronization is complete. For more details on the sync signal also see section 3.2.1.

## 4.3.2. INTERRUPT signal

interrupt is a DSL Master digital output.

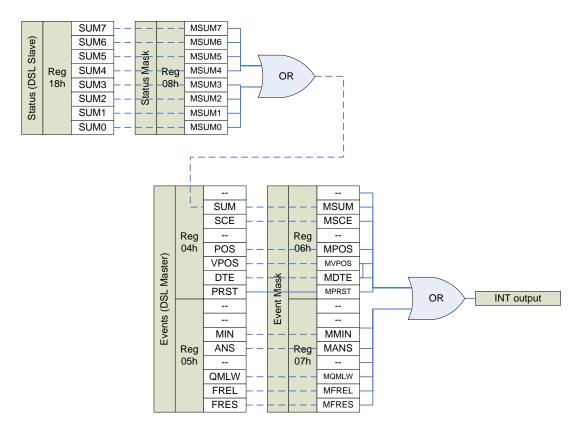

interrupt is set to "1" if an interrupt condition has been fulfilled in the DSL-Master. The interrupt conditions are set using the registers **MASK\_H**, **MASK\_L** and **MASK\_SUM** (see sections 5.3.5 and 5.3.6).

During each write process in one of the registers **EVENT\_H** or **EVENT\_L**, the interrupt output is triggered until the current SPI transaction has ended.

#### 4.3.3. LINK signal

link is a DSL Master digital output.

link reflects the content of the LINK bit in the **MASTER\_QM** register (see section 5.3.3) and therefore indicates whether the DSL Master has produced a communications link to a connected HIPERFACE  $DSL^{\text{®}}$  motor feedback system.

link is intended to be a control signal for an LED display, but can also be used to control the start-up performance (see section 6.1) or for global error handling.

link is reset if communication faults are detected.

#### 4.3.4. FAST\_POS\_RDY signal

fast pos rdy is a DSL Master digital output.

fast\_pos\_rdy signals that a new fast position value is available and permits an event-based reading of the position for incorporating latency reduction.

$fast_pos_rdy$  is always available, even if the position value is invalid or no connection to the encoder has been established.

The timing is according to the figure 14 below.

Figure 14: fast\_pos\_rdy indication.

Dependent upon the configuration in the register system control (see section 5.3.1), fast\_pos\_rdy displays either only the availability of positions based on user requirements (edge at sync input) or all transmitted positions.

#### 4.3.5. SYNC\_LOCKED signal

sync locked is a DSL Master digital output.

sync\_locked indicates whether the sync signal was correctly passed to the encoder, or whether the IP Core is still in a synchronization phase. sync\_locked drops to "0" when the provided sync is more than two clock cycles earlier or later than expected.

#### 4.3.6. BIGEND signal

bigend is a DSL Master digital input.

The byte sequence of the address allocation for registers can be influenced via bigend (see section 8.1.4). The byte sequence is based on 32 bit-wide data words. The selection influences the allocation independently of the interface block used.

Table 16 below lists the selection options for bigend.

| Value | Address allocation byte sequence |

|-------|----------------------------------|

| 0     | Little endian                    |

| 1     | Big endian                       |

Table 16: bigend selection.

## 4.4. Test signals

To support development or fault-finding for controllers that have a DSL interface integrated, the DSL Master supplies some test signals.

#### 4.4.1. SAMPLE signal

sample is a DSL Master digital output.

The sample signal is set at the sampling time point of each bit that is transmitted from the DSL motor feedback system. It consists of 50 pulses from Channel 1 followed by a bit pause and 10 pulses from Channel 2 of the motor feedback system.

#### Figure 15: Sample signal

The sample signal can be used for eye diagrams to measure time and voltage margins during signal transmission.

When making the evaluation, signal delays in the DSL Master must be taken into account. The rising edge of the sample signal is offset by 40 ns from the line driver signal. The time delay of the line driver must also be taken into account. Typically this is 13 ns.

#### 4.4.2. ESTIMATOR\_ON signal

estimator on is a DSL Master digital output.

The estimator\_on signal is set if some event leads to the transmitted fast position (see 5.3.11) being invalid and the position estimator supplying the values. Such events are:

- The DSL motor feedback system reporting a position error

- A coding error in transmission of the fast position

- A check-sum error in transmission of the fast position

- Realignment from fast to safe position

- The protocol is re-synchronizing following a break in the link

The <code>estimator\_on</code> signal can be used to carry out a statistical analysis of the incidence of errors in the DSL system. For more information, please refer to section 6.3.1.

## 4.4.3. DEV\_THR\_ERR signal

dev thr err is a DSL Master digital output.

If the fast position from the process data channel cannot be calculated (either due to transmission or due to sensor errors), estimation is made by the DSL Master based on the last two available position values of the Safe Channel. The worst case deviation from the actual mechanical position is also provided, referring to a user-defined parameter for the maximum possible acceleration in the application (fast position acceleration boundary, see section 5.3.24).

A threshold can be set up for a worst case deviation to raise the dev\_thr\_err output. The threshold is a user defined parameter for the maximum tolerable deviation in the application (fast position estimator deviation, see section 5.3.25).

dev\_thr\_err indicates whether the maximum tolerable deviation is violated ('1') or kept ('0').

#### 4.4.4. SAFE\_CHANNEL\_ERR signal

safe\_channel\_err is a DSL Master digital output.

The safe\_channel\_err signal is set if some event leads to the safe position (see 5.3.14) being invalid. Such events are:

- A coding error in transmission of the safe position

- A check-sum error in transmission of the safe position

The <code>safe\_channel\_err</code> signal can be used to carry out a statistical analysis of the incidence of errors in the DSL system.

#### 4.4.5. SAFE\_POS\_ERR signal

safe\_pos\_err is a DSL Master digital output.

safe\_pos\_err is a DSL Master digital output. The safe\_pos\_err signal is set if the safe position of Safe Channel 1 is not updated or it has never been written since the startup. Another possible cause can be the DSL motor feedback system reporting a position error.

#### 4.4.6. ACCELERATION\_ERR signal

acceleration err is a DSL Master digital output.

The acceleration\_err signal is set if an encoding error was detected after transmission of a fast position value.

If the acceleration\_err signal is set the error counter acc\_err\_cnt will be incremented with each transmission (see section 5.3.23). As soon as the acceleration\_err signal is reset the error counter acc\_err\_cnt will be set to "0" again.

#### 4.4.7. ACC\_THR\_ERR signal

acc thr err is a DSL Master digital output.

The <code>acc\_thr\_err</code> signal is set if the threshold programmed in register <code>acc\_err\_cnt</code> is exceeded.

The  $acc_thr_err$  signal can be used to implement a fault-tolerant evaluation in the drive. For this the maximum position deviation can be calculated from the number of transmission errors.

#### 4.4.8. ENCODING\_ERR signal

encoding\_err is a DSL Master digital output.

The encoding\_err signal is set if the underlying 8B/10B encoding of a DSL frame transmission is disturbed.

The encoding\_err signal can be used to make a statistical analysis of the bit error rate of a DSL system.

# 5. Register diagram

All IP Core registers and functions can be accessed via drive interface. As an option, the SensorHub Channel data is accessible via the SPI PIPE interface.

In addition, the DSL Slave interface registers are mirrored as decentralized registers. The address area 40h to 7Fh is intended for this. The addressing of these registers is identical to the addressing of the registers in the DSL Master. The answer to the transaction is, however, delayed and must be read individually (see under "Short message", in section 6.5.1).

Figure 16 below shows via which interface a connection to which register block is established.

Figure 16: Register block overview

## 5.1. Explanation of the registers

In the following description of the registers, symbols are used to describe the standard value of a bit following a reset. Additional symbols are used to describe the functions provided to the frequency inverter application for this bit.

The bit is described according to the following example:

"Function" "Reset value", e.g. "R/W-0"

| Function symbol | Meaning                                      |

|-----------------|----------------------------------------------|

| R               | Bit can be read.                             |

| W               | Bit can be set and deleted.                  |

| С               | Bit can only be deleted.                     |

| Х               | Bit is not installed and will always be read |

|                 | as "0".                                      |

Table 17: Function symbols for bits

| Reset value | Meaning                                      |  |  |  |

|-------------|----------------------------------------------|--|--|--|

| 0           | The bit is deleted after a reset.            |  |  |  |

| 1           | The bit is set after a reset.                |  |  |  |

| Х           | After a reset, the bit has no defined value. |  |  |  |

| -           | In the register diagram:                     |  |  |  |

|             | The bit is not installed and will always be  |  |  |  |

|             | read as "0".                                 |  |  |  |

Table 18: Symbols for bit reset values

It should be noted that read access to a bit that can only be written ("W") always returns the value "0". If a register address that is not used is read, the result will be "0" as well.

# 5.2. Online Status

The Online Status is a non-storing copy of registers **EVENT\_H** and **EVENT\_L**. The static information in these registers must be deleted by the user after the read process, by writing the value "0" to the corresponding bit in the register, whilst the Online Status only shows the current status without storing previous indications. The signal name of the Online Status is online status d (with d indicating drive).

online\_status\_d is given in two bytes. If an SPI block is used for interfacing the IP Core, online\_status\_d is transmitted in each transaction in the first two bytes via the spi\_miso output. When a parallel bus interface is used for drive interface, online\_status\_d has 16 dedicated output signals available.

It should be noted that when the parallel bus interface is used the 16 signals of the Online Status are not frozen during a read access. If required, the user can insert a Latch (e.g. using the hostd f signal).

#### Online Status , High Byte

| R-0   | R-0 | R-1 | R-1  | R-1 | R-1  | R-1 | R-1   |

|-------|-----|-----|------|-----|------|-----|-------|

| INT   | SUM | SCE | FIX1 | POS | VPOS | DTE | PRST  |

| Bit 7 |     |     |      |     |      |     | Bit 0 |

Bit 7 INT: Status of the Interrupt output This bit represents an exception to the Online Status, as this bit does not relate to an event indication. INT provides the value of the physical INT output so that request management (polling) can be established. The importance of this flag depends on the Interrupt sources monitored.

1 = interrupt output on "High" level 0 = interrupt output on "Low" level

Bit 6 SUM: Summary byte 1 = The last valid value from SUMMARY was not zero. The importance of this flag depends on the particular error source that leads to a set SUMMARY (see section 5.3.13).

0 = The last valid value from **SUMMARY** was zero.

| HIPERFACE DSL <sup>®</sup> |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit 5                      | <ul> <li>SCE: CRC error on the Safe Channel</li> <li>1 = The last Safe Channel CRC received was wrong. It is expected that the last safe position transmitted (see section 5.3.15) is invalid.</li> <li>0 = The last Safe Channel CRC received was correct.</li> </ul>                                                                               |  |  |  |  |  |

| Bit 4                      | <b>FIX1</b> : This bit always gives a "1". For SPI interfaces, this is used for checking the spi_miso pin for stuck-at- '0' faults.                                                                                                                                                                                                                  |  |  |  |  |  |

| Bit 3                      | <b>POS</b> : Estimator turned on<br>1 = A source of an error in the fast position was identified or an<br>alignment procedure is currently being carried out. It is probable<br>that the last fast position is invalid. Be aware that the fast<br>position read through drive interface is provided by the estimator.<br>0 = No fast position error. |  |  |  |  |  |

| Bit 2                      | <b>VPOS</b> : Safe position invalid<br>1 = An error in the safe position was identified. It is expected<br>that the safe position transmitted from the encoder is invalid.<br>0 = The last safe position received was correct.                                                                                                                       |  |  |  |  |  |

| Bit 1                      | <b>DTE</b> : Deviation Threshold Error (see section 4.4.3)                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                            | 1 = Current value of deviation greater than the specified maximum.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                            | 0 = Current value of deviation smaller than the specified maximum.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Bit 0                      | <ul> <li><b>PRST</b>: Protocol reset</li> <li>1 = IP-Core has restarted the protocol.</li> <li>0 = IP-Core running.</li> </ul>                                                                                                                                                                                                                       |  |  |  |  |  |

|                            | Online Status , Low Byte                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                            | X-0         X-0         R-0         R-0         R-1         R-0         R-0           POSTX         MIN         ANS         FIX0         QMLW         FREL         FRES           Bit 7         Bit 0         Bit 0         Bit 0         Bit 0         Bit 0         Bit 0                                                                          |  |  |  |  |  |

| Bit 7-6                    | <ul> <li>POSTX1:POSTX0: Position transmission status</li> <li>00: Position request is transmitted to the DSL encoder.</li> <li>01: Safe Channel was correctly transmitted.</li> <li>10: Fast position present (see section 5.3.11).</li> <li>11: Safe Channel 2 was correctly transmitted.</li> </ul>                                                |  |  |  |  |  |

| Bit 5                      | <ul> <li>MIN: Acknowledgment of message initialization</li> <li>1 = The DSL encoder sends a figure by which the initialization of the Parameter Channel is acknowledged.</li> <li>0 = Parameter Channel not functioning.</li> </ul>                                                                                                                  |  |  |  |  |  |

| Bit 4                      | <b>ANS</b> : Incorrect answer detected.<br>1 = The last answer to a long message was damaged.                                                                                                                                                                                                                                                        |  |  |  |  |  |

- 0 = No error detected in the last answer to a long message.

- Bit 3 **FIX0**: This bit always gives a "0". For SPI interfaces, this is used for checking the spi\_miso pin for stuck-at-'1' faults.

| HIP | ERF | ACE | DSL® |

|-----|-----|-----|------|

|     |     |     |      |

| Bit 2 | <b>QMLW</b> : Quality monitoring at Low level (see section 5.3.3)<br>1 = Current value of quality monitoring less than 14.<br>0 = Current value of quality monitoring greater than or equal to 14. |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 1 | <ul><li>FREL: Channel status for "long message".</li><li>1 = The channel for the "long message" is free.</li><li>0 = The channel for the "long message" is in use.</li></ul>                       |

| Bit 0 | <ul> <li>FRES: Channel status for the "short message".</li> <li>1 = The channel for the "short message" is free.</li> <li>0 = The channel for the "short message" is in use.</li> </ul>            |

#### 5.3. DSL Master function register

The protocol logic controls the performance of the DSL Master via the registers in the DSL Master IP Core on drive interface. These registers are also used for accessing the position values.

The table below contains a list of all the function registers available in the IP Core.

The addresses given below are referencing a big-endian addressing. For a table stating the register addresses depending on the endianness, see section 8.1.4.

| Addr        | Designation | Bit 7  | Bit 6                                                    | Bit 5   | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0  | Valu<br>res |      |

|-------------|-------------|--------|----------------------------------------------------------|---------|----------|---------|---------|---------|--------|-------------|------|

| 00h         | SYS_CTRL    | PRST   | MRST                                                     | FRST    | LOOP     | PRDY    | SPPE    | SPOL    | OEN    | 0000        | 0000 |

| 01h         | SYNC_CTRL   | ES     |                                                          |         |          |         |         |         |        | 0000        | 0001 |

| 03h         | MASTER_QM   | LINK   | -                                                        | -       | -        | Quali   | ty mon  | itoring | a<br>A | 0           | 0000 |

| 04h         | EVENT H     | INT    | SUM                                                      | SCE     | -        | POS     | VPOS    | DTE     | PRST   | 000-        | 0000 |

| 05h         | EVENT L     | -      | -                                                        | MIN     | ANS      | -       | QMLW    | FREL    | FRES   | 00          | -000 |

| 06h         | MASK H      | -      | MSUM                                                     | MVRT    | -        | MPOS    | MVPOS   | MDTE    | MPRST  | -00-        | 0000 |

| 07h         | MASK L      | -      | -                                                        | MMIN    | MANS     | -       | MQMLW   | MFREL   | MFRES  | 00          | -000 |

| 08h         | MASK SUM    | MSUM7  | : 0                                                      |         |          |         |         |         |        | 0000        | 0000 |

| 09h         | EDGES       | Bit sa | ampling                                                  | patter  | rn       |         |         |         |        | 0000        | 0000 |

| 0Ah         | DELAY       | RSSI   |                                                          | -       |          | Cable   | delay   |         |        | 0000        | 0000 |

| 0Bh         | VERSION     | Codino | 1                                                        | IP Co   | re ver   | sion nu | umber   |         |        | 0101        | 0110 |

| 0Dh         | ENC ID2     | -      | SCI                                                      |         |          |         | D19:16  |         |        | -000        | 0000 |

| 0Eh         | ENC ID1     | ENC II |                                                          |         |          |         |         |         |        | 0000        | 0000 |

| OFh         | ENC ID0     | ENC II |                                                          |         |          |         |         |         |        | 0000        |      |

| 10h         | POS4        |        | positio                                                  | n, bvte | e 4      |         |         |         |        | 0000        |      |

| 11h         | POS3        | -      | positio                                                  |         |          |         |         |         |        | 0000        |      |

| 12h         | POS2        | -      | positio                                                  |         |          |         |         |         |        | 0000        |      |

| 13h         | POS1        | -      | positio                                                  | =       |          |         |         |         |        | 0000        |      |

| 14h         | POSO        | -      | positio                                                  | . 1     |          |         |         |         |        | 0000        |      |

| 15h         | VEL2        | -      | byte                                                     | =       |          |         |         |         |        | 0000        |      |

| 16h         | VEL1        |        | byte<br>byte                                             |         |          |         |         |         |        | 0000        |      |

| 17h         | VELO        |        | byte<br>byte                                             |         |          |         |         |         |        | 0000        |      |