#### **SYLLABUS**

### 1. Introduction to Computers

Basic of Computer, Von Neumann Architecture, Generation of Computer, Classification of Computers, Instruction Execution

### 2. Register Transfer and Micro operations

Register Transfer, Bus and Memory Transfers, Tree-State Bus Buffers, Memory Transfer, Micro-Operations, Register Transfer Micro-Operations, Arithmetic Micro-Operations, Logic Micro-Operations, Shift Micro-Operations.

### 3. Computer Arithmetic

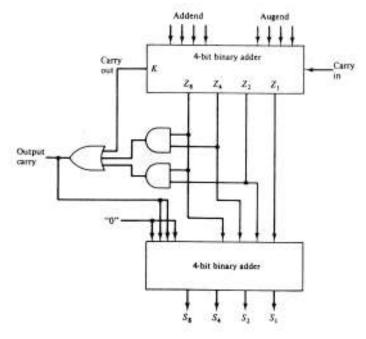

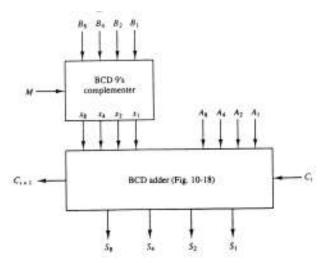

Addition And Subtraction With Signed-Magnitude, Multiplication Algorithm, Booth Multiplication Algorithm, Array Multiplier, Division Algorithm, Hardware Algorithm, Divide Overflow, Floating-Point Arithmetic Operations, Basic Considerations, Register Configuration, Addition And Subtraction, Decimal Arithmetic Operations, BCD Adder, BCD Subtraction.

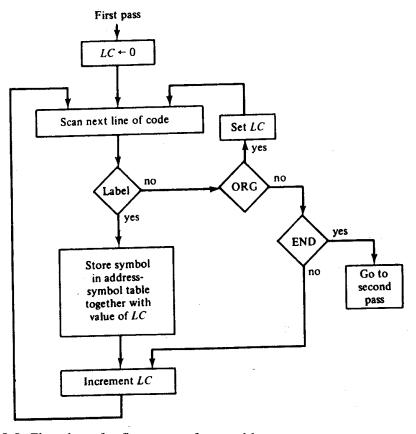

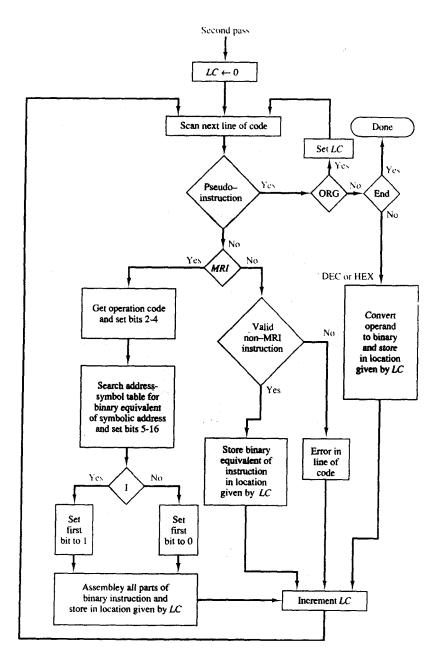

# 4. Programming the Basic Computer

Machine language, Assembly language, Assembler, First pass, Second pass, Programming Arithmetic and Logic operations, Multiplication Program, Double-Precision Addition, Logic operations, Shift operations.

### 5. Organization of a Computer

Central Progressing Unit (CPU), Stack Organization, Register Stack, Memory Stack, Reverse Polish Notation. Instruction Formats, Three- Address Instructions, Two – Address Instructions, One- Address Instructions, Zero-Address Instructions, RISC Instructions, Addressing Modes Reduced Instruction Set Computer, CISC Characteristics RISC Characteristics.

#### 6. Input-Output Organization

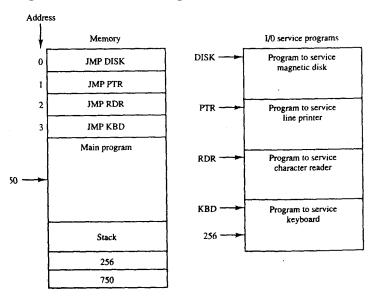

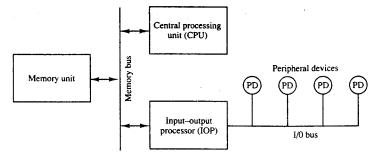

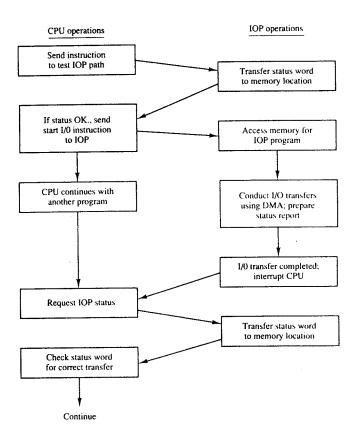

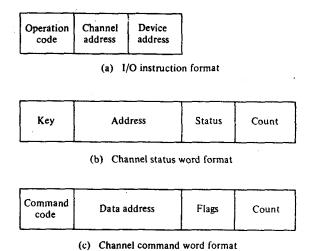

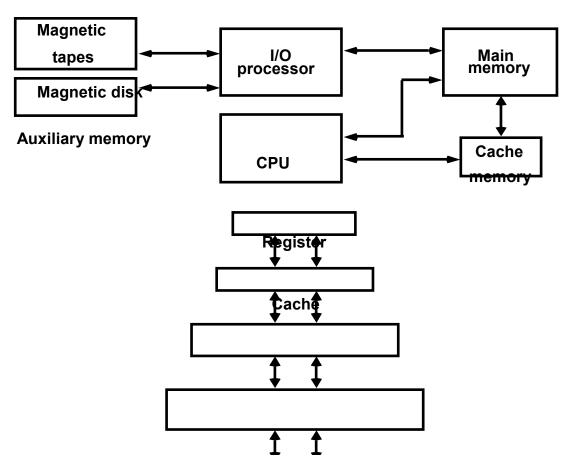

Modes Of Transfer, Priority Interrupt, DMA, Input-Output Processor (IOP), CPU-IOP Communication.

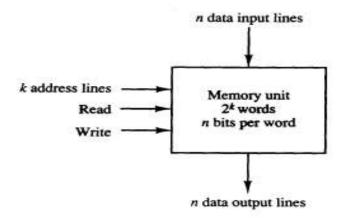

### 7. Memory Organization

Memory Hierarchy, Main Memory, Auxiliary Memory, Cache Memory, Virtual Memory. Address Space and Memory Space, Associative Memory, Page Table, Page Replacement.

### 8. Parallel Processing and Vector Processing

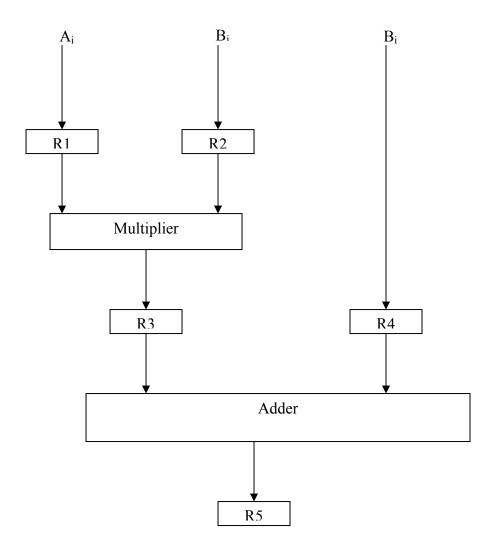

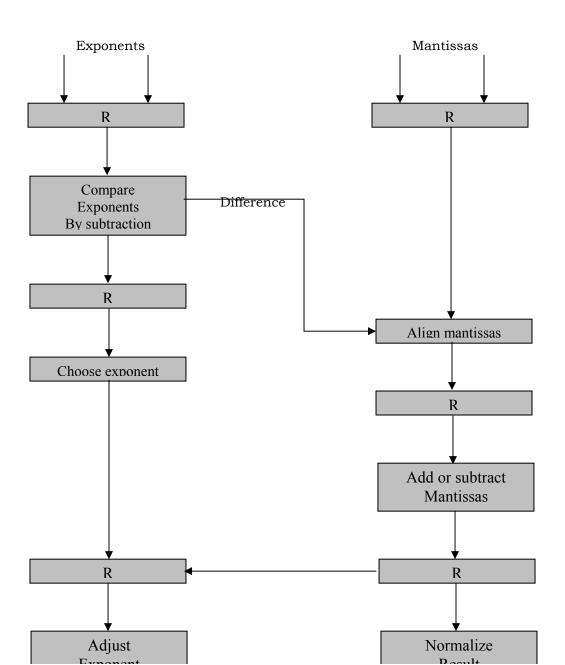

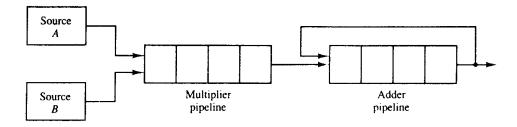

Pipelining, Parallel Processing, Pipelining General Consideration, Arithmetic Pipeline Instruction Pipeline, Vector Operations, Matrix Multiplication, Memory Interleaving.

### 9. Multiprocessors

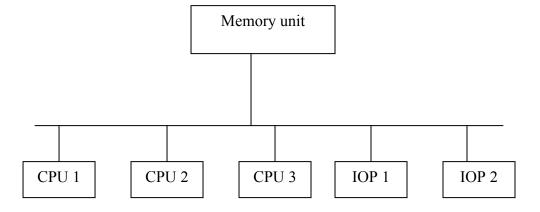

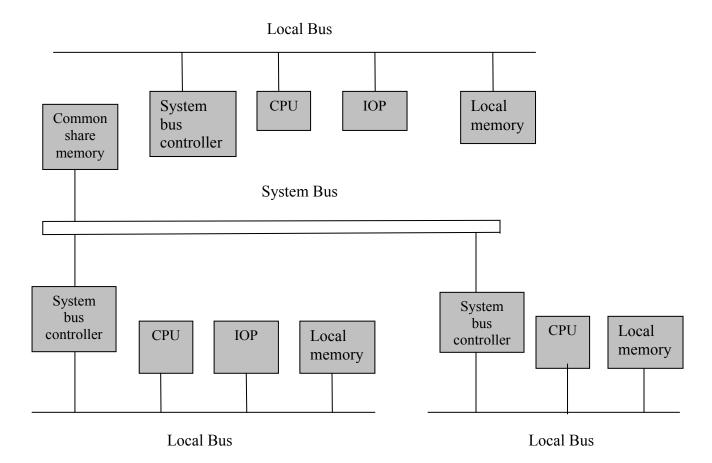

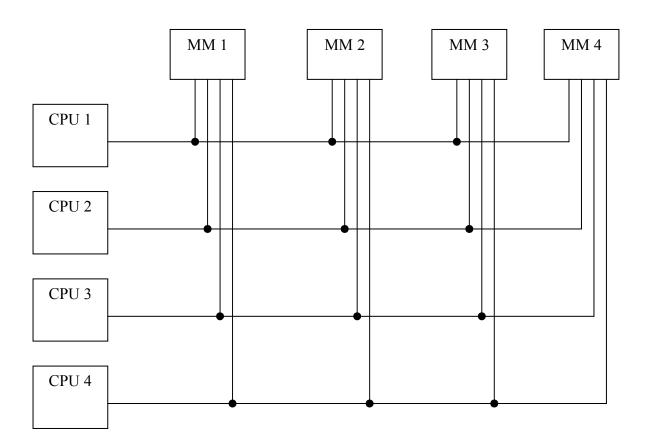

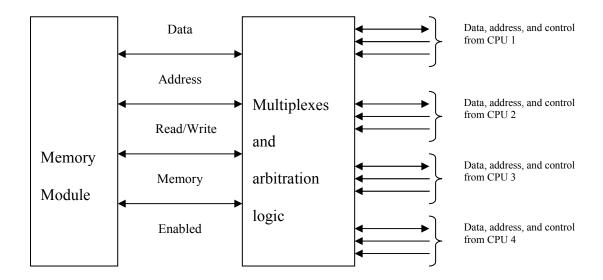

Characteristics of Multiprocessors, Interconnection Structure

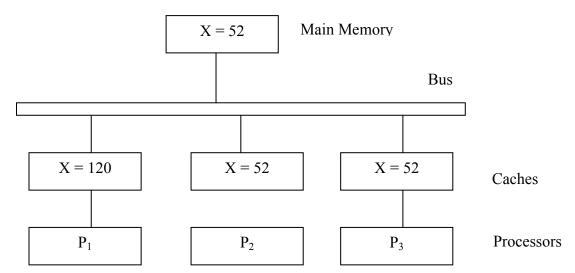

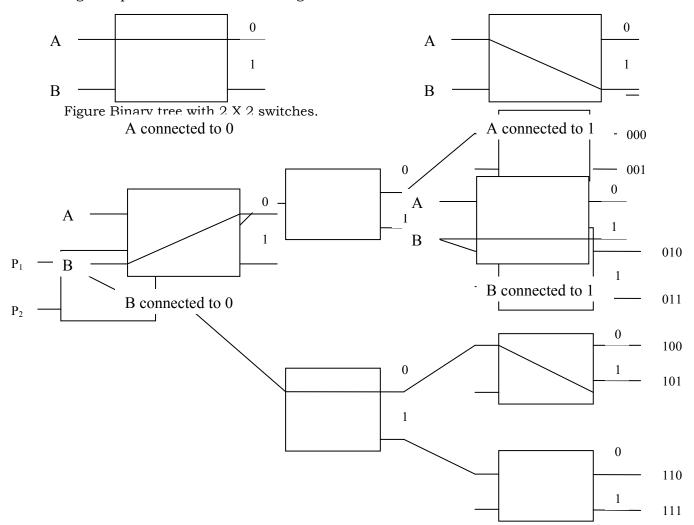

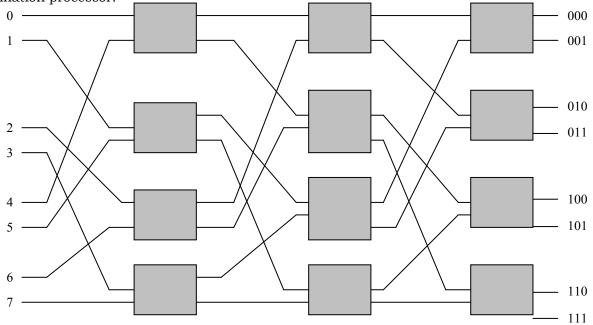

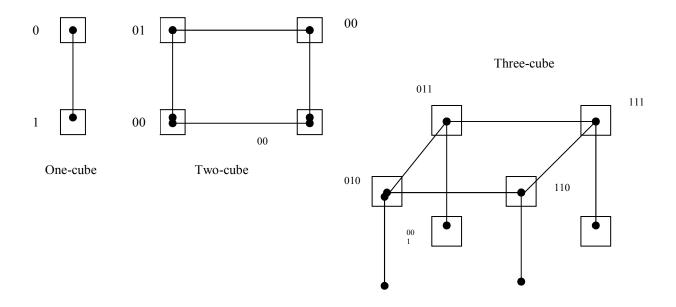

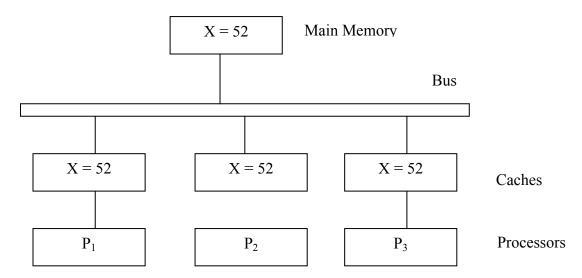

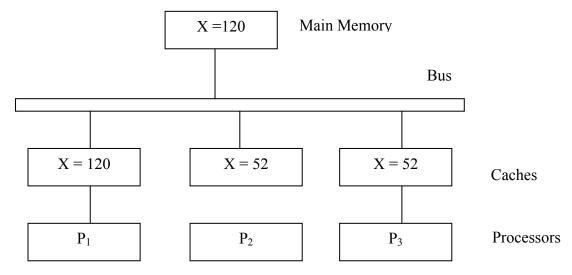

Time-Shared Common Bus, Multi-Port Memory, Crossbar Switch, Multistage Switching Network, Hypercube Interconnection, Inter Processor Arbitration, Cache Coherence

#### References: -

- 1. "Computer System Architecture", John. P. Hayes.

- 2. "Computer Architecture and parallel Processing", Hwang K. Briggs.

- 3. "Computer System Architecture", M.Morris Mano.

#### **SYLLABUS**

### **Introduction to Computers**

Basic of Computer, Von Neumann Architecture, Generation Of Computer, Classification Of Computers, Instruction Execution.

## Register Transfer and Micro operations

Register transfer, Bus and Memory Transfers, tree-state bus buffers, Memory transfer, Micro-Operations , Register transfer Micro-Operations, Arithmetic Micro-Operations , Logic Micro-Operations, Shift Micro-Operations.

#### **Computer Arithmetic**

Addition and subtraction with signed-magnitude, Multiplication algorithm, Booth multiplication algorithm, Array multiplier, Division algorithm, Hardware algorithm, Divide Overflow, Floating-point Arithmetic operations,

Basic considerations, Register configuration, Addition and subtraction, Decimal Arithmetic operations, BCD adder, BCD subtraction.

#### **Programming the Basic Computer**

Machine language, Assembly language, Assembler, First pass, Second pass, Programming Arithmetic and Logic operations, Multiplication Program, Double-Precision Addition, Logic operations, Shift operations,.

### Organization of a Computer

Central Progressing Unit (CPU), Stack organization, Register stack, Memory stack, Reverse polish notation .Instruction Formats, Three- address Instructions, Two – address instructions, One- address instructions, Zero-address instructions, RISC Instructions, Addressing Modes Reduced Instruction Set Computer, CISC characteristics RISC characteristics.

#### **Input-Output Organization**

Modes of transfer, Priority interrupt, DMA, Input-Output Processor (IOP), CPU-IOP Communication.

### **Memory Organization**

Memory hierarchy, Main memory, Auxiliary memory, Cache memory, Virtual memory. Address Space and Memory Space, Associative memory, Page table Page Replacement.

# **Introduction to Parallel Processing**

Pipelining, Parallel processing, Pipelining general consideration, Arithmetic pipeline Instruction pipeline.

# **Vector Processing**

Vector operations, Matrix multiplication, Memory interleaving.

### Multiprocessors

Characteristics of multiprocessors, Interconnection structure

Time-shared common bus, Multi-port memory ,Crossbar switch ,Multistage switching network, Hypercube interconnection, Inter processor arbitration , Cache coherence

### TABLE OF CONTENTS

| Unit 1 | : | Introduction | to | <b>Computers</b> |

|--------|---|--------------|----|------------------|

|--------|---|--------------|----|------------------|

- 1.1 Introduction

- 1.2 What Is Computer

- 1.3 Von Neumann Architecture

- 1.4 Generation Of Computer

- 1.4.1 Mechanical Computers (1623-1945)

- 1.4.2 Pascaline

- 1.4.3 Difference Engine

- 1.4.4 Analytical Engine

- 1.4.5 Harvard Mark I And The Bug

- 1.4.6 First Generation Computers (1937-1953)

- 1.4.7 Second Generation Computers (1954-1962)

- 1.4.8 Third Generation Computers (1963-1972)

- 1.4.9 Fourth Generation Computers (1972-1984)

- 1.4.10 Fifth Generation Computers (1984-1990)

- 1.4.11 Later Generations (1990 -)

- 1.5 Classification Of Computers

- 1.5.1 Micro Computer

- 1.5.2 Mini Computer

- 1.5.3 Mainframe Computer

- 1.5.4 Super Computer

# Unit 2: Register Transfer and Micro operations

- 2.1 Register transfer

- 2.2 Bus and Memory Transfers

- 2.2.1 tree-state bus buffers

- 2.2.2 Memory transfer

- 2.3 Micro-Operations

- 2.3.1 Register transfer Micro-Operations

- 2.3.2 Arithmetic Micro-Operations

- 2.3.3 Logic Micro-Operations

- 2.3.4 Shift Micro-Operations

# **Unit 3: Programming elements**

- 3.1 Computer Arithmetic

- 3.2 Addition and subtraction with signed-magnitude

- 3.3 Multiplication algorithm

- 3.1.1 Booth multiplication algorithm

- 3.1.2 Array multiplier

|             | 323             | Division algorithm                                |

|-------------|-----------------|---------------------------------------------------|

|             | 0.2.0           | 3.2.3.1 Hardware algorithm                        |

|             |                 | 3.2.3.2 Divide Overflow                           |

| 3.4         | Floating_       | point Arithmetic operations                       |

| 0,4         |                 | Basic considerations                              |

|             |                 | Register configuration                            |

|             |                 | Addition and subtraction                          |

| 3.5         |                 |                                                   |

| 3.5         |                 | Arithmetic operations BCD adder                   |

|             |                 | BCD adder BCD subtraction                         |

| IInit 4 . I |                 | ng the Basic Computer                             |

| 4.1         | Machine Machine | _                                                 |

| 4.1         |                 |                                                   |

| 4.2         | Assemble        | language                                          |

| 4.3         | 11000111010     | -                                                 |

|             |                 | First pass                                        |

| 1 1         |                 | Second pass                                       |

| 4.4         |                 | ning Arithmetic and Logic operations              |

|             |                 | Multiplication Program  Double-Precision Addition |

|             |                 |                                                   |

|             |                 | Logic operations                                  |

| TT =        |                 | Shift operations                                  |

|             |                 | ogressing Unit (CPU)                              |

| 5.1         | _               | ganization                                        |

|             | 5.1.1           | 8                                                 |

|             | 5.1.2           | •                                                 |

| ۲.0         | 5.1.3           | P                                                 |

| 5.2         |                 | on Formats                                        |

|             | 5.2.1           |                                                   |

|             | 5.2.2           |                                                   |

|             | 5.2.3           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0               |

|             | 5.2.4           | Zero-address instructions                         |

| <b>5</b> 0  | 5.2.5           |                                                   |

| 5.3         | Addressin       | •                                                 |

| 5.4         |                 | Instruction Set Computer                          |

|             | 5.4.1           | CISC characteristics                              |

|             | 5.4.2           | 11100 0114140101101100                            |

|             |                 | t Organization                                    |

| 6.1         | Modes of        |                                                   |

|             | 6.1.1           | Programmed I/O                                    |

|             | 6.1.2           | ,                                                 |

| 6.2         | Priority i      | <u>-</u>                                          |

|             | 6.2.1           | Daisy-chaining priority                           |

|             | 6.2.2           | Parallel priority interrupt                       |

|             | 6.2.3           | Interrupt cycle                                   |

| 6.3            | DMA         |                                  |

|----------------|-------------|----------------------------------|

|                | 6.3.1       | DMA Controller                   |

|                | 6.3.2       | DMA Transfer                     |

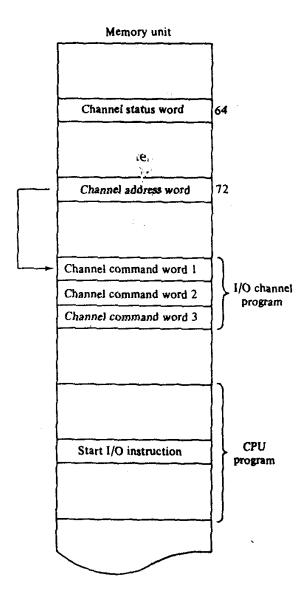

| 6.4            | Input-O     | utput Processor (IOP)            |

|                | 6.1.1       | CPU-IOP Communication            |

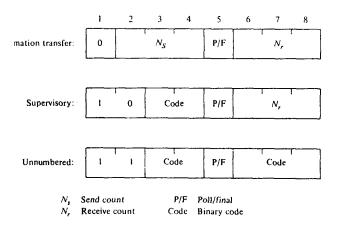

|                | 6.1.2       | Serial Communication             |

|                | 6.1.3       | Character-Oriented Protocol      |

|                | 6.1.4       | Bit-Oriented Protocol            |

| 6.5 Mo         | des of trar | nsfer                            |

| Unit-7 Me      | mory Org    | anization                        |

| 7.1            |             | hierarchy                        |

| 7.2            | Main m      |                                  |

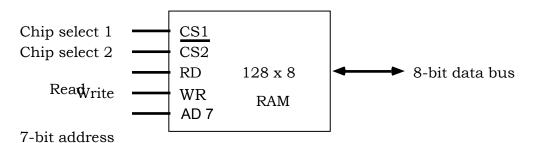

|                |             | RAM and ROM chips                |

|                | 7.2.2       | <del>-</del>                     |

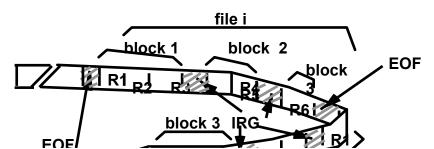

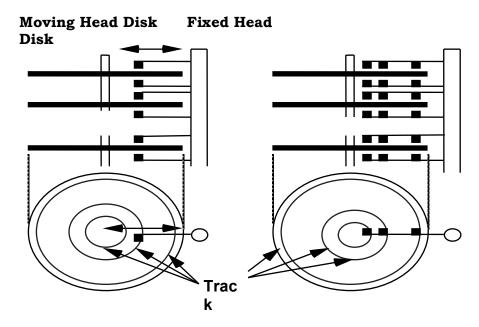

| 7.3            | Auxiliar    | ry memory                        |

|                |             | Magnetic disks                   |

|                | 7.3.2       |                                  |

| 7.4            | Cache r     | nemory                           |

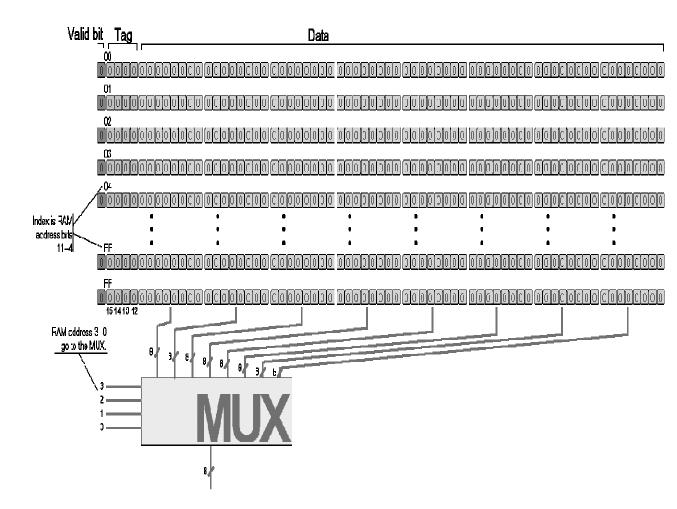

|                | 7.4.1       | Direct Mapping                   |

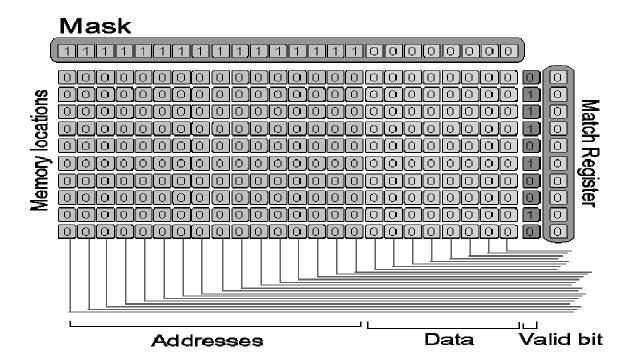

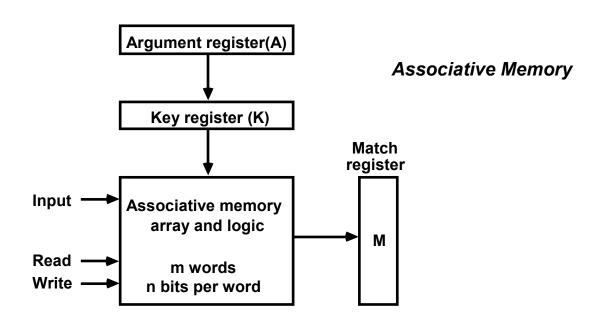

|                | 7.4.2       | Associative Mapping              |

|                | 7.4.3       | Set- associative Mapping         |

|                | 7.4.4       | Virtual memory                   |

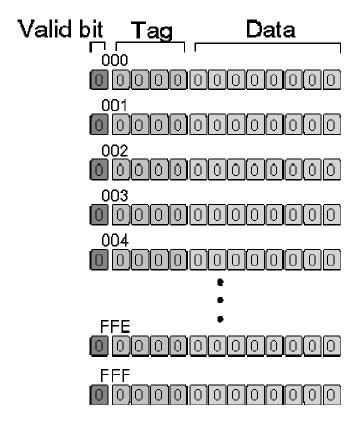

|                | 7.4.5       | Associative memory Page table    |

|                | 7.4.6       | Page Replacement                 |

| <b>UNIT 8:</b> | Introducti  | ion to Parallel Processing       |

| 8.1            | Pipelii     | ning                             |

|                | 8.1.1       | Parallel processing              |

|                | 8.1.2       | Pipelining general consideration |

|                | 8.1.3       | Arithmetic pipeline              |

|                | 8.1.4       | Instruction pipeline             |

| Unit 9: V      | ictor Proc  | essing                           |

| 9.1            | Vector      | operations                       |

| 9.2            |             | multiplication                   |

| 9.3            | Memo        | ry interleaving                  |

| UNIT 10:       | Multipro    | cess                             |

| 10.1           |             | teristics of multiprocessors     |

| 10.2           | Interco     | nnection structure               |

|                | 10.2.1      | Time-shared common bus           |

|                | 10.2.2      | Multi-port memory                |

|                | 10.2.3      | Crossbar switch                  |

|                | 10.2.4      | Multistage switching network     |

|                | 10.2.5      | Hypercube interconnection        |

- 10.3 Inter processor arbitration

- 10.4 Cache coherence

- 10.5 Instruction Execution

#### UNIT 1

#### INTRODUCTION TO COMPUTERS

Computer: An Introduction

- 1.1 Introduction

- 1.2 What Is Computer

- 1.3 Von Neumann Architecture

- 1.4 Generation Of Computer

- 1.4.1 Mechanical Computers (1623-1945)

- 1.4.2 Pascaline

- 1.4.3 Difference Engine

- 1.4.4 Analytical Engine

- 1.4.5 Harvard Mark I And The Bug

- 1.4.6 First Generation Computers (1937-1953)

- 1.4.7 Second Generation Computers (1954-1962)

- 1.4.8 Third Generation Computers (1963-1972)

- 1.4.9 Fourth Generation Computers (1972-1984)

- 1.4.10 Fifth Generation Computers (1984-1990)

- 1.4.11 Later Generations (1990 -)

- 1.5 Classification Of Computers

- 1.5.1 Micro Computer

- 1.5.2 Mini Computer

- 1.5.3 Mainframe Computer

- 1.5.4 Super Computer

#### 1.1 Introduction

Computer is one of the major components of an Information Technology network and gaining increasing popularity. Today, computer technology has permeated every sphere of existence of modern man. In this block, we will introduce you to the computer hardware technology, how does it work and what is it? In addition we will also try to discuss some of the terminology closely linked with Information Technology and computers.

#### 1.2 WHAT IS COMPUTER?

Computer is defined in the Oxford dictionary as "An automatic electronic apparatus for making calculations or controlling operations that are expressible in numerical or

logical terms". A device that accepts data1, processes the data according to the instructions provided by the user, and finally returns the results to the user and usually consists of input, output, storage, arithmetic, logic, and control units. The computer can store and manipulate large quantities of data at very high speed

The basic function performed by a computer is the execution of a **program**. A program is a sequence of instructions, which operates on data to perform certain tasks. In modern digital computers data is represented in binary form by using two symbols 0 and 1, which are called binary digits or bits. But the data which we deal with consists of numeric data and characters such as decimal digits 0 to 9, alphabets A to Z, arithmetic operators (e.g. +, -, etc.), relations operators (e.g. =, >, etc.), and many other special characters (e.g.;,@,{,],etc.). Thus, collection of eight bits is called a byte. Thus, one byte is used to represent one character internally. Most computers use two bytes or four bytes to represent numbers (positive and negative) internally. Another term, which is commonly used in computer, is a Word. A word may be defined as a unit of information, which a computer can process, or transfer at a time. A word, generally, is equal to the number of bits transferred between the central processing unit and the main memory in a single step. It ma also be defined as the basic unit of storage of integer data in a computer. Normally, a word may be equal to 8, 16, 32 or 64 bits .The terms like 32 bit computer, 64 bit computers etc. basically points out the word size of the computer.

#### 1.3 VON NEUMANN ARCHITECTURE

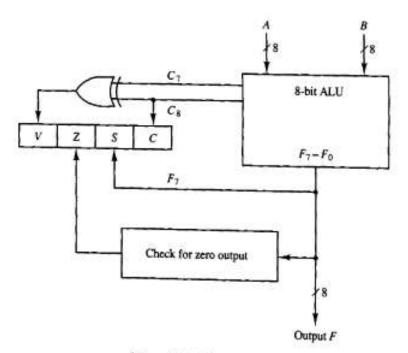

Most of today's computer designs are based on concepts developed by John von Neumann referred to as the **VON NEUMANN ARCHITECTURE**. Von Neumann proposed that there should be a unit performing arithmetic and logical operation on the data. This unit is termed as Arithmetic Logic (**ALU**). One of the ways to provide instruction to such computer will be by connecting various logic components in such a fashion, that they produce the desired output for a given set of inputs. The process of connecting various logic components in specific configuration to achieve desired results is called **Programming**. This programming since is achieved by providing instruction within hardware by various connections is termed as **Hardwired**. But this is a very inflexible process of programming. Let us have a general configuration for arithmetic and logical functions. In such a case there is a need of a control signal, which directs the ALU to performed a specific arithmetic or logic function on the data. Therefore, in such a system, by changing the control signal the desired function can be performed on data.

<sup>&</sup>lt;sup>1</sup> Representation of facts, concepts, or instructions in a formalized manner suitable for communication, interpretation, or processing by humans or by automatic means. Any representations such as characters or analog quantities to which meaning is or might be assigned

Any operation, which needs to be performed on the data, then can be obtained by providing a set of control signals. This, for a new operation one only needs to change the set of control signals.

But, how can these control signals by supplied? Let us try to answer this from the definition of a program. A program consists of a sequence of steps. Each of these steps, require certain arithmetic or logical or input/output operation to be performed on data. Therefore, each step may require a new set of control signals. Is it possible for us to provide a unique code for each set of control signals? Well the answer is yes. But what do we do with these codes? What about adding a hardware segment, which accepts a code and generates termed as Control Unit (CU). This, a program now consists of a sequence of codes. This machine is quite flexible, as we only need to provide a new sequence of codes for a new program. Each code is, in effect, and instruction, for the computer The hardware interprets each of these instructions and generates respective control signals,

The Arithmetic Logic Unit (ALU) and the Control Unit (CU) together are termed as the Central Processing Unit (CPU). The CPU is the moist important component of a computer's hardware. The ALU performs the arithmetic operations such as addition, subtraction, multiplication and division, and the logical operations such as: "Is A =B?" (Where A and B are both numeric or alphanumeric data), "Is a given character equal to M (for male) or F (for female)?" The control unit interprets instructions and produces the respective control signals.

All the arithmetic and logical Operations are performed in the CPU in special storage areas called registers. The size of the register is one of the important consideration in determining the processing capabilities of the CPU. Register size refers to the amount of information that can be held in a register at a time for processing. The larger the register size, the faster may be the speed o processing. A CPU's processing power is measured in Million Instructions Per Second (MIPS). The performance of the CPU was measured in milliseconds (one thousand of a second) on the first generation computers, in microseconds (one millionth of a second) on second-generation computers, and is expected to be measured in Pico-seconds (one 1000th of a nano-second) in the later generations. How can the instruction and data be put into the computers? An external environment supplies the instruction and data, therefore, an input module is needed. The main responsibility of input module will be to put the data in the form of signals that can be recognized by the system. Similarly, we need another component, which will report the results in the results in proper format and form. This component is called output module. These components are referred together as input/output (I/O) components. In addition, to transfer the information, the computer system internally needs the system interconnections. Most common input/output devices are keyboard, monitor and printer, and the most common interconnection structure is the Bus structure.

Are these two components sufficient for a working computer? No, because input devices can bring instructions or data only sequentially and a program may not be executed sequentially as jump instructions are normally encountered in programming. In addition, more than one data elements may be required at a time. Therefore, a temporary storage area is needed in a computer to store temporarily the instructions and the data. This component is referred to as memory. It was pointed out by von-Neumann that the same memory can be used or storing data and instructions. In such cases the data can be treated as data on which processing can be performed, while instructions can be treated as data, which can be used for the generation of control signals.

The memory unit stores all the information in a group of memory cells, also called memory locations, as binary digits. Each memory location has a unique address and can be addressed independently. The contents of the desired memory locations are provided to the central processing unit by referring to the address of the memory location. The amount of information that can be held in the main memory is known as memory capacity. The capacity of the main memory s measured in Kilo Bytes (KB) or Mega Bytes (B). One-kilo byte stands for  $2^{10}$  bytes, which are 1024 bytes (or approximately 1000 bytes). A mega byte stands for  $2^{20}$  bytes, which is approximately little over one million bytes. When 64-bit CPU's become common memory will start to be spoken about in terabytes, petabytes, and exabytes.

- One kilobyte equals 2 to the 10th power, or 1,024 bytes.

- One megabyte equals 2 to the 20th power, or 1,048,576 bytes.

- One gigabyte equals 2 to the 30th power, or 1,073,741,824 bytes.

- One terabyte equals 2 to the 40th power, or 1,099511,627,776 bytes.

- One petabyte equals 2 to the 50th power, or 1,125,899,906,842,624 bytes.

- One exabyte equals 2 to the 60<sup>th</sup> power, or 1,152,921,504,606,846,976 bytes.

- One zettabyte equals 2 to the 70th power, or 1,180,591,620,717,411,303,424

- One yottabyte equals 2 to the 80<sup>th</sup> power, or 1,208,925,819,614,629,174,706,176

*Note:* There is some lack of standardization on these terms when applied to memory and disk capacity. Memory specifications tend to adhere to the definitions above whereas disk capacity specifications tend to simplify things to the 10<sup>th</sup> power definitions (kilo=10<sup>3</sup>, mega=10<sup>6</sup>, giga=10<sup>9</sup>, etc.) in order to produce even numbers.

Let us summarize the key features of a von Neumann machine.

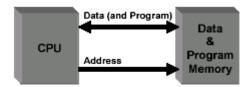

- The hardware of the von Neumann machine consists of a CPU, which includes an ALU and CU.

- A main memory system

- An Input/output system

- The von Neumann machine uses stored program concept, e.g., the program and data are stored in the same memory unit. The computers prior to this idea used

to store programs and data on separate memories. Entering and modifying these programs were very difficult as they were entered manually by setting switches and plugging and unplugging.

- Each location of the memory of von Neumann machine can be addressed independently.

- Execution of instructions in von Neumann machine is carried out in a sequential fashion (unless explicitly altered by the program itself) from one instruction to the next.

The following figure shows the basic structure of von Neumann machine. A von Neumann machine has only a single path between the main memory and control unit (CU). This feature/ constraint is refereed to as von Neumann bottleneck. Several other architectures have been suggested for modern computers

von Neumann Machine

- Attributed to John von Neumann

- Treats Program and Data equally

- One port to Memory . Simplified Hardware

- "von Neumann Bottleneck" (rate at which data and program can get into the CPU is limited by the bandwidth of the interconnect)

### 1.4 HISTORY OF COMPUTERS

Basic information about the technological development trends in computer in the past and its projections in the future. If we want to know about computers completely then we must start from the history of computers and look into the details of various technological and intellectual breakthrough. These are essential to give us the feel of how much work and effort has been done to get the computer in this shape.

The ancestors of modern age computer were the mechanical and electro-mechanical devices. This ancestry can be traced as back and 17th century, when the first machine capable of performing four mathematical operations, viz. addition, subtraction, division and multiplication, appeared.

#### 1.4.1 MECHANICAL COMPUTERS

### 1.4.1.1. Pascaline:

Blaise Pascal made the very first attempt towards this automatic computing. He invented a device, which consisted of lots of gears and chains and used to perform repeated addition and subtractions. This device was called Pascaline. Later many attempts were made in this direction; we will not go in the details of these mechanical calculating devices. But we must discuss some details about the innovation by Charles babbage, the grandfather of modern computer. He designed two computers:

#### 1.4.1.2. THE DIFFERENCE ENGINE

It was based on the mathematical principle of finite differences and was used to solve calculations on large numbers using a formula. It was also used for solving the polynomial and trigonometric functions.

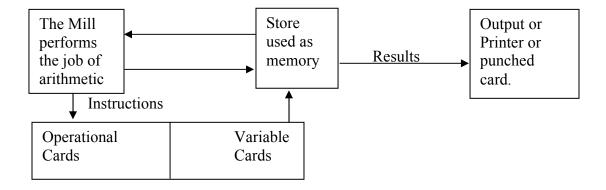

#### 1.4.1.3. THE ANALYTICAL ENGINE BY BABBAGE:

It was general purpose computing device, which could be used for performing any mathematical operation automatically. It consisted of the following components:

- **THE STORE:** A mechanical memory unit consisting of sets of counter wheels.

- **THE MILL:** An arithmetic unit, which is capable of performing the four basic arithmetic operations.

- **CARDS:** There are basically two types of cards:

- o **Operation Cards:** Selects one of four arithmetic operating by activating the mill to perform the selected function.

- Variable Cards: Selects the memory locations to be used by the mill for a particular operation (i.e. the source of the operands and the destination of the results).

- **OUTPUT:** Could be directed to a printer or a cardpunch device.

Logical Structure of Babbage's Analytical Engine

# The basic features of this analytical engine were:

- It was a general purpose programmable machine.

- It had the provision of automatic sequence control, thus enabling programs to alter its sequence of operations.

- The provision of sign checking of result existed.

- Mechanism for advancing or reversing of control card were permitted thus enabling exceution of any desired instruction. In other words, Babbage had deviced a conditional and branching instructions, the babbage machine is fundamentally the same as modern computer. Unfortunately Babbage work could not be completed. But as a tribute to Charles Babbage his Analytical Engine was completed in the last decade and is now on display at the science Museum at London.

Next notable attempts towards computer were electromechanical Zuse used electromechanical relays that could be either opened or closed automatically. Thus, the use of binary digits, rather than decimal numbers started.

#### 1.4.1.4. HARVARD MARK I AND THE BUG

The next significant effort towards devising an electromechanical computer was made at the harvard University, jointly sponsered by IBM and the Department of UN Navy, Howard Aiken of Harvard University developed a system called Mark I in 1944. Mark I was decimal machine.

Some of you must have heard a term call "bug". It is mainly used to indicate errors in computer programs. This term was coined, when one day, a program in Mark I did not run properly due to a short-circuiting the computer. Since then, the "bug" has been linked with errors or problems in computer programming. The process of eliminating error in a program is thus, known as "debugging".

The basic drawback of these mechanical and elecromechanical computers were:

- Friction/inertia of moving components had limited the speed.

- The data movement using gears and liner was quite difficult and unreliable.

- The change was to have switching and storing mechanism with no moving parts and then the electronic switching technique "triode" vacuum tubes were used and hence born the first electronic computer.

- The evolution of digital computing is often divided into *generations*. Each generation is characterized by dramatic improvements over the previous generation in the technology used to build computers, the internal organization of computer systems, and programming languages. Although not usually associated with computer generations, there has been a steady improvement in algorithms, including algorithms used in computational science. The following history has been organized using these widely recognized generations as mileposts.

### 1.4.2 First Generation Electronic Computers (1937-1953)

Three machines have been promoted at various times as the first electronic computers. These machines used electronic switches, in the form of vacuum tubes, instead of electromechanical relays. In principle the electronic switches would be more reliable, since they would have no moving parts that would wear out, but the technology was still new at that time and the tubes were comparable to relays in reliability. Electronic components had one major benefit, however: they could "open" and "close" about 1,000 times faster than mechanical switches.

The first general purpose programmable electronic computer was the Electronic Numerical Integrator and Computer (ENIAC), built by J. Presper Eckert and John V. Mauchly at the University of Pennsylvania. Eckert, Mauchly, and John von Neumann, a consultant to the ENIAC project, began work on a new machine before ENIAC was finished. The main contribution of EDVAC, their new project, was the notion of a *stored program*. There is some controversy over who deserves the credit for this idea, but none over how important the idea was to the future of general purpose computers. ENIAC was controlled by a set of external switches and dials; to change the program required physically altering the settings on these controls. These controls also limited the speed of the internal electronic operations. Through the use of a memory that was large enough to hold both instructions and data, and using the program stored in memory to control the order of arithmetic operations, EDVAC was able to run orders of magnitude faster than ENIAC. By storing instructions in the same medium as data, designers could concentrate on improving the internal structure of the machine without worrying about matching it to the speed of an external control.

The trends, which were encountered during the era of first generation computer, were:

- The first generation computer control was centralized in a single CPU, and all operations required a direct intervention of the CPU.

- Use of ferrite-core main memory was started during this time.

- Concepts such as use of virtual memory and index register (you will know more about these terms in advanced courses).

- Punched cards were used as input device.

- Magnetic tapes and magnetic drums were used as secondary memory.

- Binary code or machine language was used for programming.

- Towards the end due to difficulties encountered in use of machine language as programming language, the use of symbolic language, which is now called assembly language, started.

- Assembler, a program, which translates assembly language programs to machine language, was made.

- Computer was accessible to only one programmer at a time (single user environment).

• Advent of Von-Neumann Architecture.

# 1.4.3 Second Generation (1954-1962)

The second generation saw several important developments at all levels of computer system design, from the technology used to build the basic circuits to the programming languages used to write scientific applications.

Electronic switches in this era were based on discrete diode and transistor technology with a switching time of approximately 0.3 microseconds. The first machines to be built with this technology include TRADIC at Bell Laboratories in 1954 and TX-0 at MIT's Lincoln Laboratory. Memory technology was based on magnetic cores which could be accessed in random order, as opposed to mercury delay lines, in which data was stored as an acoustic wave that passed sequentially through the medium and could be accessed only when the data moved by the I/O interface.

During this second generation many high level programming languages were introduced, including FORTRAN (1956), ALGOL (1958), and COBOL (1959). Important commercial machines of this era include the IBM 704 and its successors, the 709 and 7094. The latter introduced I/O processors for better throughput between I/O devices and main memory.

The second generation also saw the first two supercomputers designed specifically for numeric processing in scientific applications. The term "supercomputer" is generally reserved for a machine that is an order of magnitude more powerful than other machines of its era. Two machines of the 1950s deserve this title. The Livermore Atomic Research Computer (LARC) and the IBM 7030 (aka Stretch) were early examples of machines that overlapped memory operations with processor operations and had primitive forms of parallel processing

#### 1.4.4 Third Generation (1963-1972)

The third generation brought huge gains in computational power. Innovations in this era include the use of integrated circuits, or ICs (semiconductor devices with several transistors built into one physical component), semiconductor memories starting to be used instead of magnetic cores, microprogramming as a technique for efficiently designing complex processors, the coming of age of pipelining and other forms of parallel processing, and the introduction of operating systems and time-sharing.

The first ICs were based on **small-scale integration (SSI) circuits**, which had around 10 devices per circuit (or `chip"), and evolved to the use of **medium-scale integrated** (MSI) circuits, which had up to 100 devices per chip. Multilayered printed circuits were developed and core memory was replaced by faster, solid state memories. Computer designers began to take advantage of parallelism by using multiple functional units, overlapping CPU and I/O operations, and pipelining (internal parallelism) in both the

instruction stream and the data stream. The SOLOMON computer, developed by Westinghouse Corporation, and the ILLIAC IV, jointly developed by Burroughs, the Department of Defense and the University of Illinois, was representative of the first parallel computers.

#### 1.4.5. Fourth Generation (1972-1984)

The next generation of computer systems saw the use of large scale integration (LSI - 1000 devices per chip) and very large scale integration (VLSI - 100,000 devices per chip) in the construction of computing elements. At this scale entire processors will fit onto a single chip, and for simple systems the entire computer (processor, main memory, and I/O controllers) can fit on one chip. Gate delays dropped to about 1ns per gate.

Semiconductor memories replaced core memories as the main memory in most systems; until this time the use of semiconductor memory in most systems was limited to registers and cache. A variety of parallel architectures began to appear; however, during this period the parallel computing efforts were of a mostly experimental nature and most computational science was carried out on vector processors. Microcomputers and workstations were introduced and saw wide use as alternatives to time-shared mainframe computers.

Developments in software include very high level languages such as FP (functional programming) and Prolog (programming in logic). These languages tend to use a declarative programming style as opposed to the imperative style of Pascal, C, FORTRAN, et al. In a **declarative style**, a programmer gives a mathematical specification of what should be computed, leaving many details of how it should be computed to the compiler and/or runtime system. These languages are not yet in wide use, but are very promising as notations for programs that will run on massively parallel computers (systems with over 1,000 processors). Compilers for established languages started to use sophisticated optimization techniques to improve code, and compilers for vector processors were able to vectorize simple loops (turn loops into single instructions that would initiate an operation over an entire vector).

Two important events marked the early part of the third generation: the development of the C programming language and the UNIX operating system, both at Bell Labs. In 1972, Dennis Ritchie, seeking to meet the design goals of CPL and generalize Thompson's B, developed the C language. Thompson and Ritchie then used C to write a version of UNIX for the DEC PDP-11. This C-based UNIX was soon ported to many different computers, relieving users from having to learn a new operating system each time they change computer hardware. UNIX or a derivative of UNIX is now a de facto standard on virtually every computer system.

### 1.4.6 Fifth Generation (1984-1990)

The development of the next generation of computer systems is characterized mainly by the acceptance of parallel processing. Until this time parallelism was limited to pipelining and vector processing, or at most to a few processors sharing jobs. The fifth generation saw the introduction of machines with hundreds of processors that could all be working on different parts of a single program.

Other new developments were the widespread use of computer networks and the increasing use of single-user workstations. Prior to 1985 large scale parallel processing was viewed as a research goal, but two systems introduced around this time are typical of the first commercial products to be based on parallel processing. The Sequent Balance 8000 connected up to 20 processors to a single shared memory module (but each processor had its own local cache). The machine was designed to compete with the DEC VAX-780 as a general purpose Unix system, with each processor working on a different user's job.

The Intel iPSC-1, nicknamed ``the hypercube", took a different approach. Instead of using one memory module, Intel connected each processor to its own memory and used a network interface to connect processors. This distributed memory architecture meant memory was no longer a bottleneck and large systems (using more processors) could be built. Toward the end of this period a third type of parallel processor was introduced to the market. In this style of machine, known as a data-parallel or SIMD, there are several thousand very simple processors. All processors work under the direction of a single control unit; i.e. if the control unit says ``add a to b'' then all processors find their local copy of a and add it to their local copy of b.

Scientific computing in this period was still dominated by vector processing. Most manufacturers of vector processors introduced parallel models, but there were very few (two to eight) processors in this parallel machines. In the area of computer networking, both wide area network (WAN) and local area network (LAN) technology developed at a rapid pace, stimulating a transition from the traditional mainframe computing environment toward a distributed computing environment in which each user has their own workstation for relatively simple tasks (editing and compiling programs, reading mail) but sharing large, expensive resources such as file servers and supercomputers. RISC technology (a style of internal organization of the CPU) and plummeting costs for RAM brought tremendous gains in computational power of relatively low cost workstations and servers. This period also saw a marked increase in both the quality and quantity of scientific visualization.

# 1.4.7. Sixth Generation (1990 - )

This generation is beginning with many gains in parallel computing, both in the hardware area and in improved understanding of how to develop algorithms to exploit diverse, massively parallel architectures. Parallel systems now complete with vector

processors in terms of total computing power and most expect parallel systems to dominate the future.

Combinations of parallel/vector architectures are well established, and one corporation (Fujitsu) has announced plans to build a system with over 200 of its high end vector processors. Workstation technology has continued to improve, with processor designs now using a combination of RISC, pipelining, and parallel processing. As a result it is now possible to purchase a desktop workstation for about \$30,000 that has the same overall computing power (100 megaflops) as fourth generation supercomputers.

One of the most dramatic changes in the sixth generation will be the explosive growth of wide area networking. Network bandwidth has expanded tremendously in the last few years and will continue to improve for the next several years. T1 transmission rates are now standard for regional networks, and the national "backbone" that interconnects regional networks uses T3. Networking technology is becoming more widespread than its original strong base in universities and government laboratories as it is rapidly finding application in K-12 education, community networks and private industry.

#### 1.5 CLASSIFICATION COMPUTERS

#### 1.5.1 MICRO COMPUTER

A microcomputer's CPU is microprocessor. The microcomputer originated in late 1970s. the first microcomputers were built around 8-bit microprocessor chips. It means that the chip can retrieve instructions/data from storage, manipulate, and process an 8-bit data at a time or we can say that the chip has a built-in 8-bit data transfer path. An improvement on 8-bit chip technology was seen in early 1980s, when a series of 16-bit chips namely 8086 and 8088 were introduced by Intel Corporation, each one with an advancement over the other. 8088 is a 8/16 bit chip i.e. an 8-bit path is used to move data between chip and primary storage(external path), at a time, but processing is done within the chip using a 16-bit path(internal path) at a time. 8086 is a 16/16 bit chip i.e. the internal and external paths both are 16 bit wide. Both these chips can support a primary storage capacity of upto 1 mega byte (MB). These computers are usually divided into desktop models and laptop models. They are terribly limited in what they can do when compared to the larger models discussed above because they can only be used by one person at a time, they are much slower than the larger computers, and they cannot store nearly as much information, but they are excellent when used in small businesses, homes, and school classrooms. These computers are inexpensive and easy to use. They have become an indispensable part of modern life. Thus

- Used for memory intense and graphic intense applications

- Are single-user machines

#### 1.5.2 MINI COMPUTER

Minicomputers are much smaller than mainframe computers and they are also much less expensive. The cost of these computers can vary from a few thousand dollars to several hundred thousand dollars. They possess most of the features found on mainframe computers, but on a more limited scale. They can still have many terminals, but not as many as the mainframes. They can store a tremendous amount of information, but again usually not as much as the mainframe. Medium and small businesses typically use these computers. Thus

- Fit somewhere between mainframe and PCs

- Would often be used for file servers in networks

#### 1.5.3. MAINFRAME COMPUTER

Mainframe computers are very large, often filling an entire room. They can store enormous of information, can perform many tasks at the same time, can communicate with many users at the same time, and are very expensive. The price of a mainframe computer frequently runs into the millions of dollars. Mainframe computers usually have many terminals connected to them. These terminals look like small computers but they are only devices used to send and receive information from the actual computer using wires. Terminals can be located in the same room with the mainframe computer, but they can also be in different rooms, buildings, or cities. Large businesses, government agencies, and universities usually use this type of computer. Thus

- Most common type of large computers

- Used by many people using same databases

- Can support many **terminals**

- Used in large company like banks and insurance companies

#### 1.5.4. SUPER COMPUTER

The upper end of the state of the art mainframe machine is the supercomputer. These are amongst the fastest machines in terms of processing speed and use multiprocessing techniques, were a number of processors are used to solve a problem. Computers built to minimize distance between points for very fast operation. Used for extremely complicated computations. Thus

- Largest and most powerful

- Used by scientists and engineers

- o Very expensive

- o Would be found in places like Los Alamos or NASA

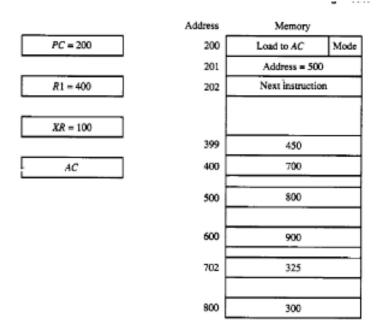

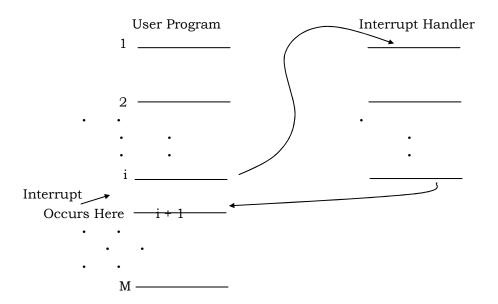

#### 1.6 INSTRUCTION EXECUTION

We know that the basic function performed by a computer is the execution of a program. The program, which is to be executed, is a set of instructions, which are stored in memory. The central processing unit (CPU) executes the instructions of the program to complete a task. The instruction execution takes place in the CPU registers. Let us, first discuss few typical registers, some of which are commonly available in of machines.

These registers are:-

- **Memory Address Register (MAR):-** Connected to the address lines of the system bus. It specifies the address of memory location from which data or instruction is to be accessed (for read operation) or to which the data is to be stored (for write operation).

- **Memory Buffer Register (MBR):-** Connected to the data lines of the system bus. It specifies which data is to be accessed(for read operation) or to which data is to be stored (for write operation).

- **Program Counter (PC):-** Holds address of next instruction to be fetched, after the execution of an on-going instruction.

- **Instruction Register (IR):-** Here the instruction are loaded before their execution or holds last instruction fetched.

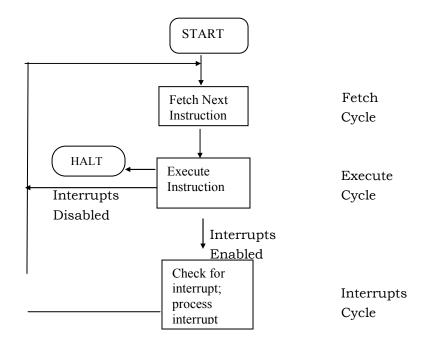

#### **Instruction Cycle**

The simplest model of instruction processing can be a two step process. The CPU reads (fetches) instructions (codes) from the memory one at a time, and executes. Instruction fetch involves reading of an instruction from a memory location to the CPU register. The execution of this instruction may involve several operations depending on the nature of the instruction. Thus to execute an instruction, a processor must go through two subcycles:

#### UNIT-2

#### REGISTER TRANSFER AND MICRO OPERATIONS

- 2.1 Register transfer

- 2.2 Bus and Memory Transfers

- 2.2.1 Tree-state bus buffers

- 2.2.2 Memory transfer

- 2.3 Micro-Operations

- 2.3.1 Register transfer Micro-Operations

- 2.3.2 Arithmetic Micro-Operations

- 2.3.3 Logic Micro-Operations

- 2.3.4 Shift Micro-Operations

#### 2.1 Introduction To Register Transfer

A micro operations is an elementary operation performed on the information stored in one or more registers. The result of the operation may replace the previous binary information of a register or may by transferred to another register.

The symbolic notation used to describe the micro operation transfer among registers is called a register transfer language. The term "register transfer" implies the availability of hardware logic circuits that can perform stated micro operation and transfer the results to the operation to the same or another register.

Register Transfer

We designate computer registers by capital letters to denote the function of the register. For example, the register that holds an address for the memory unit is usually called a memory address register, represented by MAR. Other examples are PC (for program counter), IR (for instruction register) and R1 (for processor register). We show the individual flip-flops in an n-bit register by giving numbers them in sequence from 0 through n-1, starting from 0 in the right most position and increasing the numbers toward the left.

A 16-bit register is divided into two halves. Low byte (Bits 0 through 7) is assigned the symbol L and high byte (Bits 8 through 15) is assigned the symbol H. The name of a 16-bit register is PC. The symbol PC(L) represents the low order byte and PC(H) designates the high order byte. The statement  $R_2 \ \square \ R_1$  refers the transfer of the content of register  $R_1$  into register  $R_2$ . It should be noted that the content of the source register  $R_1$  does not

change after the transfer. In real applications, the transfer occurs only under a predetermined control condition. This can be shown by means of an "if-then" statement: If P=1 then  $R_2 \square \square R_1$

where P is a control signal generated in the control section of the system. For convenience we separate the control variables from the register transfer operation by specifying a control function. A control function is a Boolean variable that is equal to 1 or 0. The control function is written as follows:

$P: R_2 \square \square \square R_1$

Bus

Since a computer has many registers, paths must be provided to transfer information from one register to another. If separate lines are used between each register and all other registers, number of wires will be excessive in the system. A more efficient scheme for transferring information between registers in a multiple-register configuration is a common bus system. A bus structure consists of a set of common lines, one for each bit of a register, through which binary information is transferred one at a time. Control signals determine which register is selected by the bus during each particular register transfer.

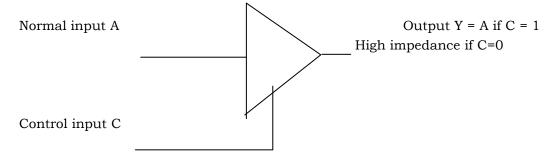

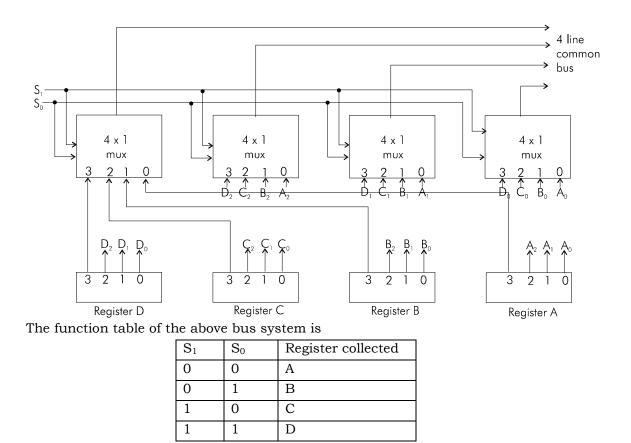

A common bus system can be constructed using multiplexers. These multiplexers select the source register whose binary information is then placed on the bus. A bus system will multiplex registers of a bit each to produce an n-line common bus. The number of multiplexers required to construct the bus is equal to n, where n is the number of bits in each register. The size of each multiplexer must be  $k \times 1$  since it multiplexes k data lines. A bus system can be constructed with 'three-state gates' instead of multiplexers. A three-state gate is a digital circuit that shows three states. Two of the states are equivalent to logic 1 and 0. The third state is a high impedance state. The high-impedance state behaves like an open circuit, which means that the output is disconnected and does not have a logic significance. The one most commonly used in the design of a bus system is the buffer gate.

The graphic symbol of a three state buffer gate is shown in the figure given below. The control input determines the output.

The construction of a bus system for four registers is shown in the figure in on the next page.

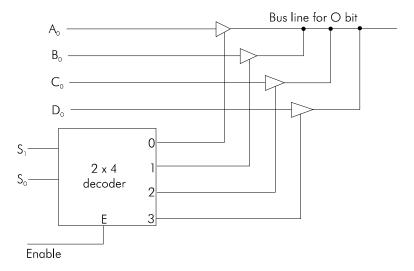

#### Three state table buffers

**Three state table buffers:** A bus system can be constructed with three state gates instead of multiplexers. A three states gate is digital circuit that exhibits three states. Two of the states are signals equivalent to logic 1 and 0 as in a conventional gate. The third state is a high-impedance state. The high-impedance states behaves like an open circuit, which means that the output is disconnected and does not have a logic, such as AND or NAND. However the one most commonly used in the design of a bus system is the buffer gate.

The construction of a bus system with **three state table buffers** is shown in the following figure:

# 2.2 Bus And Memory Transfer

A read operation implies transfer of information to the outside environment from a memory word, whereas storage of information into the memory is defined as write operation. Symbolizing a memory word by the letter M, it is selected by the memory address during the transfer which is a specification for transfer operations. The address is specified by enclosing it in square brackets following the letter M.

For example, the read operation for the transfer of a memory unit M from an address register AR to another data register DR can be illustrated as:

Read:  $DR \leftarrow M[AR]$

The write operation transfer the contents of a data register to a memory word M selected by the address. Assume that the input data are in register R1 and the address in the AR. The write operation can be stated symbolic as follows:

Write:  $M[AR] \leftarrow R1$

This cause a transfer on information from R1 into the memory word M selected by the address in AR.

### 2.3 Micro-Operations

A micro-operation is an elementary operation which is performed on the data stored in registers. We can classify the micro-operations into four categories:

- 1. Register transfer: transfer binary information from one register to another.

- 2. Arithmetic: perform arithmetic operations on numeric data stored in registers.

- 3. Logic: perform bit manipulation operation on non-numeric data stored in registers.

- 4. Shift: perform shift operations on data stored in registers.

#### 2.3.1 Arithmetic Micro-operations

These micro-operations perform some basic arithmetic operations on the numeric data stored in the registers. These basic operations may be addition, subtraction, incrementing a number, decrementing a number and arithmetic shift operation. An 'add' micro-operation can be specified as:

$$R_3 \square R_1 + R_2$$

It implies: add the contents of registers  $R_1$  and  $R_2$  and store the sum in register  $R_3$ . The add operation mentioned above requires three registers along with the addition circuit in the ALU.

Subtraction, is implemented through complement and addition operation as:

$$R_3 \square R_1 - R_2$$

is implemented as  $R_3 \square R_1 + (2$ 's complement of  $R_2$ )  $R_3 \square R_1 + (1$ 's complement of  $R_2 + 1$ )

$R_3 \square R_1 + R_2 + 1$

An increment operation can be symbolized as:

$$R_1 \square R_1 + 1$$

while a decrement operation can be symbolized as:

$$R_1 \square R_1 - 1$$

We can implement increment and decrement operations by using a combinational circuit or binary up/down counters. In most of the computers multiplication and division are implemented using add/subtract and shift micro-operations. If a digital system has implemented division and multiplication by means of combinational circuits then we can call these as the micro-operations for that system. An arithmetic circuit is normally implemented using parallel adder circuits. Each of the multiplexers (MUX) of the given circuit has two select inputs. This 4-bit circuit takes input of two 4-bit data values and a carry-in-bit and outputs the four resultant data bits and a carry-out-bit. With the different input values we can obtain various micro-operations.

| Equivalent micro-operation | Micro-operation name |

|----------------------------|----------------------|

| $R \square R_1 + R_2$      | Add                  |

| $R \square R_1 + R_2 + 1$  | Add with carry       |

| $R \square R_1 + R_2$      | Subtract with borrow |

| $R \square R_1 + 2$ 's     | Subtract             |

| $R\ \square\ R_1$          | Transfer             |

| $R \square R_1 + 1$        | Increment            |

| $R \square R_1 - 1$        | Decrement            |

### 2.3.2 Logic Micro-operations

These operations are performed on the binary data stored in the register. For a logic micro-operation each bit of a register is treated as a separate variable.

For example, if R<sub>1</sub> and R<sub>2</sub> are 8 bits registers and

$R_1$  contains 10010011 and  $R_2$  contains 01010101  $R_1$  AND  $R_2$  00010001

Some of the common logic micro-operations are AND, OR, NOT or complements. Exclusive OR, NOR, NAND.

We can have four possible combinations of input of two variables. These are 00, 01, 10 and 11. Now, for all these 4 input combination we can have  $2^4 = 16$  output combinations of a function. This implies that for two variables we can have 16 logical operations.

# **Logic Micro Operations**

#### SELECTIVE SET

The selective-set operation sets to 1 the bits in register A where there are corresponding 1's in register B. it does not affect bit positions that have 0's in B. the following numerical example clarifies this operation:-

1010 A before 1100 B (logic operand) 1110 A after

#### SELECTIVE COMPLEMENT

The selective-complement operation complements bits in register A where there are corresponding 1's in register B. it does not affect bit positions that have 0's in B. the following numerical example clarifies this operation:-

1010 A before 1100 B (logic operand) 0110 A after

#### SELECTIVE CLEAR

The selective-clear operation clears to 0 the bits in register A only where there are corresponding 1's in register B. For example:-

#### MASK OPERATION

The mask operation is similar to the selective-clear operation except that thebits of A are cleared only where there are corresponding 0's in B. the mask operation is an AND micro operation, for example:-

#### INSERT OPERATION

The insert operation inserts a new value into a group of bits. This is done by first masking the bits and then Oring them with the required value. For example, suppose that an A register contains eight bits, 0110 1010. to replace the four leftmost bits by the value 1001 we first the four unwanted bits:-

the mask operation is an AND microoperation and the insert operation is an OR microoperation.

### **CLEAR OPERATION**

The clear operation compares the words in A and B and produces an all 0's result if the two numbers are equal. This operation is achieved by an exclusive-OR microoperation as has own by the following example:

When A and B are equal, the two corresponding bits are either both 0 or both 1. in either case the exclusive-OR operation produces a 0. the all-0's result is then checked to determine if the tow numbers were equal.

### 2.3.4 Shift Microoperations

Shift microoperation can be used for serial transfer of data. They are used generally with the arithmetic, logic, and other data-processing operations. The contents of a register can be shifted to the left or the right. During a shift-right operation the serial input transfers a bit into the leftmost position. The serial input transfers a bit into the rightmost position during a shift-left operation. There are three types of shifts, logical, circular and arithmetic.

### Logical shift

A logical shift operation transfers 0 through the serial input. We use the symbols *shl* and *shr* for logical shift left and shift right microoperations, e.g.

$R1 \leftarrow shl R1$

$R2 \leftarrow shr R2$

are the two micro operations that specify a 1-bit shift left of the content of register R1 and a 1- bit shift right of the content of register R2.

#### Circular shift

The circular shift is also known as rotate operation. It circulates the bits of the register around the two ends and there is no loss of information. This is accomplished by connecting the serial output of the shift register to its serial input. We use the symbols *cil* and *cir* for the circular shift left and circular shift right. E.g. suppose Q1 register contains 01101101 then after cir operation, it □contains 0110110 and after cil operation it will contain 11011010.

#### Arithmetic Shift

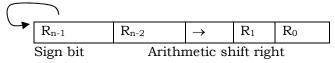

An arithmetic shift micro operation shifts a signed binary number to the left or right. The effect of an arithmetic shift left operation is to multiply the binary number by 2. Similarly an arithmetic shift right divides the number by 2. Because the sign of the number must remain the same arithmetic shift-right must leave the sign bit unchanged, when it is multiplied or divided by 2. The left most bit in a register holds the sign bit, and the remaining bits hold the number. The sign bit is 0 for positive and 1 for negative. Negative numbers are in 2's complement form. Following figure shows a typical register of n bits.

Bit  $R_{n-1}$  in the left most position holds the sign bit.  $R_{n-2}$  is the most significant bit of the number and  $R_0$  is the least significant bit. The arithmetic shift-right leaves the sign bit unchanged and shifts the number (including the sign bits) to the right. Thus  $R_{n-1}$  remains the same,  $R_{n-2}$  receives the bit from  $R_{n-1}$ , and so on for other bits in the register.

#### UNIT 3

#### PROGRAMMING ELEMENTS

| 3.1 | Compu    | uter Arithmetic |                                       |  |  |  |  |

|-----|----------|-----------------|---------------------------------------|--|--|--|--|

| 3.2 | -        |                 | and subtraction with signed-magnitude |  |  |  |  |

| 3.3 |          | ication algo    | 0 0                                   |  |  |  |  |

|     | 3.3.1    | J               | ultiplication algorithm               |  |  |  |  |

|     | 3.3.2    | Array mı        | •                                     |  |  |  |  |

|     | 3.3.3    | · ·             | algorithm                             |  |  |  |  |

|     |          | 3.3.3.1         | S .                                   |  |  |  |  |

|     |          |                 | Divide Overflow                       |  |  |  |  |

| 3.4 | Floating | g-point Arit    | hmetic operations                     |  |  |  |  |

|     | 3.4.1    | Basic co        | nsideration                           |  |  |  |  |

|     |          | 3.4.1.1         | Register configuration                |  |  |  |  |

|     |          | 3.4.1.2         | Addition and subtraction              |  |  |  |  |

|     | 3.4.2    | Decimal         | Arithmetic operations                 |  |  |  |  |

|     |          | 3.4.2.1         | BCD adder                             |  |  |  |  |

|     |          | 3.4.2.2         | BCD subtraction                       |  |  |  |  |

#### 3.1 Computer Arithmetic

Data is manipulated by using the arithmetic instructions in digital computers. Data is manipulated to produce results necessary to give solution for the computation problems. The Addition, subtraction, multiplication and division are the four basic arithmetic operations. If we want then we can derive other operations by using these four operations.

To execute arithmetic operations there is a separate section called arithmetic processing unit in central processing unit. The arithmetic instructions are performed generally on binary or decimal data. Fixed-point numbers are used to represent integers or fractions. We can have signed or unsigned negative numbers. Fixed-point addition is the simplest arithmetic operation.

If we want to solve a problem then we use a sequence of well-defined steps. These steps are collectively called algorithm. To solve various problems we give algorithms.

In order to solve the computational problems, arithmetic instructions are used in digital computers that manipulate data. These instructions perform arithmetic calculations.

And these instructions perform a great activity in processing data in a digital computer. As we already stated that with the four basic arithmetic operations addition, subtraction, multiplication and division, it is possible to derive other arithmetic operations and solve scientific problems by means of numerical analysis methods.

A processor has an arithmetic processor(as a sub part of it) that executes arithmetic operations. The data type, assumed to reside in processor, registers during the execution of an arithmetic instruction. Negative numbers may be in a signed magnitude or signed complement representation. There are three ways of representing negative fixed point - binary numbers signed magnitude, signed 1's complement or signed 2's complement. Most computers use the signed magnitude representation for the mantissa.

#### 3.2 Addition and Subtraction with Signed -Magnitude Data

We designate the magnitude of the two numbers by A and B. Where the signed numbers are added or subtracted, we find that there are eight different conditions to consider, depending on the sign of the numbers and the operation performed. These conditions are listed in the first column of Table 4.1. The other columns in the table show the actual operation to be performed with the magnitude of the numbers. The last column is needed to present a negative zero. In other words, when two equal numbers are subtracted, the result should be +0 not -0.

The algorithms for addition and subtraction are derived from the table and can be stated as follows (the words parentheses should be used for the subtraction algorithm).

Table 4.1: Addition and Subtraction of Signed-Magnitude Numbers

| Operation     | Add Magnitudes | Subtract Magnitudes |            |            |  |  |

|---------------|----------------|---------------------|------------|------------|--|--|

|               |                | When A > B          | When A < B | When A = B |  |  |

| (+A) + (+B)   | +(A + B)       |                     |            |            |  |  |

| (+A) + (- B)  |                | + (A – B)           | - (B - A)  | + (A – B)  |  |  |

| (- A) + (+ B) |                | - (A - B)           | + (B – A)  | + (A – B)  |  |  |

| (-A) + (-B)   | - (A + B)      |                     |            |            |  |  |

| (+ A) – (+ B) |                | + (A + B)           | - (B - B)  | + (A – B)  |  |  |

| (+ A) – (– B) | + (A + B)      |                     |            |            |  |  |

| (-A) - (+B)   | – (A + B)      |                     |            |            |  |  |

| (-A) - (-B)   |                | - (A - B)           | + (B – A)  | + (A – B)  |  |  |

Algorithm

When the signs of A and B are same, add the two magnitudes and attach the sign of result is that of A. When the signs of A and B are not same, compare the magnitudes and subtract the smaller number from the larger. Choose the sign of the result to be the same as A, if A > B or the complement of the sign of A if A < B. If the two magnitudes are equal, subtract B from A and make the sign of the result will be positive.

#### 3.3 Multiplication Algorithms

Multiplication of two fixed-point binary numbers in signed magnitude representation is done with paper and pencil by a process of successive shift and add operations. This process is best illustrated with a numerical example:

This process looks at successive bits of the multiplier, least significant bit first. If the multiplier bit is 1, the multiplicand is copied as it is; otherwise, we copy zeros. Now we shift numbers copied down one position to the left from the previous numbers. Finally, the numbers are added and their sum produces the product.

#### Hardware Implementation for signed-magnitude data

When multiplication is implemented in a digital computer, we change the process slightly. Here, instead of providing registers to store and add simultaneously as many binary numbers as there are bits in the multiplier, it is convenient to provide an adder for the summation of only two binary numbers, and successively accumulate the partial products in a register. Second, instead of shifting the multiplicand to left, the partial product is shifted to the right, which results in leaving the partial product and the multiplicand in the required relative positions. Now, when the corresponding bit of the multiplier is 0, there is no need to add all zeros to the partial product since it will not alter its value.

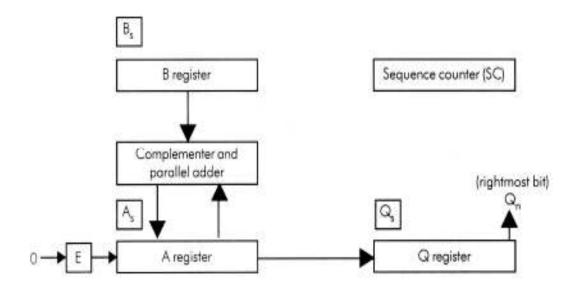

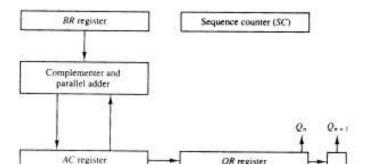

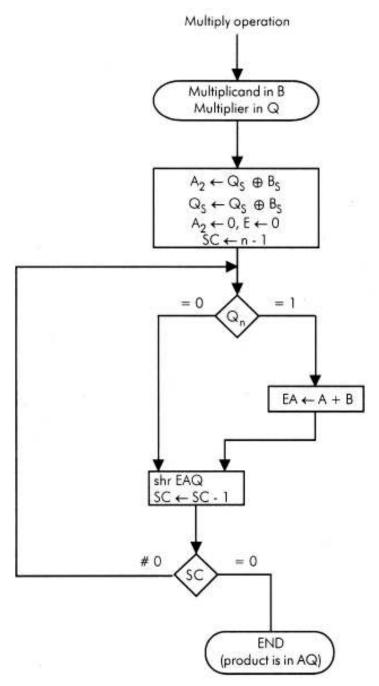

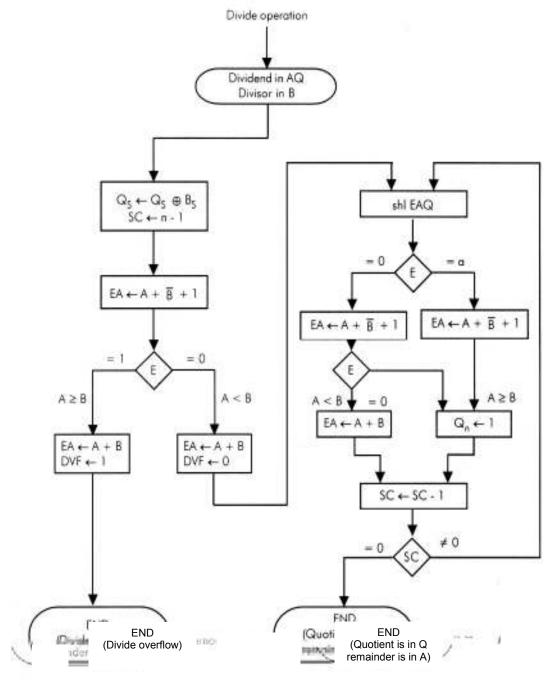

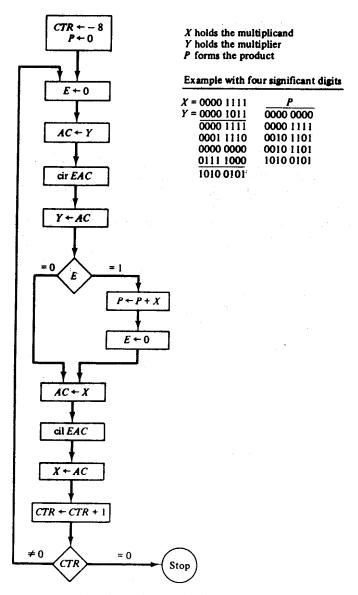

The hardware for multiplication consists of the equipment given in Figure 4.5. The multiplier is stored in the register and its sign in  $Q_s$ . The sequence counter SC is initially set bits in the multiplier. After forming each partial product the counter is decremented. When the content of the counter reaches zero, the product is complete and we stop the process.

Figure 4.5: Hardware for Multiply Operation

# 3.3.1 Booth Multiplication Algorithm

If the numbers are represented in signed 2's complement then we can multiply them by using Booth algorithm. In fact the strings of 0's in the multiplier need no addition but just shifting, and a string of 1's in the multiplier from bit weight  $2^k$  to weight  $2^m$  can be treated as  $2^{k+1}$  -  $2^m$ . For example, the binary number 001111 (+15) has a string of 1's from  $2^3$  to  $2^0$ (k = 3, m = 0).

Table 4.2: Numerical Example for Binary Multiplier

| Multiplicand B = 10111      |   | E |       | A     |       | Q     |     | SC  |

|-----------------------------|---|---|-------|-------|-------|-------|-----|-----|

| Multiplier in Q             | 0 |   | 00000 |       | 10011 |       | 101 |     |

| $Q_n = 1$ ; add B           |   |   | 10111 |       |       |       |     |     |

| First partial product       | 0 |   | 10111 |       |       |       |     |     |

| Shift right EAQ             |   | 0 |       | 01011 |       | 11001 |     | 100 |

| $Q_n = 1$ ; add B           |   |   | 10111 |       |       |       |     |     |

| Second partial product      |   | 1 |       | 00010 |       |       |     |     |

| Shift right EAQ             |   | 1 |       | 00001 |       | 01100 |     | 011 |

| $Q_n = 0$ ; shift right EAQ |   | O |       | 01000 |       | 10110 |     | 010 |

| $Q_n = 0$ ; shift right EAQ |   | O |       | 00100 |       | 01011 |     | 001 |

| Qn = 1; add B               |   |   | 10111 |       |       |       |     |     |

| Fifth partial product       | 0 |   | 11011 |       |       |       |     |     |

| Shift right EAQ             |   | 0 |       | 11011 |       |       |     |     |

Final product in AQ = 0110110101

The number can be represented as  $2^{k+1} - 2^m = 2^{4} - 2^0 = 16 - 1 = 15$ . Therefore, the multiplication M x 14, where M is the multiplicand and 14 the multiplier may be computed as M x  $2^4$  - M x  $2^1$ . That is, the product can be obtained by shifting the binary multiplicand M four times to the left and subtracting M shifted left once.

Booth algorithm needs examination of the multiplier bits and shifting of the partial product. Prior to the shifting, the multiplicand added to the partial product, subtracted from the partial product, or left unchanged by the following rules:

- 1. The multiplicand is subtracted from the partial product when we get the first least significant 1 in a string of 1's in the multiplier.

- 2. The multiplicand is added to the partial product when we get the first Q (provided that there was a previous 1) in a string of 0's in the multiplier.

- 3. The partial product does not change when the multiplier bit is the same as the previous multiplier bit.

The algorithm applies to both positive and negative multipliers in 2's complement representation. This is because a negative multiplier ends with a string of 1's and the last operation will be a subtraction of the appropriate weight. For example, a multiplier equal to -14 is represented in 2's complement as 110010 and is treated as  $-2^4 + 2^2 - 2^1 = -14$ .

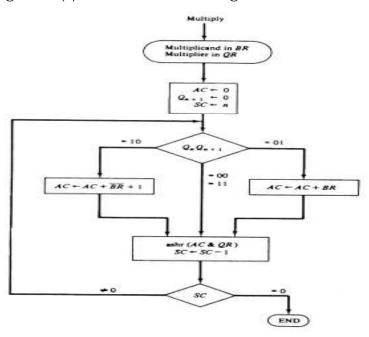

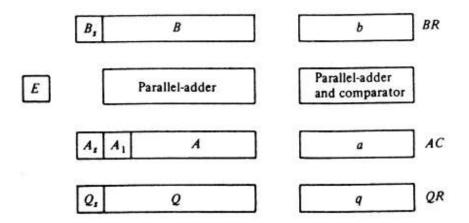

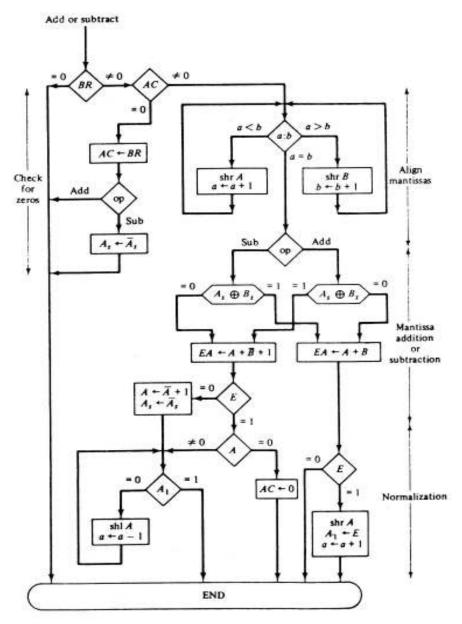

The hardware implementation of Booth algorithm requires the register configuration shown in Figure 4.7(a). Qn represents the least significant bit of the multiplier in register QR. An extra flip-flop  $Q_{n+1}$  is appended to QR to provide a double bit inspection of the multiplier. The flowchart for Booth algorithm is shown in Figure 4.7(b). AC and the appended bit  $Q_{n+1}$  are initially set to 0 and the sequence counter SC is set to a number n equal to the number of bits in the multiplier. The two bits of the multiplier in  $Q_n$  and  $Q_{n+1}$  are inspected. If the two bits are 10, it means that the first 1 in a string of 1's has been encountered. This needs a subtraction of the multiplicand from the partial product in AC. If the two bits are equal to 01. It means that the first 0 in a string of 0's has been encountered. This needs the addition of the multiplicand to the partial product in AC. When the two bits are equal, the partial product does not change. An overflow cannot occur because the addition and subtraction of the multiplicand follow each other. Hence, the two numbers that are added always have opposite sign, a condition that excludes an overflow. Next step is to shift right the partial product and the multiplier (including bit  $Q_{n+1}$ ). This is an arithmetic shift right (ashr) operation which shifts AC and QR to the right and leaves the sign bit in AC same The sequence counter decrements and the computational loop is repeated n times.

Figure 4.7(a): Hardware for Booth Algorithm

Figure 4.7(b)

A numerical example of Booth algorithm is given in Table 4.3 for n=5. It gives the multiplication of (-9) x (-13) = +117. Note that the multiplier in QR is negative and that the multiplicand in BR is also negative. The 10-bit product appears in AC. The final value of  $Q_{n+1}$  is the original sign bit of the multiplier and should not be taken as part of the product.

| Table 4.3: | Example | of Multi | plication | with | Booth A | lgorithm |

|------------|---------|----------|-----------|------|---------|----------|

|            |         |          |           |      |         |          |

|         | BR = 10111     |       |       |   |           |

|---------|----------------|-------|-------|---|-----------|

| Qn Qn+1 | BR + 1 = 01001 | AC    | QR    |   | $Q_{n+1}$ |

| SC      |                |       |       |   |           |

| 1 0     | Initial        | 00000 | 10011 | 0 | 101       |

|         | Subtract BR    | 01001 |       |   |           |

|         |                | 01001 |       |   |           |

|         | ashr           | 00100 | 11001 | 1 | 100       |

| 1 1     | ashr           | 00010 | 01100 | 1 | 011       |

| 0 1     | Add BR         | 101   | 11    |   |           |

|         |                | 11001 |       |   |           |

|         | ashr           | 11100 | 10110 | 0 | 010       |

| 0 0     | ashr           | 11110 | 01011 | 0 | 001       |

| 1 0     | Subtract BR    | 01001 |       |   |           |

|         |                | 00111 |       |   |           |

| ashr | 0011 | 10101 | 1 | 000 |

|------|------|-------|---|-----|

|------|------|-------|---|-----|

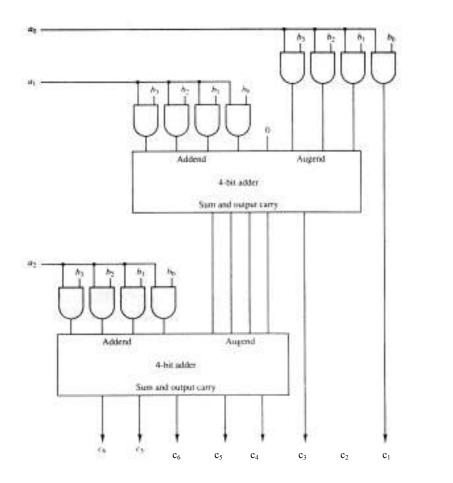

### 3.3.2 Array Multiplier

To check the bits of the multiplier one at a time and forming partial products is a sequential operation requiring a sequence of add and shift micro-operations. The multiplication of two binary numbers can be done with one micro-operation by using combinational circuit that forms the product bits all at once.

This is a fast way since all it takes is the time for the signals to propagate through the gates that form the multiplication array. However, an array multiplier requires a large number of gates, and so it is not an economical unit for the development of ICs.

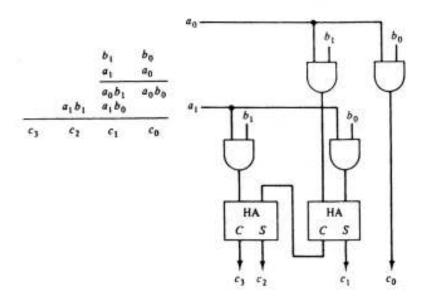

Now we see how an array multiplier is implemented with a combinational circuit. Consider the multiplication of two 2-bit numbers as shown in Fig. 4.8. The multiplicand bits are  $b_1$  and  $b_0$ , the multiplier bits are  $a_1$  and  $a_0$ , and the product is  $c_3$   $c_2$   $c_1$   $c_0$ . The first partial product is obtained by multiplying  $a_0$  by  $b_1b_0$ . The multiplication of two bits gives a 1 if both bits are 1; otherwise, it produces a 0. This is identical to an AND operation and can we implement it with an AND gate. As shown in the diagram, the first partial product is formed by means of two AND gates. The second partial product is formed by multiplying  $a_1$  by  $b_1b_0$  and is shifted one position to the left. The two partial products are added with two half-adder (HA) circuits. Usually, there are more bits in the partial products and it will be necessary to use full-adders to produce the sum. Note that the least significant bit of the product does not have to go through an adder since it is formed by the output of the first AND gate.

A combinational circuit binary multiplier with more bits can be constructed in a similar fashion. A bit of the multiplier is ANDed with each bit of the multiplicand in as many levels as there are bits in the multiplier. The binary output in each level AND gates is added in parallel with the partial product of the previous level to form a new partial product. The last level produces the product. For j multiplier bits and k multiplicand bits we need j \* k AND gates and (j - 1) k-bit adders to produce a product of j + k bits.

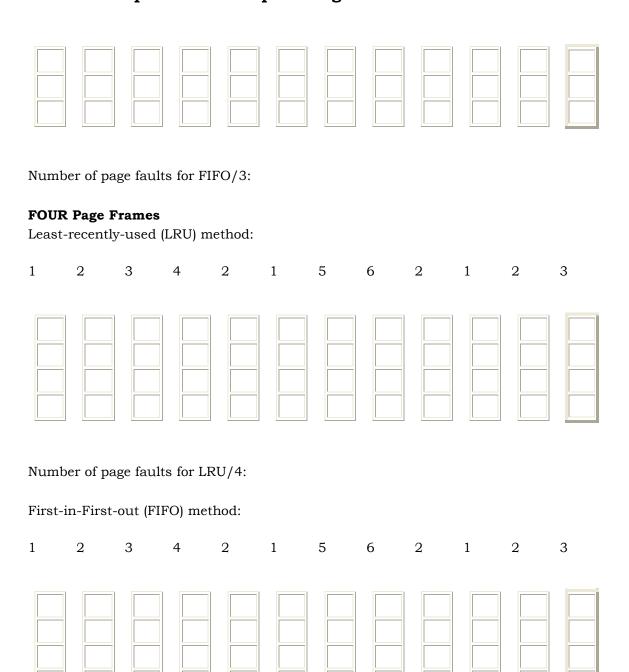

Figure 4.8: 2-bit by 2-bit array multiplier