## NAVSEA SE 003-AA-TRN-010

ELECTROSTATIC DISCHARGE

AD A U SG 1 U

# TRAINING MANUAL

#### FOREWORD

MANY ELECTRONIC PARTS SUCH AS MICROCIRCUITS, DISCRETE SEMICONDUCTORS, FILM RESISTORS AND CRYSTALS ARE SUSCEPTIBLE TO DAMAGE FROM ELECTROSTATIC DIS-CHARGE (ESD). COMPREHENSIVE ESD CONTROL PROGRAMS ARE REQUIRED TO PROTECT THESE PARTS DURING MANUFACTURE, ASSEMBLY, TEST, REPAIR/REWORK, MAINTENANCE, AND OTHER HANDLING OPERATIONS. SUCH CONTROL PROGRAMS MUST BE IMPLEMENTED THROUGHOUT THE LIFE CYCLE OF THESE ELECTRONIC PARTS. THE INTENT OF THIS TRAINING MANUAL IS TO COMPLEMENT AN ESD AWARENESS TRAINING COURSE WHICH IS A KEY PART OF ANY EFFEC-TIVE ESD CONTROL PROGRAM.

THIS MANUAL COVERS TOPICS SUCH AS: PRINCIPLES OF STATIC ELECTRICITY, CHARGING AND DISCHARGING, PRIME STATIC GENERATORS, STATIC ELECTRIFICATION OF ELECTRICAL AND ELECTRONIC PARTS, ELEMENTS OF AN ESD CONTROL PROGRAM, ESD PROTEC-TIVE MATERIALS, ESD PROTECTIVE EQUIPMENT, PACKAGING AND MARKING OF ESDS ITEMS, ESD IN DESIGN, ESD HANDLING PRECAUTIONS AND PROCEDURES, AND MONITORING OF ESD CONTROL PROGRAMS......

REQUESTS FOR COPTES OF THIS MANUAL EROM U.S. GOVERNMENT ACTIVITIES SHOULD

COMMANDING OFFICER NAVAE PUBLICATIONS AND FORMS CENTER 5801 TABOR AVENUE PHILADELPHIA, PENNSYLVANIA 19120

REQUESTS FROM INDUSTRY SHOULD BE FORWARDED TO THE SAME ADDRESS VIA THE LOCAL U.S. GOVERNMENT REPRESENTATIVE (E.G., DCASA) OR MAY BE PURCHASED DIRECTLY FROM THE SAME ADDRESS, ATTN: CODE FOIG.

NAVAL SEA SYSTEMS COMMAND DEPARTMENT OF THE NAVY CODE 6151 WASHINGTON, D.C. 20362 SEPTEMBER 1980

### TABLE OF CONTENTS

|      |            |                                                                     | Page |

|------|------------|---------------------------------------------------------------------|------|

| Ι.   | INT        | RODUCTION                                                           | 1    |

|      | Α.         | BACKGROUND                                                          | 1    |

|      | Β.         | ESDS PART FAILURE                                                   | ۱    |

|      | c.         | TRANSIENT UPSET FAILURE                                             | 2    |

|      | D.         | TRANSMITTED FAILURES                                                | 3    |

|      | E.         | THE ESD PROBLEM                                                     | 3    |

|      | F.         | ESTABLISHED ESD CONTROL PROGRAM REQUIREMENTS                        | 3    |

| II.  | PRI        | NCIPLES OF STATIC ELECTRICITY                                       | 10   |

|      | A.         | BACKGROUND                                                          | 10   |

|      | Β.         | TRIBOELECTRIC EFFECT                                                | 10   |

|      | C.         | MATHEMATICAL FORMULATION OF ELECTROSTATIC FIELD<br>ANALYSIS         | 13   |

| III. | <u>CHA</u> | RGING AND DISCHARGING                                               | 30   |

|      | Α.         | INTRODUCTION                                                        | 30   |

|      | Β.         | PARAMETERS INFLUENCING THE MAGNITUDE OF STATIC CHARGE<br>GENERATION | 42   |

|      | C.         | MATHEMATICAL EXPRESSIONS FOR ELECTROSTATIC DISCHARGE                | 43   |

| IV.  | PRI        | ME STATIC GENERATORS                                                | 51   |

|      | Α.         | TYPICAL CHARGE GENERATORS                                           | 51   |

|      | Β.         | MANUFACTURING PROCESSES GENERATING STATIC ELECTRICITY               | 51   |

| ۷.   | STA        | TIC ELECTRIFICATION OF ELECTRICAL AND ELECTRONIC PARTS              | 55   |

| ·    | Α.         | GENERAL                                                             | 57   |

|      | Β.         | FAILURE MECHANISMS                                                  | 57   |

|      | C.         | LATENT/DEGRADATION DAMAGE FAILURE MECHANISMS                        | 61   |

|      | D.         | EXAMPLES OF ESD FAILURES                                            | 61   |

i.

· · ·

1

### TABLE OF CONTENTS (Cont'd)

|       |            |                                             | Page |

|-------|------------|---------------------------------------------|------|

| VI.   | ESD        | CONTROL PROGRAM                             | 71   |

|       | Α.         | GENERAL                                     | 71   |

|       | Β.         | PROGRAM REQUIREMENTS                        | 71   |

|       | C.         | TAILORING                                   | 81   |

| VII.  | ESD        | PROTECTIVE MATERIALS                        | 84   |

|       | Α.         | GENERAL                                     | 84   |

|       | Β.         | ESD PROTECTIVE MATERIALS                    | 84   |

|       | C.         | ELEMENTS OF AN ESD PROTECTED AREA           | 100  |

| VIII. | <u>ESD</u> | PROTECTIVE EQUIPMENT                        | 121  |

|       | Α.         | GENERAL                                     | 121  |

|       | Β.         | IONIZERS                                    | 121  |

|       | C.         | ESD PROTECTIVE TOOLS                        | 123  |

|       | D.         | ELECTROSTATIC DETECTORS AND ALARMS          | 124  |

|       | Ε.         | PORTABLE ESD WORK STATION KITS              | 126  |

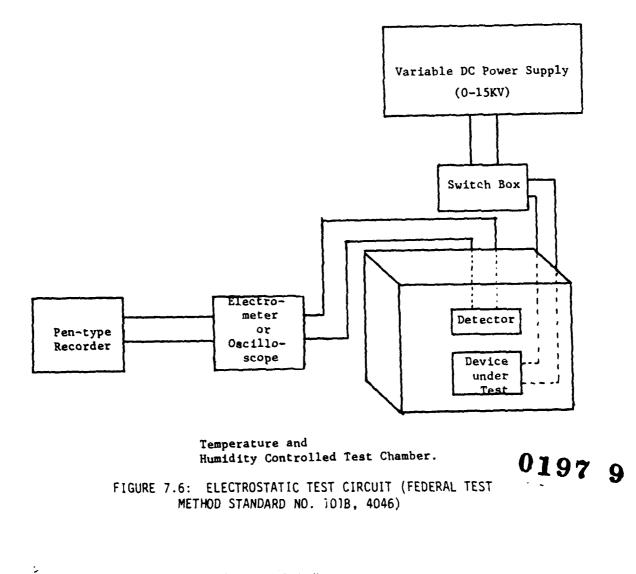

|       | F.         | SPECIAL ESD TEST EQUIPMENT                  | 126  |

| IX.   | PAC        | KAGING AND MARKING OF ESDS ITEMS            | 128  |

|       | Α.         | GENERAL                                     | 128  |

|       | Β.         | PROTECTION AGAINST TRIBOELECTRIC GENERATION | 129  |

|       | с.         | PROTECTION AGAINST DIRECT DISCHARGE         | 129  |

|       | D.         | PROTECTION AGAINST ELECTROSTATIC FIELDS     | 129  |

|       | E.         | SHUNTING DEVICES                            | 130  |

|       | F.         | NAVY ESD PACKING REQUIREMENTS               | 130  |

|       | G.         | REPACKAGING FOR DISTRIBUTION                | 131  |

ii.

¥.

iii.

### TABLE OF CONTENTS (Cont'J)

÷P.

•

4

×

|       |      |                                                              | Page |

|-------|------|--------------------------------------------------------------|------|

| х.    | ESD  | IN DESIGN                                                    | 132  |

|       | Α.   | GENERAL                                                      | 132  |

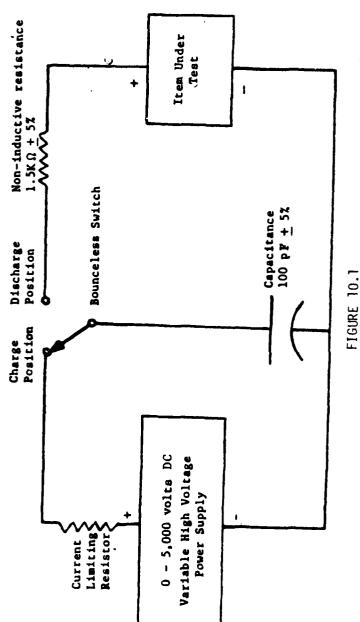

|       | Β.   | HUMAN MODEL EQUIVALENT CIRCUIT                               | 133  |

|       | C.   | ELECTROSTATIC DISCHARGE TESTING                              | 136  |

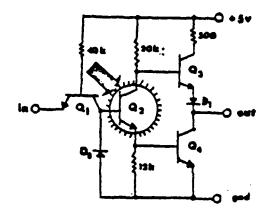

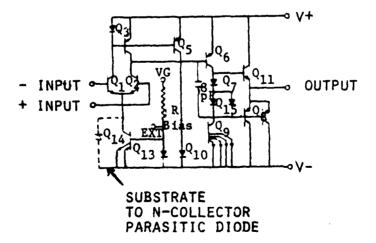

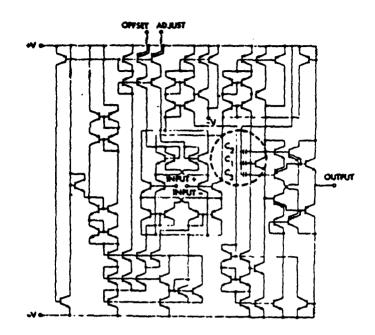

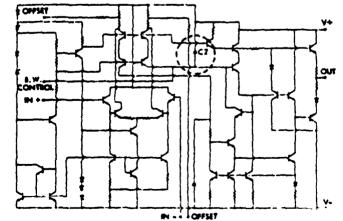

|       | D.   | EXAMPLES OF SOME TYPICAL DAMAGE PATH IN MICROCIRCUITS        | 148  |

|       | Ε.   | COMMENTS ON EMP TESTING AND CONVERSION OF EMP DATA<br>TO ESD | 150  |

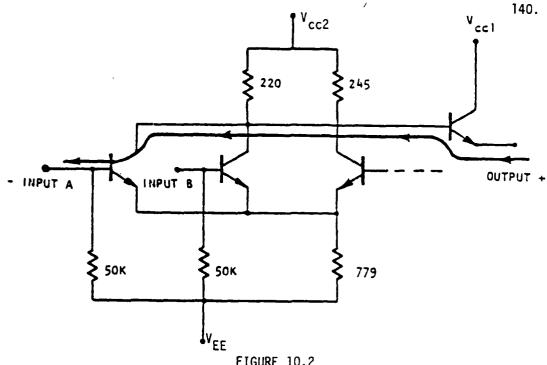

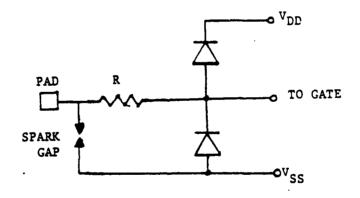

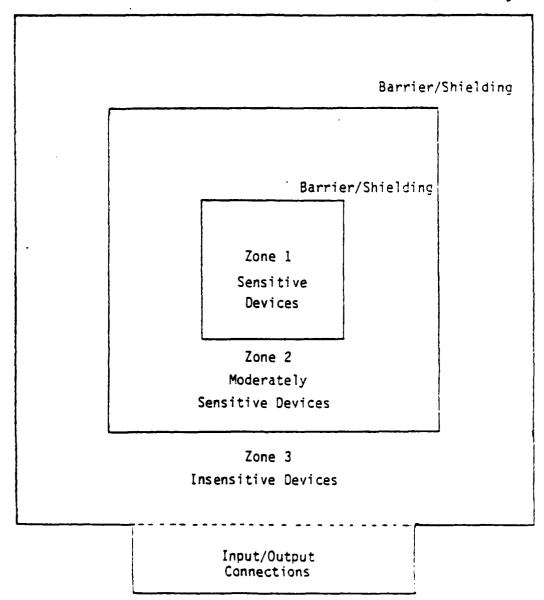

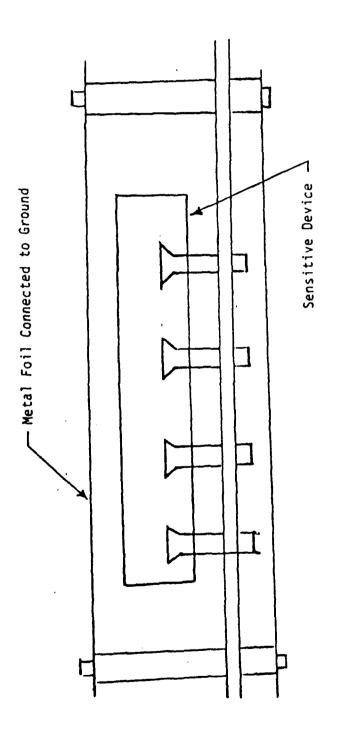

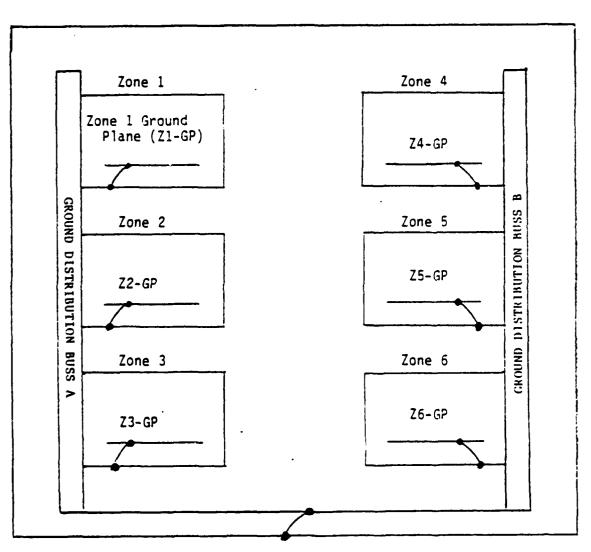

|       | F.   | ESD PROTECTIVE CIRCUITRY                                     | 159  |

| XI.   |      | HANDLING PRECAUTIONS AND PROCEDURES                          |      |

| XII.  | MON  | ITORING OF ESD CONTROL PROGRAMS                              | 190  |

|       | Α.   | GENERAL                                                      | 190  |

|       | в.   | ESD PROGRAM MONITORING AND AUDITS                            | 190  |

|       | c.   | FORMAL REVIEWS                                               | 201  |

| XIII. | REFI | ERENCES                                                      | 204  |

#### ELECTROSTATIC DISCHARGE (ESD) CONTROL PROGRAM TRAINING COURSE

#### I. INTRODUCTION

#### A. BACKGROUND

STATIC ELECTRICITY IS FAMILIAR TO US ALL AS LIGHTNING, STATIC CLING OF CLOTHING AND SPARKING WHEN TOUCHING A DOOR KNOB OR OTHER METALLIC OBJECTS IN COOL, DRY WEATHER.

ORDINARY VINYL CLEAN ROOM DRAPERIES CAUSED CONSIDERABLE INTERFERENCE WITH THE MARINER SPACECRAFT RECEIVERS AT JET PROPULSION LAB-ORATORIES IN PASADENA, WHENEVER A PASSING TECHNICIAN BRUSHED HIS BUNNY-SUIT AGAINST THE CLEAR VINYL CURTAIN WHICH FORMED THE WALLS OF THE PORTABLE DOWN-FLOW ROOM IN WHICH THE MARINER WAS ASSEMBLED.

STATIC ELECTRICITY AND THE DIRT IT ATTRACTS CAN CAUSE DATA LOSS IN A COMPUTER. BOTH ARE RESPONSIBLE FOR MAJOR PROBLEMS SUCH AS PRINTER MALFUNCTION, PAPER JAMS, DESTRUCTION OF SENSITIVE LOGIC CIRCUITS AND THE ATTRACTION OF CONTAMINANTS TO READ/WRITE HEADS AND MAGNETIC RE-CORDING SURFACES. ADDITIONALLY, STATIC CAN PRODUCE NOISE TRANSIENTS IN SYSTEM INTERFACE LINES CAUSING EQUIPMENT MALFUNCTION OR DEGRADATION OF SYSTEM PERFORMANCE. FOR EXAMPLE, IN 1974, STATIC LEVELS AS HIGH AS 17,000 VOLTS WERE DISCHARGED IN THE COMPUTER ROOM AT NEW YORK TELEPHONE AT VAR-IOUS TIMES OF THE DAY, CAUSING THE IBM 1130 COMPUTING SYSTEM TO BE OUT OF PARITY. THIS OCCURRED ON THE AVERAGE OF FIVE TIMES DAILY RESULTING IN AN ENORMOUS NUMBER OF BILLING ERRORS.

B. ESDS PART FAILURE

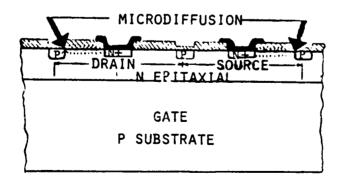

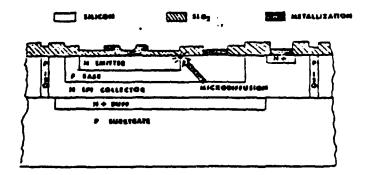

STATIC VOLTAGES UP TO AND SOMETIMES EXCEEDING 15,000 VOLTS CAN BE GENERATED BY SIMPLE MOTIONS SUCH AS GETTING UP FROM A CHAIR, WALKING ACROSS A ROOM, ROCKING IN A CHAIR, RUBBING OF CLOTHING AND THOUS-ANDS OF OTHER NORMAL, EVERYDAY PERSONNEL MOVEMENTS. SUCH STATIC VOLTAGES CAN DAMAGE ELECTRICAL AND ELECTRONIC COMPONENTS AND DEVICES (PARTS) SUCH AS INTEGRATED CIRCUITS (ICs), DISCRETE SEMICJNDUCTORS, THICK AND THIN FILM DEVICES AND CRYSTALS. THE STATIC DANGER TO SOLID STATE SEMICONDUCTORS IS DUE TO THE EXTENSIVE USE OF THEN OXIDE LAYERS (E.G., MOS DEVICES) AND THE MICROMINIATURIZATION OF ACTIVE JUNCTIONS WHICH ARE SEVERELY LIMITED IN THE POWER THEY CAN HANDLE. FILM RESISTORS ARE DAMAGED BY METALLIZATION MELT; CRYSTALS BY MECHANICAL OVERSTRESS IN REACTION TO HIGH ESD VOLTAGE.

THE ESD SENSITIVITY OF PARTS IS BECOMING MORE EVIDENT DURING PRODUCTION, USE, TESTING, AND FAILURE ANALYSIS. THE CONSTRUCTION AND DESIGN FEATURES OF CURRENT MICROTECHNOLOGY HAS RESULTED IN PARTS WHICH CAN BE DAMAGED BY ESD VOLTAGES AS LOW AS 20 VOLTS. THE TREND IN THIS TECH-NOLOGY IS TOWARDS GREATER COMPLEXITY AND INCREASED PACKAGING DENSITY; HENCE SMALLER ACTIVE ELEMENTS AND THINNER DIELECTRICS BETWEEN ACTIVE ELEMENTS. THIS RESULTS IN PARTS THAT ARE BECOMING MORE AND MORE SENSITIVE TO ESD.

WHILE CATASTROPHIC FAILURES OF ICS ARE A MAJOR PROBLEM, THEY BECOME OBVIOUS RATHER QUICKLY TO THE EQUIPMENT USER. SUBASSEMBLIES, ASSEMBLIES AND EQUIPMENT CONTAINING THESE ESDS PARTS ARE NORMALLY AS SENSI-TIVE AND IN SOME CASES MORE SENSITIVE THAN THE PARTS THEMSELVES. FOR EX-AMPLE, PRINTED CIRCUIT BOARD RUNS CAN ACT AS ANTENNAS GATHERING GREATER STATIC VOLTAGES ACROSS SENSITIVE PART LEADS THAN SUBJECTING THESE INDIVIDUAL PARTS TO ELECTROSTATIC FIELDS.

C. TRANSIENT UPSET FAILURE

A MORE SUBTLE PROBLEM, HOWEVER, IS THAT OF ELECTROSTATIC DISCHARGES INDUCING NOISE INTO ESDS PARTS OR CIRCUINRY. UNLIKE CATASTROPHIC

FAILURES, THESE SUBTLE FAULTS CAN GO UNDETECTED FOR A CONSIDERABLE PERIOD OF TIME AND, ONCE DETECTED, CAN BE VERY DIFFICULT TO DIAGNOSE. DIGITAL CIRCUITS ARE MUCH MORE SUSCEPTIBLE THAN LINEAR CIRCUITS TO THIS TYPE OF PROBLEM BECAUSE THEIR OPERATION DEPENDS UPON THE RECOGNITION AND PRO-CESSING OF PULSES. THE PRESENCE OF A STATIC DISCHARGE PULSE-LIKE NOISE SPIKE CAN UPSET THE IC'S LOGIC PROCESS. FOR EXAMPLE, IN AMERICAN TELE-COMMUNICATION COMPANY'S AUTOMATIC DIALING EQUIPMENT, STATIC DISCHARGES CAUSED ERASURE OF THE TELEPHONE NUMBERS STORED IN MEMORY.

#### D. TRANSMITTED FAILURES

SIMILARLY, STATIC DISCHARGES CAUSED COUNTING FAULTS (AND EVENTUAL FAILURE) IN INTERNATIONAL COMPUTING SCALE COMPANY'S COUNTING SCALES. THE PROBLEM WAS RELATED TO THE ELECTROSTATIC CHARGE TRANSMITTED THROUGH THE FRONT-PANEL LEDS TO ITS ASSOCIATED PC BOARD BEHIND THE PANEL CAUSING FAILURE OF SOME BOARD-MOUNTED ICS. MANY PARTS ALTHOUGH NOT SENSI-TIVE THEMSELVES TO ESD, CAN CONDUCT ESD PULSES THROUGH CIRCUITRY TO ESDS PARTS AND CAUSE THEIR FAILURE.

#### E. THE ESD PROBLEM

TODAY, ESD CONTROLS ARE NOT WIDELY IMPLEMENTED FOR ELECTRONICS. COMPREHENSIVE ESD CONTROL PROGRAM REQUIREMENTS GENERALLY HAVE NOT BEEN CONTRACTUALLY SPECIFIED TO DATE AND RELATIVELY FEW CONTRACTORS HAVE TAKEN THE INITIATIVE TO IMPLEMENT ESD CONTROL PROGRAMS INTERNALLY AND IMPOSE EFFECTIVE ESD CONTROL REQUIREMENTS ON THEIR SUBCONTRACTORS. WITH THE ADVENT OF DOD-STD-1686 (REFERENCE 1), THIS WILL CHANGE IN THE NEAR FUTURE.

PERHAPS ONE OF THE PRIME CAUSES FOR THE LACK OF IMPLE-MENTATION OF ESDS CONTROLS IS THE LACK OF ESD AWARENESS FOR ALL

FUNCTIONS FOR WHICH ESD CONTROLS ARE NECESSARY, SUCH AS: PROGRAM MANAGE-MENT, PROCUREMENT, ENGINEERING, MANUFACTURING, PACKAGING, STORAGE, FIELD MAINTENANCE AND QUALITY CONTROL. FEW CONTRACTORS HAVE ESTABLISHED AND IMPLEMENTED INTERNAL ESD TRAINING PROGRAMS FOR THESE FUNCTIONS. ADDI-TIONALLY, THE HARDWARE, PACKAGING, DRAWINGS OR TECHNICAL MANUALS ARE GENERALLY NOT MARKED SO THAT THE USERS ARE AWARE THAT THE HARDWARE THEY PROCURE, OPERATE AND MAINTAIN IN THE FIELD CONTAIN ESDS ITEMS. LACK OF ESD TRAINING OR AWARENESS IS NOT LIMITED TO INDUSTRY. MILITARY PERSONNEL USING ESDS EQUIPMENT ALSO GENERALLY LACK ESD TRAINING, AND ESD AWARENESS IS SELDOM INCLUDED IN EQUIPMENT TRAINING PROGRAMS CONDUCTED FOR MILITARY PERSONNEL BY CONTRACTORS.

A PRIMARY REASON FOR THE LACK OF ESD AWARENESS TO DATE IS THE LACK OF BASIC TECHNICAL DATA RELATING TO ESD. NUMEROUS PAPERS HAVE BEEN PUBLISHED IN VARIOUS MAGAZINES, PERIODICALS AND SYMPOSIUM PROCEEDINGS. HOWEVER, IT IS DIFFICULT FOR PEOPLE INTERESTED IN ESD TO GATHER ALL THIS INFORMATION AND TO OBTAIN INFORMATION ON ALL ASPECTS OF AN ESD CONTROL PRO-GRAM FROM RANDOM ARTICLES. ADDITIONALLY, THERE ARE NUMEROUS AREAS RELATING TO ESD FOR WHICH FEW ARTICLES HAVE BEEN PUBLISHED AND FOR WHICH CONSIDERABLE RESEARCH IS REQUIRED.

ESD IS NOT TAUGHT IN COLLEGE COURSES AND FEW BOOKS HAVE BEEN WRITTEN ON THE SUBJECT. SYMPOSIUMS LIKE THE ELECTRICAL OVERSTRESS/ELECTRO-STATIC DISCHARGE (EOS/ESD) ARE METHODS FOR DISSEMINATING INFORMATION ON ESD. HOWEVER, SUCH SYMPOSIUMS ARE NOT ATTENDED BY ENOUGH PEOPLE, ARE TOO IN-FREQUENT, TOO SHORT, AND OFTEN UNTIMELY, TO PROVIDE ANSWERS TO THE EVERYDAY ESD PROBLEMS PEOPLE ENCOUNTER IN THE FIELD OF ELECTRONICS. A FORMAL CENTRALIZED ESD INFORMATION EXCHANGE IS REQUIRED TO COLLECT ESD DATA, PERFORM ENGINEERING ANALYSIS, AND DISSEMINATE THE LATEST INFORMATION ON

ESD; THE LATEST LISTING OF ESDS PARTS AND THEIR SENSITIVITIES THAT ARE CONSTANTLY CHANGING WITH THE STATE-OF-THE-ART ADVANCEMENTS IN SOLID STATE TECHNOLOGY; AND THE NEW PRODUCTS AND MATERIALS BEING DEVELOPED THAT CAN SOLVE SOME OF THE MORE DIFFICULT PROBLEMS RELATING TO ESD. SUFFICIENT INFORMATION IS SELDOM PUBLISHED ON MATERIALS MARKETED FOR ESD CONTROLS. CHEMICAL AND PHYSICAL CHARACTERISTICS, USEFUL LIFE, STORAGE LIFE, AND KEY ELECTROSTATIC CHARACTERISTICS SUCH AS PROTECTION AGAINST TRIBOELECTRIC GENERATION, ELECTROSTATIC SHIELDING ATTENUATION AND PROTECTION AFFORDED FROM CONTACT WITH CHARGED PERSONS OR OBJECTS ARE SELDOM PROVIDED BY THE MATERIAL MANUFACTUREFS. THIS MAY IN PART BE DUE TO THE LACK OF FORMAL TEST MATERIALS AND STANDARD SPECIFICATION REQUIREMENTS FOR SUCH MATERIALS.

ANOTHER BASIC PROBLEM IS THAT FAILURES ARE OFTEN NOT RECOGNIZED AS RELATED TO ESD. FAILURES CAUSED BY ESD ARE OFTEN ANALYZED AS ELECTRICAL OVERSTRESS FAILURES AND BLAMED ON POWER LINE TRANSIENTS OR TECHNICIANS IMPROPERLY HOOKING UP, PROBING OR TESTING AN ASSEMBLY WITH TOO HIGH A VOLT-AGE. OTHER FAILURES CAUSED BY ESD ARE OFTEN CATEGORIZED AS RANDOM, UNKNOWN, INFANT MORTALITY, OR MANUFACTURING DEFECT DUE TO THE LACK OR DEPTH OF FAILURE ANALYSIS PERFORMED. A MAJOR REASON FOR THE ABOVE IS THAT FEW FAILURE ANALYSIS LABORATORIES ARE EQUIPPED WITH SCANNING ELECTRON MICRO-SCOPES OR OTHER EQUIPMENT AND TECHNOLOGY REQUIRED TO TRACE FAILURES TO ESD. ALSO, ESD CAUSED FAILURES CAN OFTEN BE OVERLOOKED IF THE FAILURE ANALYSIS TECHNICIANS ARE NOT PROPERLY TRAINED. MANY MANUFACTURERS OF ELECTRONIC EQUIPMENT CONTAINING ESDS PARTS ACCEPT A PERCENTAGE OF PART FAILURES AS NORMAL PRODUCTION FALLOUT WHEN MANY MAY BE CAUSED BY ESD. THE USER IN THE FIELD OFTEN ACCEPTS THE HIGHER OPERATIONAL FAILURE RATES OF EQUIPMENT CONTAINING ESDS ITEMS AS NORMAL AND INSTEAD OF INVESTIGATING THE CAUSE OF THE HIGH NUMBER OF FAILURES SIMPLY PROCURES GREATER QUANTITIES OF SPARES.

LACK OF ESD AWARENESS OFTEN RESULTS IN PERSONNEL LIMITING ESD HANDLING PRECAUTIONS TO THE MOST NOTORIOUS ESDS PARTS (E.G., METAL OXIDE SEMI-CONDUCTORS (MOSs)) WITHOUT KNOWING THAT FAILURES OF NUMEROUS OTHER PARTS ARE BEING CAUSED BY ESD. THE LACK OF ESD AWARENESS ALSO CONTRIBUTES TO THE FALSE SENSE OF SECURITY THAT AN ESDS PART CONTAINING BUIT-IN PROTEC-TIVE CIRCUITRY IS COMPLETELY PROTECTED FROM ESD, NOT KNOWING THAT MOST PROTECTIVE CIRCUITRY NORMALLY DECREASES SENSITIVITY BY ONLY SEVERAL HUNDRED VOLTS. ESD CAN RESULT IN LATENT DEFECTS WHERE THE ITEM WILL OPERATE WITHIN SPECIFICATION LIMITS DURING TEST, BUT WILL FAIL AFTER BEING DELIVERED TO THE USER. IN ALL OF THE ABOVE INSTANCES, ESD AS A CAUSE OF FAILURE IS NOT ALWAYS RECOGNIZED AND HENCE ESD CONTROL MEASURES ARE NOT IMPLEMENTED.

RECOGNIZING THESE PROBLEMS, THE NAVAL SEA SYSTEMS COMMAND HAS DEVELOPED DOD-STD-1686 FOR DEFINING ESD CONTROL PROGRAM REQUIREMENTS AND DOD-HDBK-263 TO PROVIDE GUIDELINES FOR IMPLEMENTING THESE REQUIREMENTS.

#### F. ESTABLISHED ESD CONTROL PROGRAM REQUIREMENTS

ESD CONTROL PROGRAM REQUIREMENTS ARE NOT COMPLETELY NEW. MANY ESTABLISHED MILITARY SPECIFICATIONS AND STANDARDS COMMONLY IMPOSED ON EQUIPMENT MANUFACTURERS REQUIRE CONTROLS FOR PROTECTION OF ESDS ITEMS. FOR EXAMPLE, MIL-Q-9858 "QUALITY PROGRAM REQUIREMENTS" (REFERENCE 2) REQUIRES THAT WORK INSTRUCTIONS BE DEVELOPED FOR ALL WORK AFFECTING THE QUALITY OF EQUIPMENT INCLUDING HANDLING, ASSEMBLING, FABRICATING, PROCESSING, INSPECTION, TESTING, MODIFICATIONS, ETC., AND THAT HANDLING, STORAGE, PRESERVATION, PACKAGING AND SHIPPING WORK AND INSPECTION INSTRUC-TIONS PROTECT THE QUALITY OF PRODUCTS AND PREVENT LOSS, DETERIORATION OR DEGRADATION OF PRODUCTS.

MIL-STD-785, "RELIABILITY PROGRAM FOR SYSTEMS AND EQUIPMENT DEVELOPMENT AND PRODUCTION" (REFERENCE 3) REQUIRES THE EFFECTS OF PACK-AGING, TRANSPORTATION, HANDLING AND MAINTENANCE ON THE RELIABILITY OF THE END PRODUCT BE DETERMINED AND THAT CRITICAL CHARACTERISTICS OF ITEMS THAT DETERIORATE WITH ENVIRONMENTAL CONDITIONS BE IDENTIFIED.

PERHAPS THE STRONGEST ESTABLISHED REQUIREMENTS FOR ESD CON-TROLS ARE FOUND IN MIL-STD-882, "SYSTEM SAFETY PROGRAM REQUIREMENTS" (REFERENCE 4) WHICH IMCLUDE: IDENTIFICATION OF CRITICAL PATHS, ASSEMBLIES, PRODUCTION TECHNIQUES, ASSEMBLY PROCEDURES, FACILITIES, TESTING AND IN-SPECTION REQUIREMENTS WHICH MAY AFFECT SAFETY (INCLUDING MATERIAL SAFETY); ENSURE SAFETY WITHIN THE PRODUCTION PROCESS; PROVIDE WARNINGS AND CAUTIONS IN TECHNICAL MANUALS AND PRODUCTION PROCESSES, OPERATION, STORAGE, PACK-AGING AND HANDLING; USE DESIGN TECHNIQUES AND SAFETY DEVICES TO MINIMIZE HAZARDS TO SAFETY (INCLUDING MATERIAL SAFETY); ELIMINATION OR CONTROL OF HAZARDS RESULTING FROM ENVIRONMENTAL CONDITIONS INCLUDING SPECIFICALLY: "ELECTROSTATIC DISCHARGE"; INCLUSION OF SAFETY (INCLUDING MATERIAL SAFETY) PROCEDURES IN INSTRUCTORS' LESSON PLANS AND STUDENT EXAMINATIONS FOR THE TRAINING OF 'ENGINEERS, TECHNICIANS, OPERATING AND MAINTENANCE PERSONNEL AND REQUIREMENTS FOR AN AUDIT PROGRAM TO ENSURE THAT THE OBJECTIVES AND RE-QUIREMENTS OF THE SAFETY PROGRAM ARE BEING ACCOMPLISHED.

THE ABOVE IS A SMALL SAMPLING OF ESTABLISHED MILITARY DOCUMENTS WHICH REQUIRE SOME OF THE BASIC ELEMENTS OF AN ESD CONTROL PROGRAM THAT ARE COMMONLY IMPOSED UPON DOD CONTRACTORS. A MORE COMPLETE LISTING OF THESE DOCUMENTS AND THEIR REQUIREMENTS PERTAINING TO AN ESD CONTROL PROGRAM ARE SUMMARIZED IN NAVSEA S6000-AB-GTP-010, "MILITARY SPECIFICATIONS, STAND-ARDS AND CONTRACT CLAUSES SPECIFYING CONTROLS FOR PROTECTION AGAINST ELECTROSTATIC DISCHARGE" (REFERENCE 5).

#### F. IMPACT OF NOT IMPLEMENTING ESD CONTROLS

THE IMPACT OF NOT IMPLEMENTING EFFECTIVE AND COMPREHENSIVE ESD CONTROLS CAN BE COSTLY TO BOTH THE MANUFACTURER AND THE USER.

ESD FAILURES AT THE MANUFACTURER'S PLANT RESULT IN REPLACE-MENT COSTS FOR FAILED PARTS AND REWORK AND REPAIR COSTS IF FAILURES OCCUR AT THE ASSEMBLY LEVEL OR AFTER THE EQUIPMENT ASSEMBLY HAS BEEN COMPLETED. THE HIGHER THE ASSEMBLY LEVEL AT WHICH THE FAILURE OCCURS THE GREATER ARE THE COSTS.

UNSCHEDULED MAINTENANCE RESULTING FROM ESD RELATED FAILURES COULD IMPACT DELIVERY SCHEDULES. THE EQUIPMENT DOWNTIME NEEDED TO EFFECT A REPAIR IS NOT NORMALLY EXCESSIVE FOR ELECTRONIC EQUIPMENT GIVEN THAT SUFFICIENT REPLACEMENT PARTS ARE AVAILABLE. IF A MANUFACTURER DESTROYS HIS INVENTORY OF A SPECIFIC PART DUE TO THE LACK OF ADEQUATE ESD CONTROLS, THE EQUIPMENT COULD BE DOWN FOR A SUBSTANTIAL PERIOD AWAITING PRODUCTION AND DELIVERY OF A REPLACEMENT PART.

IN THE FIELD THE USER NORMALLY ABSORBS THE BURDEN OF THESE COSTS EXCEPT IN INSTANCES WHERE THE MANUFACTURER WARRANTS THE EQUIPMENT. IN EITHER CASE, SUCH COSTS CAN BE SUBSTANTIAL IF THE MANUFACTURER MUST SEND A FIELD ENGINEER TO A USER FACILITY TO EFFECT A REPAIR.

FOR THE USER, EQUIPMENT FAILURES RESULTING FROM ESD CAN REQUIRE INCREASED MAN-LOADING TO KEEP THE EQUIPMENT OPERATIONAL, INCREASED SPARES USAGE, GREATER BURDEN ON THE SUPPLY SYSTEM, AND OTHER LOGISTICS SUPPORT COST INCREASES.

AN INCREASE IN THE NUMBER OF FAILURES MEANS A DECREASE IN EQUIPMENT REALIBILITY, INCREASED DOWNTIME FOR MAINTENANCE AND INCREASED

PROBABILITY OF WAITING FOR A SPARE PART THAT IS NOT ON HAND. THIS DE-CREASE IN RELIABILITY AND INCREASE IN DOWNTIME MEANS LOWER AVAILABILITY OF THAT EQUIPMENT.

ALL OF THE ABOVE RELATE TO HIGHER LIFE CYCLE COSTS FOR AN EQUIPMENT WHETHER THEIR COSTS BE BORNE BY THE MANUFACTURER OR USER. FOR MILTIARY EQUIPMENT CRITICAL TO COMBAT SITUATIONS THE DECREASED RELIABILITY AND INCREASED DOWNTIME RELATES TO DECREASED MILITARY READINESS AND EFFEC-TIVENESS.

#### II. PRINCIPLES OF STATIC ELECTRICITY

#### A. BACKGROUND

STATIC ELECTRICITY IS THE OLDEST KNOWN FORM OF ELECTRICITY. THE GREEKS WERE ACQUAINTED WITH ELECTRIFICATION OF SUBSTANCES BY FRICTION. IN FACT, THE WORD "ELECTRON" WAS DERIVED FROM THE GREEK WORD "ELEKTRON" THE NAME FOR AMBER. THE TRUE SCIENTIFIC STUDY OF ELECTRICITY BEGAN IN THE SIXTEENTH CENTURY BY WILLIAM GILBERT OF COLCHESTER, ENGLAND, WHO MADE THE FIRST DETAILED STUDY OF THE PROPERTY WHICH SUBSTANCES ACQUIRE AFTER BEING RUBBED WITH SILK, FLANNEL OR FUR (I.E., THE ATTRACTION OF LIGHT OBJECTS). FURTHER STUDIES OF FRICTIONAL ELECTRICITY WERE PERFORMED IN THE EIGHTEENTH CENTURY BY SCIENTISTS IN ENGLAND, GERMANY AND FRANCE WHO ESTABLISHED THAT ALL SUBSTANCES COULD BE ELECTRIFIED BY RUBBING, BUT THAT SOME SUBSTANCES HAD THE POWER OF CONDUCTION AND COULD DIFFUSE THE ELECTRIC CHARGES OVER THEIR SURFACE. DURING THIS PERIOD ELECTRIC MACHINES WERE DESIGNED EMPLOYING SUL-PHUR OR GLASS BALLS ROTATED BY HAND AND RUBBED ON ANOTHER SUBSTANCE SUCH AS SILK, FLANNEL OR RUBBER. THESE MACHINES WERE CAPABLE OF PRODUCING FAIRLY INTENSE SPARKS. LATER STUDIES BY BENJAMIN FRANKLIN REFERRED TO BODIES AS NEGATIVELY OR POSITIVELY ELECTRIFIED AS THEY EXERTED A FORCE OR REPULSION ON A GLASS ROD RUBBED WITH SILK OR A RESIN STICK RUBBED WITH FLANNEL.

#### B. TRIBOELECTRIC EFFECT

THE PRIME METHOD OF GENERATING STATIC ELECTRICITY IS BY RUBBING OR SEPARATING MATERIALS, ALSO KNOWN AS TRIBOELECTRIC CHARGING. INVESTIGA-TIONS HAVE SHOWN THAT MATERIALS CAN BE RANKED IN ACCORDANCE WITH THEIR ABILITY TO BECOME POSITIVELY CHARGED WITH RESPECT TO OTHER MATERIALS DURING TRIBOELECTRIC CHARGING. THIS RANKING IS KNOWN AS A TRIBOELECTRIC SERIES.

A MATERIAL UPPERMOST IN THE SERIES BECOMES POSITIVELY CHARGED WHEN RUBBED WITH A MATERIAL LOWER IN THE SERIES; THE MATERIAL LOWER IN THE SERIES BE-COMES NEGATIVELY CHARGED. ONE OF THE MANY VERSIONS OF THE SERIES IS SHOWN IN TABLE II-A. CONDITIONS SUCH AS CLEANLINESS, VARIATION IN CHEMICAL COMP-OSITION AND PROCESSES, HUMIDITY AND THE MECHANICS OF RUBBING OR SEPARATION (E.G., SPEED, CONTACT PRESSURE) AFFECT THE SERIES TO A GREAT EXTENT. THUS THE RANKING OF ELEMENTS OR COMPOUNDS IN THE SERIES WILL NOT ALWAYS BE REPRODUCIBLE.

TRIBOELECTRIC GENERATION OF STATIC IS COMMONLY ENCOUNTERED BY PEOPLE WALKING ACROSS A VINYL CARPETED, FINISHED WOOD, SEALED OR PAINTED CONCRETE FLOOR, ESPECIALLY WHEN WEARING SHOES WITH SYNTHETIC SOLES. WAX COMMONLY USED ON WOOD OR VINYL FLOORS NORMALLY ADDS SIGNIFICANTLY TO THIS GENERATION OF STATIC ELECTRICITY. THE CONTACT AND SEPARATION OF THE SHOES FROM THE FLOOR GENERATES THE CHARGE ON THE BOTTOM OF THE SHOES WHICH IN TURN INDUCES A CHARGE ON THE PERSON'S BODY. THE CONTACT, SEPARATION AND RUBBING OF PEOPLE'S CLOTHING AS THEY MOVE THEIR ARMS OR LEGS AND THE SEPARA-TION OF A PERSON'S CLOTHING FROM A CHAIR SEAT MADE OF SYNTHETIC MATERIALS (E.G., VINYL OR FINISHED WOOD) CAN ALSO GENERATE SUBSTANTIAL ELECTROSTATIC CHARGES ON PERSONNEL. IN GENERAL, ALMOST ALL MOVEMENTS OF PERSONNEL RESULT IN SOME RELATIVE MOTION OF SUBSTANCES IN THE FORM OF RUBBING OR SEPARATION CREATING VARYING LEVELS OF ELECTROSTATIC CHARGE ON THAT PERSON.

TRIBOELECTRIC GENERATION OF STATIC ELECTRICITY IS NOT LIMITED TO PERSONNEL MOVEMENTS. ALL MACHINERY WITH MOVING PARTS, OR EQUIPMENT OPER-ATION WITH FLOW OF LIQUIDS OR GASES (E.G., PAINT SPRAYERS, FLOW SOLDER MACHINES, DE-GREASERS) CAN ALSO GENERATE SUBSTANTIAL ELECTROSTATIC CHARGES.

ONCE ELECTROSTATIC CHARGES ARE GENERATED BY TRIBOELECTRIC EFFECT OR ANY OTHER CHARGE MECHANISM, AN ELECTROSTATIC FORCE FIELD IS CREATED

TABLE II-A SAMPLE TRIBOELECTRIC SERIES

+

POSITIVE AIR HUMAN HANDS ASBESTOS RABBIT FUR GLASS MICA HUMAN HAIR NYLON WOOL FUR LEAD SILK ALUMINUM PAPER COTTON STEEL WOOD AMBER SEALING WAX HARD RUBBER NICKEL, COPPER BRASS, COPPER GOLD, PLATINUM SULFUR ACETATE RAYON POLYESTER CELLULOID ORLON POLYURETHANE POLYETHYLENE POLYPROPYLENE PVC (VINYL) KEL F SILICON TEFLON

NEGATIVE

BETWEEN THE CHARGED SUBSTANCE AND THE CLOSEST MASS OR GROUND, AND/OR AN OPPOSITELY CHARGED OBJECT. OBJECTS ENTERING THIS ELECTROSTATIC FORCE FIELD WILL BE POLARIZED WITH EQUAL AND OPPOSITE CHARGES ATTRACTED TO THE SURFACES CLOSEST TO THE CHARGED SOURCE AND TERMINATION OF THE FIELD VECTOR (MASS OR GROUND OR ANOTHER OPPOSITELY CHARGED OBJECT IN CLOSE PROXIMITY).

THE ELECTROSTATIC FIELD WILL REMAIN INTACT UNTIL THE CHARGED OBJECT CREATING THE FIELD IS NEUTRALIZED BY SOME FORM OF ESD. THIS ESD CAN OCCUR BY DIRECT DISCHARGE VIA CONTACT WITH AN OPPOSITELY CHARGED OBJECT, BY CONTACT OF THE CHARGED OBJECT WITH A CONDUCTIVE OBJECT OR A GROUND, OR BY SUBJECTING THE CHARGED OBJECT TO IONIZED FLUID FLOW (E.G., FLOW FROM AN AIR IONIZER). THE DISCHARGE BY DIRECT CONTACT CAN BE A SLOW LOW CURRENT DISCHARGE AS OCCURS WHEN THE CHARGED OBJECT COMES IN CONTACT WITH AN OPPOS-ITELY CHARGED OBJECT, CONDUCTVE MASS OR GROUND HAVING A HIGH CONTACT RESIS-TANCE THROUGH WHICH THE CHARGES ARE NEUTRALIZED. THE DISCHARGE CAN ALSO BE IN THE FORM OF A HIGH CURRENT SPARK WHICH OCCURS WHEN THE CHARGE DIFFERENTIAL IS SUFFICIENT ENOUGH TO BREAK DOWN THE DIELECTRIC OF THE AIR GAP BETWEEN A CHARGED OBJECT AND A CONDUCTIVE MASS OR A GROUND. ALTERNATELY, A CORONA DISCHARGE COULD OCCUR WHEN THE CHARGE DIFFERENTIAL BETWEEN THE OPPOSITELY CHARGED OBJECTS, OR THE CHARGED OBJECT AND GROUND, IS SUFFICIENT TO IONIZE THE SURROUNDING AIR BUT IS NOT HIGH ENOUGH TO CAUSE DIELECTRIC BREAKDOWN OF THE AIR SPACE.

#### C. MATHEMATICAL FORMULATION OF ELECTROSTATIC FIELD ANALYSIS

TO HELP AVOID CONDITIONS OR SITUATIONS THAT ARE STATIC GENER-ATIVE, IT IS IMPORTANT THAT THE CONCEPT OF STATIC ELECTRICITY BE UNDERSTOOD. ONE WAY OF ACHIEVING THIS IS TO START BY DEFINING CERTAIN BASIC CONCEPTS AND MATHEMATICAL RELATIONSHIPS. THESE INVOLVE SUCH QUANTITIES AS THE

ELECTROSTATIC FORCES BETWEEN CHARGED BODIES, THE FIELD STRENGTHS PRODUCED BY CHARGED OBJECTS, ELECTROSTATIC POTENTIAL, CAPACITANCE, "RELAXATION TIME" (THE TIME FOR CHARGES TO BE DISSIPATED), AND THE ELECTRICAL ENERGY OF A SYSTEM COMPRISED OF OPPOSITELY CHARGED OBJECTS, OR A CHARGED OBJECT AND GROUND.

#### (1) COULOMB'S LAW

THE FORCE OF ATTRACTION OR REPULSION BETWEEN TWO POINT CHARGES IS PROPORTIONAL TO THE MAGNITUDE OF EACH OF THE CHARGES, INVERSELY PROPORTIONAL TO THE SQUARE OF THE DISTANCE BETWEEN THE CHARGES, AND HAS A DIRECTION ALONG THE LINE JOINING THE TWO CHARGES. THE CONSTANT OF PROPORTION-ALITY IS BASED UPON THE MEDIUM IN WHICH THE CHARGED OBJECTS ARE CONTAINED. IN TERMS OF A MATHEMATICAL EQUATION AND CONSIDERING THE MEDIUM TO BE AIR, THIS CAN BE EXPRESSED AS:

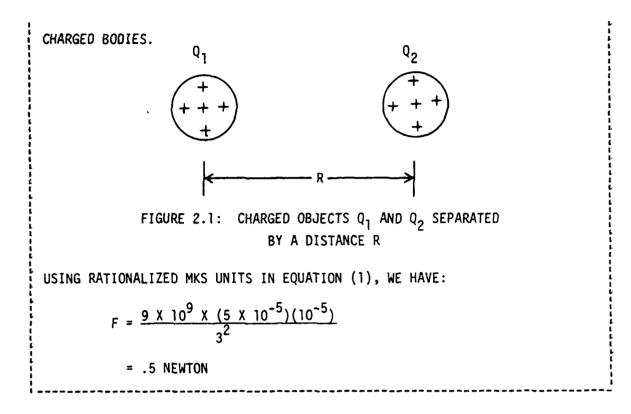

$$F = K \left(\frac{Q_1 Q_2}{R^2}\right) \dots (1)$$

WHERE:

F = FORCE (NEWTONS)  $Q_1 \text{ AND } Q_2 = \text{MAGNITUDES OF THE CHARGES (COULOMB)}$  R = DISTANCE BETWEEN CHARGES (METERS)  $K = \frac{1}{4\pi\epsilon_0} = \text{THE PROPORTIONALITY CONSTANT 9 X 10}^9 \text{ FOR VACUUM} (SOMETIMES USED FOR AIR) (METERS/FARADS)}$   $\epsilon_0 = \text{THE PERMITIVITY OF FREE SPACE (PERFECT VACUUM)}$

EXAMPLE (A): CONSIDER TWO CHARGED BODIES (FIGURE 2.1) HAVING CHARGES  $Q_1 = 5 \times 10^{-5}$  COULOMB AND  $Q_2 = 10^{-5}$  COULOMB AND SEPARATED BY A DISTANCE OF 3 METERS. IT IS REQUIRED TO FIND THE FORCE OF REPULSION BETWEEN THE TWO

#### (2) ELECTRIC FIELD INTENSITY

AN ELECTRIC FIELD IS SAID TO EXIST AT A POINT IF A FORCE OF ELECTRICAL ORIGIN IS EXERTED ON A CHARGED BODY (+q) PLACED AT THAT POINT (FIGURE 2.2). THE FIELD INTENSITY IS A VECTOR QUANTITY E HAVING BOTH DIREC-TION AND MAGNITUDE IN TERMS OF FORCE PER UNIT CHARGE. THUS THE ELECTRIC INTENSITY IN AIR DUE TO CHARGE Q IS GIVEN AS:

THE ELECTRIC FIELD INTENSITY HAS THE SAME DIRECTION AS THE FORCE F ACTING ON A SMALL POSITIVE CHARGE +q

#### FIGURE 2.2: CALCULATION OF FIELD INTENSITY

$$E = \frac{F}{q} = \frac{1}{4\pi\epsilon_{0}} \times \frac{Q}{R^{2}} = \frac{1}{4\pi\times8.85 \times 10^{-12} \frac{FARAD}{METER}} \times \frac{Q}{R^{2}} \frac{COULOMB}{(METER)^{2}}$$

$$= 9 \times 10^{9} \frac{Q}{R^{2}} \frac{(COULOMB}{(FARAD - METER)} \dots \dots \dots (2)$$

IN PRACTICAL APPLICATIONS, ELECTRIC FIELDS ARE USUALLY PRODUCED BY CHARGES DISTRIBUTED OVER A SURFACE RATHER THAN A POINT SOURCE; HENCE THE VECTOR SUM OF THE CHARGE IS USED TO EXPRESS THE ELECTRIC FIELD.

WHERE:

R = DISTANCE BETWEEN THE POINT OF INTEREST AND CHARGE (METERS) $A_R = UNIT VECTOR IN THE DIRECTION OF THE FIELD$

FOR MANY POINT CHARGES:

$$E = \sum_{i=1}^{n} (K Q_i / R^2) \dots (4)$$

E IN A GIVEN DIRECTION X IS:

$$E_{\chi} = \sum_{j=1}^{n} (K Q_{j}/R^{2}) \cos \theta$$

..... (5)

WHERE:

0 IS THE ANGLE BETWEEN THE ELECTRIC FIELD INTENSITY VECTOR AND THE X DIRECTION.

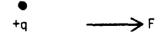

EXAMPLE (B) (CONTINUED)

$$E_{1Y} = -180 \times 10^{3} \text{ SIN } 90^{\circ}$$

$$= -180 \times 10^{3} \text{ NEWTON/COULOMB}$$

$$E_{2X} = 27 \times 10^{3} \text{ COS } (\cos^{-1} \frac{1.2}{1.2})$$

$$= 24.92 \times 10^{3} \text{ NEWTON/COULOMB}$$

$$E_{2Y} = 27 \times 10^{3} \text{ SIN } (\cos^{-1} \frac{1.2}{1.3})$$

$$= 10.37 \times 10^{3} \text{ NEWTON/COULOMB}$$

USING EQUATION (5), THE NET ELECTRIC INTENSITY IN THE X DIRECTION,  $E_{X}$  IS:

$$E_{X} = E_{1X} + E_{2X} \qquad \text{AND}$$

$$E_{1X} + E_{2X} = 0 + 24.92 \times 10^{3}$$

$$= 24.92 \times 10^{3} \text{ NEWTON/COULOMB}$$

NET ELECTRIC INTENSITY IN THE Y DIRECTION,

$$E_{Y} = E_{1Y} + E_{2Y} = -180 \times 10^{3} + 10.37 \times 10^{3}$$

$$= -169.63 \times 10^{3} \text{ NEWTON/COULOMB}$$

THUS THE RESULTANT ELECTRIC FIELD INTENSITY AT X, E:

$$= \sqrt{E_{X}^{2} + E_{Y}^{2}}$$

$$= 171.45 \times 10^{3} \text{ NEWTON/COULOMB} \text{ AT AN ANGLE OF 8.35^{\circ}}$$

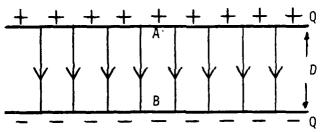

ELECTRIC FIELD BETWEEN OPPOSITELY CHARGED OBJECTS (TWO PLATES OF A CAPACITOR) IS OFTEN EXPRESSED IN TERMS OF POTENTIAL DIFFERENCE BETWEEN THE TWO OBJECTS DIVIDED BY THE DISTANCE BETWEEN THEM.

PARTS SENSITIVE TO ELECTRIC FIELDS CAN BE DAMAGED IF SUBJECTED TO A HIGH ENOUGH ELECTRIC FIELD INTENSITY. MOS PARTS ARE SUCH PARTS BECAUSE OF THEIR VERY THIN ( $600-1000A^{\circ}$ ) INSULATING OXIDE (COMMONLY  $sio_2$ ) LAYERS. SINCE THE BREAKDOWN VOLTAGE OF  $sio_2$  IS 6 X  $10^{6}$ V/CM, A VOLTAGE OF ONLY 60 VOLTS ACROSS  $1000A^{\circ} sio_2$  LAYER OF A MOS PART CAN CAUSE BREAKDOWN AND PART FAILURE.

THE PROTECTION OF ELECTRONIC PARTS FROM ELECTRIC FIELD CAN BE ACHIEVED BY USING A CONDUCTIVE BAG DURING STORAGE, TRANSPORTATION AND HANDLING. THE PRINCIPLE OF THIS TYPE OF PROTECTION CAN BE UNDERSTOOD FROM FIGURE 2.4 WHICH SHOWS A CROSS-SECTION OF A CONDUCTING BAG AND AN INSULATING BAG PLACED IN A UNIFORM ELECTRIC FIELD. NOTE THAT THE ELECTRIC FIELD PASSES THROUGH THE INSULATOR BUT TERMINATES ON THE SURFACE OF THE CONDUCTOR. THIS SHOWS THAT A PART WITHIN AN INSULATOR IS DEFINITELY NOT SHIELDED FROM AN ELECTRIC FIELD, SUCH AS IS GENERATED FROM A CHARGED PERSON. SINCE MANY MATER-IALS ARE NOT PURELY CONDUCTIVE (I.E., ZERO RESISTANCE) OR PERFECT INSULATORS (I.E., INFINITE RESISTANCE) MATERIALS PROVIDE PARTIAL SHIELDING FROM ELECTRO-STATIC FIELDS DEPENDING UPON THE CONDUCTIVITY OF THE MATERIAL.

Lines of electric field terminate at the surface of a conductive sphere (a) Lines of electric field pass through an insulating sphere (b)

FIGURE 2.4: (A) CONDUCTOR AND (B) INSULATOR IN A UNIFORM ELECTRIC FIELD

(3) ELECTROSTATIC POTENTIAL

IN A REGION IN WHICH THERE IS AN ELECTRIC FIELD, AN ELEC-TRIC CHARGE EXPERIENCES A FORCE. IF THE CHARGE MOVES FROM ONE POINT (A) TO ANOTHER POINT (B), (FIGURE 2.5), EITHER THE FIELD DOES WORK ON THE CHARGE OR OUTSIDE ENERGY IS REQUIRED TO OVERCOME THE ELECTRICAL FORCES AND TO EFFECT THE MOTION. THE MAGNITUDE OF THIS WORK IS INDEPENDENT OF THE PATH TAKEN FROM A TO B. THUS THE ELECTROSTATIC POTENTIAL BETWEEN A AND B, IN VOLTS, IS A SCALAR QUANTITY DEFINED AS THE WORK IN JOULES PER COULOMB DONE BY THE ELECTRICAL FORCES WHEN A SMALL POSITIVE TEST CHARGE IS MOVED FROM A TO B.

FIGURE 2.5: FIELD BETWEEN TWO CHARGED PLATES

IF A IS AT A HIGHER POTENTIAL THAN B, THE WORK IS POSITIVE AND THE FORCES EXERTED BY THE ELECTRIC FIELD PUSH THE POSITIVE CHARGE DOWN THE POTENTIAL HILL FROM A TO B. IF, ON THE OTHER HAND, THIS WORK IS NEGATIVE, INDICATING THAT OUTSIDE ENERGY MUST BE SUPPLIED TO OVERCOME THE FORCES OF THE ELECTRIC FIELD, A IS SAID TO BE AT A LOWER POTENTIAL THAN B. NOTE THAT DIFFERENCE OF POTENTIAL IS DEFINED IN TERMS OF WORK DONE ON A POSITIVE CHARGE.

CONSIDER THE DIFFERENCE OF POTENTIAL FOR TWO CHARGED PLATES BETWEEN WHICH THERE IS A UNIFORM ELECTRIC FIELD AS SHOWN IN FIGURE 2.5. AT ANY POINT BETWEEN THE PLATES, A SMALL TEST CHARGE +q EXPERIENCES A DOWNWARD ELECTROSTATIC FORCE:

$$F = qE$$

IN THE MOTION FROM A TO B, THIS FORCE DOES WORK:

$W_{A \rightarrow B} = F.X = qE.X$  ......(6)

$= qE.X$

THE WORK DONE PER COULOMB OF CHARGE IS:

$$W_{A \rightarrow B}/q = E.X$$

WHERE E IS IN NEWTON/COULOMB AND X IS IN METERS, THIS IS EQUIVALENT TO JOULES/COULOMB WHICH, BY DEFINITION, IS THE DIFFERENCE OF POTENTIAL BETWEEN A AND B IN VOLTS. THIS DIFFERENCE OF POTENTIAL IS USUALLY DENOTED BY  $V_A - V_B$ . THEREFORE,

$$V_{A} - V_{B} = EX$$

.....(7)

SINCE:

$$1 \frac{\text{VOLT}}{\text{METER}} = 1 \frac{\text{NEWTON}}{\text{COULOMB}}$$

WHERE VOLT/METER IS USUALLY USED AS THE UNIT OF ELECTRIC INTENSITY AND IS FREQUENTLY CALLED POTENTIAL GRADIENT; OR THE POTENTIAL PER UNIT OF DISTANCE.

(4) MAXIMUM POTENTIAL

IF THE CHARGE ON A BODY WERE ABLE TO BUILD UP INDEFINITELY, THEN THE POTENTIAL WOULD HAVE NO UPPER LIMIT. FORTUNATELY, THIS IS NOT TRUE. THE MAXIMUM CHARGE THAT CAN BE RETAINED BY AN OBJECT IN AIR IS LIMITED BY THE FACT THAT THE AIR ITSELF BECOMES CONDUCTIVE AT AN ELECTRIC FIELD OF ABOUT 3 X  $10^6$  V/M. FOR EXAMPLE, THE MAXIMUM POTENTIAL THAT A METALLIC SPHERICAL BODY IN AIR CAN ACHIEVE IS:

$$V_{MAX} = R E_{MAX} (VOLTS) .....(8)$$

= R (3 X 10<sup>6</sup>) (VOLTS)

WHERE:

V<sub>MAX</sub> = MAXIMUM POTENTIAL (VOLTS)

E<sub>MAX</sub> = MAXIMUM ELECTRIC FIELD (VOLTS/METERS)

R = RADIUS OF THE SPHERE (METER)

EXAMPLE (C): FOR A SPHERE OF 5 CM RADIUS: V<sub>MAX</sub> = (.05) (3 X 10<sup>6</sup>) = 150,000 VOLTS

(5) CAPACITANCE

IF TWO CONDUCTIVE PLATES ARE SEPARATED FROM EACH OTHER BY AN INSULATING (DIELECTRIC) MATERIAL, A CAPACITANCE WILL EXIST BETWEEN THEM. ANY OPPOSITE STATIC CHARGE THAT BUILDS UP ON THESE PLATES WILL CHARGE THIS CAPACITOR. A CAPACITOR CAN BE CHARGED BY: (1) ELECTRICALLY SHORTING AND PLACING THESE PLATES IN AN ELECTROSTATIC FIELD (WITH THE PLATES PERPENDICULAR TO THE ELECTRIC FIELD INTENSITY VECTOR) AND REMOVING THE SHORT PRIOR TO REMOVING THESE PLATES FROM THE ELECTROSTATIC FIELD, (2) BY CHARGING THE PLATES DIRECTLY WITH EQUAL AND OPPOSITE CHARGES, OR (3) BY CHARGING ONE PLATE AND GROUNDING THE OTHER. THE VOLTAGE LEVEL TO WHICH THIS CAPACITOR WILL BE CHARGED IS EQUAL TO:

$V = \frac{Q}{C} \qquad (9)$

WHERE:

- V = VOLTAGE (VOLTS)

- Q = CHARGE (COULOMBS)

- C = CAPACITANCE (FARADS)

IT CAN BE SEEN THAT THE VOLTAGE ACROSS A CAPACITOR IS DIRECTLY PROPORTIONAL TO ITS STORED CHARGE AND INVERSELY PROPORTIONAL TO ITS CAPACITANCE. THE CAPACITANCE (C) OF THE TWO CHARGED PLATES OF OVERLAPPING AREA (A) (SQUARE METERS) SEPARATED BY A DIELECTRIC OF THICKNESS (D) IN METERS IS EQUAL TO:

$$C = \varepsilon_0 \varepsilon_r \frac{A}{D} (FARADS) .... (10)$$

= 8.85  $\varepsilon_r \frac{A}{D} 10^{-12} (FARADS)$

WHERE:

$\boldsymbol{\varepsilon}_{\!\!\boldsymbol{\tau}}$  is the relative permitivity of the dielectric

$\varepsilon_{0}$  IS THE PERMITIVITY OF FREE SPACE = 1/(36 T X 10<sup>9</sup>) FARADS/ METERS (RATIONALIZED MKS UNITS) 23.

EXAMPLE (D): LET THE TWO PLATES OF A MOS CAPACITOR BE SEPARATED BY A DISTANCE OF 1000Å OF SiO<sub>2</sub> ( $\varepsilon_r = 10$ ) WITH 5 MILLIMETERS<sup>2</sup> AS THE AREA OF THE SMALLER ONE. IT IS REQUIRED TO FIND THE CAPACITANCE OF THIS MOS PART AND THE CHARGE ON EITHER PLATE WHEN THE DIFFERENCE OF POTENTIAL BETWEEN THE PLATES IS 100V. USING EQUATION (10), THE CAPACITANCE (C) IS:

C = 8.85 (10)

$$\frac{5 \times 10^{-6}}{10^3 \times 10^{-10}} \times 10^{-12}$$

FARAD

$= 4425 \mu \mu f$

USING EQUATION (9), THE CHARGE ON EACH PLATE Q IS:

Q = VC

=  $100 \times 4425 \times 10^{-12}$  COULOMB

= .4425 µC

#### (6) DIELECTRIC STRENGTH

THE REASON FOR USING A DIELECTRIC BETWEEN THE PLATES IS NOT SOLELY FOR MECHANICAL CONVENIENCE. A DIELECTRIC IMPROVES THE CAPACITOR ELECTRICALLY IN TWO WAYS: (1) IT INCREASES THE CAPACITANCE, AND (2) IT PERMITS THE USE OF HIGHER VOLTAGES WITHOUT DANGER OF BREAKDOWN OR FLASHOVER BETWEEN THE CAPACITOR PLATES. BREAKDOWN IS RELATED TO A PROPERTY OF A DIELECTRIC CALLED DIELECTRIC STRENGTH. THE DIELECTRIC STRENGTH OF A MATERIAL IS THE MAXIMUM POTENTIAL GRADIENT (VOLTS/METERS) THAT THE MATERIAL CAN WITH-STAND WITHOUT RUPTURE. DIELECTRIC STRENGTH MUST NOT BE CONFUSED WITH OFFLECTRIC CONSTANT. THE DIELECTRIC CONSTANT OF A MATERIAL IS THE RATIO OF THE CAPACITANCE OF A CAPACITOR WITH A GIVEN DIELECTRIC MATERIAL BETWEEN THE PLATES TO THE CAPACITANCE OF A CAPACITOR WITH VACUUM BETWEEN THE PLATES. THE DIELECTRIC CONSTANT DETERMINES HOW MUCH CHARGE A GIVEN CAPACITOR WILL STORE WITH A GIVEN POTENTIAL DIFFERENCE; DIELECTRIC STRENGTH DETERMINES HOW MUCH VOLTAGE THIS CAPACITOR WILL STAND WITHOUT BREAKING DOWN.

EXAMPLE (E): THE DIELECTRIC STRENGTH OF THERMAL  $sio_2$  is in the range of 5-8 x  $10^6$ V/CM. IF WE ASSUME THE DIELECTRIC STRENGTH OF THE  $sio_2$  used in the mos device of example (c) to be 6 x  $10^6$ V/CM, then a  $1000^{\circ}$  layer will fail at a voltage of only 60 volts as calculated below:

MAXIMUM VOLTAGE TO BREAKDOWN = 6 X  $10^6 \frac{V}{CM} \times 1000 \times 10^{-8} \text{ cm}$

#### ≈ 60V

THUS FOR A 5 MILLIMETER<sup>2</sup> CAPACITOR (SEE EXAMPLE (D), A Q OF .4425  $\mu$  C ON EITHER PLATE CORRESPONDING TO THE POTENTIAL DIFFERENCE BETWEEN THE PLATES OF 100 VOLTS WILL DAMAGE THE DEVICE VIA DIELECTRIC BREAKDOWN.

#### (7) TYPICAL EXAMPLES OF A CAPACITOR

TYPICAL EXAMPLES OF CAPACITORS ENCOUNTERED IN THE FIELD OF ELECTRONICS ARE HUMANS, TOTE BOXES (AND OTHER CONTAINERS, TRAYS, ETC.) AND ELECTRONIC PARTS.

(a) HUMAN CAPACITANCE

THE HUMAN CAPACITANCE C<sub>H</sub> IS DIVIDED INTO TWO MAJOR PARTS: THE PARALLEL PLATE CAPACITANCE OF THE SOLES OF THE FEET TO GROUND, AND CAPACITANCE OF THE BODY BULK TO GROUND. THE CAPACITANCE OF A PERSON IS A FUNCTION OF HIS PROXIMITY TO OTHER OBJECTS. THIS CAPACITANCE CAN CHANGE SIGNIFICANTLY DURING SIMPLE MOVEMENTS SUCH AS LEANING FORWARD IN A CHAIR, PICKING UP ONE OR BOTH FEET FROM THE FLOOR, OR STANDING UP, AS IS SHOWN IN TABLE II-B. HUMAN CAPACITANCE CAN VARY FROM 50 TO SEVERAL THOUSAND PICO~ FARADS (PF).

#### TABLE II-B (REFERENCE 6)

| DESCRIPTION OF                                                              | % CHANGE IN CAPACITANCE DUE TO MOVEMENT |                      |              |  |

|-----------------------------------------------------------------------------|-----------------------------------------|----------------------|--------------|--|

| MOVEMENT                                                                    | INITIAL<br>CAPACITANCE                  | FINAL<br>CAPACITANCE | % CHANGE     |  |

| PERSON SEATED, RAISING ONE<br>FOOT                                          | 192                                     | 163                  | 15% DECREASE |  |

| PERSON SEATED, PICKING UP<br>BOTH FEET AND PLACING<br>THEM ON THE FOOT REST | 192                                     | 129                  | 33% DECREASE |  |

| PERSON SEATED, LEANING<br>FORWARDS IN CHAIR (DESK<br>TYPE CHAIR WITH BACK)  | 192                                     | 184                  | 4% DECREASE  |  |

| STANDING PERSON RAISING<br>ONE FOOT                                         | 167                                     | 141                  | 16% DECREASE |  |

| SEATED PERSON STANDING UP                                                   | 192                                     | 167                  | 13% DECREASE |  |

### CAPACITANCE CHANGES IN PERSONNEL IN A WORK AREA

#### (b) CONDUCTIVE TOTE BOX CAPACITANCE

CONDUCTIVE TOTE BOXES HAVE BEEN FOUND TO VARY IN CAPACITANCE FROM 35-300 PF DEPENDING ON THEIR SIZE AND SHAPE. A TYPICAL VALUE OF THE CAPACITANCE OF A TOTE BOX TO GROUND PLANE (17 CM WIDE, 24 CM LONG AND 15 CM HIGH) IS 138 PF. THE EFFECT OF THIS CAPACITANCE TO THE DIS-CHARGE OF CONDUCTIVE TOTE BOX TO GROUND IS DISCUSSED IN REFERENCE 6.

#### (c) MOS CAPACITOR

THE CAPACITANCE BETWEEN THE METAL GATE AND SEMICONDUCTOR

OF A MOS FIELD EFFECT TRANSISTOR (FET) WITH SiO<sub>2</sub> AS THE DIELECTRIC FORMS ANOTHER TYPE OF CAPACITOR COMMON IN MANY INTEGRATED CIRCUITS.

(d) REVERSE BIASED P-N JUNCTION

THE DEPLETION LAYER OF THE REVERSE BIASED P-N JUNCTION DIODE CONSTITUTES A VOLTAGE DEPENDENT CAPACITOR, POPULARLY KNOWN AS A VARACTOR.

#### (8) ENERGY STORAGE

ASSUME THE SYSTEM WHERE THE CAPACITANCE (C) IS UNCHARGED AND HENCE HAS ZERO POTENTIAL DIFFERENCE BETWEEN ITS PLATES. LET US ALSO ASSUME THAT THERE IS NO DISSIPATIVE ELEMENTS IN THE STORAGE SYSTEM AND THAT THE STORED ENERGY W IS A FUNCTION OF SOME POSITION VARIABLE (E.G., PLATE SEPARATION X) AND THE CHARGE Q. SINCE THE CAPACITOR IS INITIALLY UNCHARGED, AND SINCE NO ELECTRICAL FORCES ARE INVOLVED IN PUTTING IT TOGETHER MECH-ANICALLY, THE CHANGE IN ENERGY dW AS CHARGE IS MOVED FROM ONE PLATE TO THE OTHER IS:

dW = VdQ(11)

WHERE V (VOLTS) IS THE POTENTIAL THROUGH WHICH THE CHARGE dQ MOVES IN BEING CARRIED FROM ONE PLATE TO THE OTHER. IF WE BEGIN WITH THE UNCHARGED SYSTEM AND CHARGE IT TO A POTENTIAL V BY TRANSFERRING A CHARGE Q (COULOMBS), AN EXTERNAL SOURCE MUST ADD W (JOULES) ENERGY TO THE SYSTEM WHERE:

BUT AS BEFORE V = Q/C, WHICH MEANS THAT:

$$W = \int_{0}^{Q} \frac{QdQ}{C} = \frac{1}{2} \frac{Q^{2}}{C}$$

(13)

FOR THE ENERGY STORED IN THE CAPACITOR. EXPRESSING ENERGY FUNCTION IN TERMS OF POTENTIAL (V) IN VOLTS AND (C) IN FARADS:

EXAMPLE (F): CONSIDER A PERSON TOUCHING A CHARGED OBJECT THAT HAS A PO-TENTIAL OF (V) VOLTS AND ENOUGH CHARGE (Q) TO FULLY CHARGE THAT PERSON'S CAPACITANCE ( $C_{H}$ ). THE AMOUNT OF CHARGE WOULD BE:

$Q = C_H V$  COULOMBS

=  $100 \times 10^{-12}$ V (COULOMB), FOR C = 100 PF

IF THAT CHARGE SOURCE IS OF 1000 VOLTS, THE TOTAL ENERGY (E) ABSORBED BY THAT PERSON WOULD BE:

$$W = \frac{1}{2} CV^2 \text{ JOULES}$$

= (.5) (100 X 10<sup>-12</sup>) X (10<sup>3</sup>)<sup>2</sup>

= 50 JOULES

SINCE:

CV = Q $W = \frac{1}{2} QV$

IF THAT PERSON'S CAPACITANCE IS HALVED (AS BY LIFTING ONE FOOT OFF THE GROUND AFTER BEING CHARGED (CHARGE REMAINING CONSTANT), THE VOLTAGE AND THE ENERGY

WOULD BE DOUBLED. THIS SAME LINEAR RELATIONSHIP EXISTS FOR OTHER INCREASE IN VOLTAGES WITH A CORRESPONDING DECREASE IN CAPACITANCE (I.E., CONSTANT Q).

VARIOUS STUDIES HAVE SHOWN THAT SEMICONDUCTOR PARTS CAN BE DEGRADED BY A SINGLE VERY SHORT LOW ENERGY PULSE CHARACTERISTIC OF AN ELEC-TROSTATIC DISCHARGE. ESPECIALLY MOS INTEGRATED CIRCUITS, BIPOLAR INTEGRATED CIRCUITS WITH EXTREMELY SMALL GEOMETRIES AND MINIATURE FILM RESISTORS OF HIGH SHEET RESISTIVITY CAN BE DAMAGED BY AS LITTLE AS 3 PICOJOULES OF STATIC ENERGY.

#### III. CHARGING AND DISCHARGING

#### A. INTRODUCTION

THERE ARE MANY WAYS TO DEVELOP A STATIC CHARGE. CONTACT CHARGING, TRIBOELECTRIC CHARGING (A FORM OF CONTACT CHARGING), INDUCTION CHARGING, CHARGING BY FREEZING, ION AND ELECTRON BEAM CHARGING, AND SPRAY CHARGING ARE A FEW OF THE MOST COMMON METHODS AND MOST APPLICABLE TO ESD. IN THE ELECTRONICS INDUSTRY, STATIC CHARGING CAN POSE A SERIOUS PROBLEM IN MANY AREAS. IF THE MECHANISMS OF CHARGING ARE UNDERSTOOD, ONE IS BETTER EQUIPPED TO AVOID SITUATIONS WHICH ARE SUSCEPTIBLE TO THE HAZARDS OF STATIC CHARGES. ALSO, THE ASSEMBLY, REPAIR AND OTHER PERSONNEL WHO HANDLE ESDS ITEMS WILL BECOME MORE AWARE OF THE METHODS TO CONTROL STATIC TO SAFE LEVELS. IN THE NEXT FEW SECTIONS THESE COMMON MECHANISMS OF CHARGING ARE DISCUSSED IN DETAIL.

ALSO DISCUSSED ARE THE MECHANISMS OF "BLEEDING-OFF" STATIC CHARGES. CHARGED SUBSTANCES ACT AS CAPACITORS WITH THE CHARGED SURFACE OF THE CHARGED OBJECT ACTING AS ONE PLATE OF THE CAPACITOR, AIR OR OTHER INSUL-ATORS AS THE DIELECTRIC AND A NEARBY CONDUCTIVE MASS OR GROUND ACTING AS THE SECOND CAPACITOR PLATE. FOR EXAMPLE, A CHARGED PERSON HAS A CAPACITANCE RELATIVE TO GROUND WITH THE DIELECTRIC BEING THE PERSON'S SHOE SOLES AND PERHAPS THE FLOOR. THE GROUND FORMS THE SECOND CAPACITOR PLATE. THEREFORE, THE PHENOMENA OF ELECTROSTATIC DISCHARGE IS SIMILAR TO THE DISCHARGE OF A CAPACITOR CHARGED TO SOME ELECTROSTATIC VOLTAGE POTENTIAL, USUALLY DISCHARGED THROUGH A RESISTANCE SUCH AS THE HUMAN BODY BULK AND SKIN CONTACT RESISTANCE, WORK TABLE TOP RESISTANCE, AND/OR THE RESISTANCE OF AN ELECTRONIC PART. THE TIME CONSTANT OF THIS RESISTANCE-CAPACITANCE (RC) CIRCUIT IS OF PRIME IMPOR-TANCE IN DETERMINING THE DECAY RATE OF THE DISCHARGE. A MATHEMATICAL FORMULATION OF THIS SITUATION ALONG WITH A NUMBER OF NUMERICAL EXAMPLES ARE CITED AT THE END OF THIS SECTION.

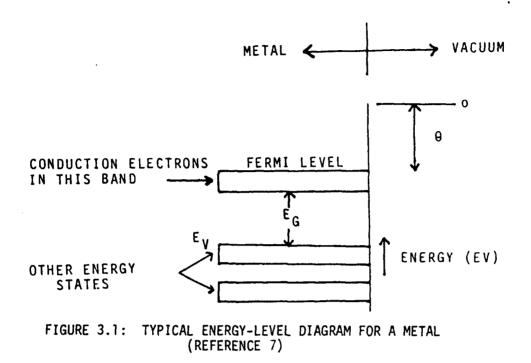

## (1) CONTACT CHARGING

THE CONCEPT OF CONTACT CHARGING WILL BE BETTER UNDERSTOOD IF WE START WITH THE ENERGY-LEVEL DIAGRAM REPRESENTATION OF A MATERIAL. AN ENERGY-LEVEL DIAGRAM FOR THE ELECTRONS IN A METAL INDICATES THE ENERGY STATES OF THE ELECTRONS WITH RESPECT TO A REFERENCE LEVEL OUTSIDE THE METAL (THE "VACUUM" ENERGY LEVEL). A TYPICAL ENERGY-LEVEL DIAGRAM FOR A METAL IS SHOWN IN FIGURE 3.1.  $E_C$  AND  $E_V$  ARE THE EDGES OF THE CONDUCTION BAND AND VALENCE BAND RESPECTIVELY WHERE ELECTRONS AND HOLES (ABSENCE OF ELECTRONS) CAN MOVE IN A CRYSTAL STRUCTURE.

## (a) VALENCE BAND

THE OUTERMOST ELECTRONS ORBITING AROUND THE NUCLEUS OF AN ATOM ARE CALLED VALENCE ELECTRONS. ALSO EACH ELECTRON HAS ITS OWN ENERGY STATE DIFFERENT FROM THAT OF ANOTHER ELECTRON (PAULI EXCLUSION PRINCIPLE). THUS THE VALENCE ELECTRONS OCCUPY A BAND OF ENERGY LEVELS, INSTEAD OF A SINGLE ENERGY LEVEL (STATE). THIS ENERGY BAND IS CALLED THE VALENCE BAND.

## (b) CONDUCTION BAND

THE CONDUCTION BAND IS A PARTIALLY FILLED ENERGY BAND IN WHICH ELECTRONS MOVE FREELY ALLOWING AN ELECTRIC CURRENT TO FLOW THROUGH THE MATERIAL.

THE VALENCE BAND AND THE CONDUCTION BAND ARE NORMALLY SEPARATED BY A FORBIDDEN ENERGY GAP ( $E_G$ ) (FIGURE 3.1) WHERE ELECTRONS DO NOT EXIST. THE CONDUCTIVITY OF A MATERIAL DEPENDS ON THE NUMBER OF ELECTRONS IN THE CONDUCTION BAND AND THE NUMBER OF HOLES IN THE VALENCE BAND. FOR A VALENCE ELECTRON TO BECOME A CONDUCTION ELECTRON, A MINIMUM ENERGY EQUAL TO

THE FORBIDDEN GAP ENERGY HAS TO BE SUPPLIED TO THAT ELECTRON.

THE FERMI LEVEL INDICATED IN FIGURE 3.1 IS INSIDE THE CONDUCTION BAND. THIS CONCEPT IS TRUE ONLY FOR METALS AND HEAVILY DOPED SEMICONDUCTORS. IN MODERATELY DOPED AND UNDOPED (INTRINISIC) SEMICONDUCTORS THE FERMI LEVEL IS WITHIN THE BAND GAP OF THE MATERIAL REPRESENTED BY  $E_G$  OF FIGURE 3.1. THE CONCEPT OF FERMI-LEVEL CAN BE ILLUSTRATED FROM THE FERMI-DIRAC DISTRIBUTION FUNCTION, F(E), WHICH IS ACTUALLY THE ENERGY DISTRIBUTION FUNCTION FOR THE ELECTRONS. THE FERMI-DIRAC DISTRIBUTION FUNCTION IS WRITTEN AS FOLLOWS:

$$F(E) = \frac{1}{1 + EXP (E-E_F)/KT}$$

(15)

WHERE:

E = ENERGY OF DESIRED ENERGY LEVEL

$E_F$  = THE FERMI ENERGY, THE ENERGY AT WHICH F(E) =  $\frac{1}{2}$

F(E) = THE PROBABILITY THAT AN ENERGY STATE, E, IS OCCUPIED BY AN ELECTRON

K = THE BOLTZMANN CONSTANT

$T = TEMPERATURE (^{O}K)$

AS INDICATED IN FIGURE 3.1, IT IS NECESSARY TO GIVE THE ELECTRONS IN A METAL AN AMOUNT OF ENERGY EQUAL TO 0, THE WORK FUNCTION:

IN ORDER FOR THEM TO ESCAPE FROM THE METAL WITH NO KINETIC ENERGY. THIS CAN BE DONE BY HEATING THEM (THERMIONIC EMISSION), BY INTRODUCING A STRONG ELEC-TRIC FIELD (FIELD EMISSION), BY IMPACT WITH OTHER ELECTRONS (SECONDARY EMISSION), OR BY OTHER MEANS.

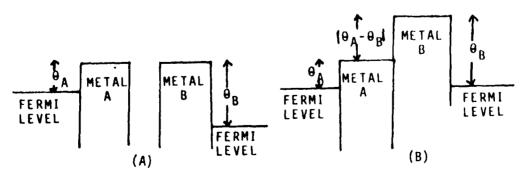

IF TWO DISSIMILAR METALS COME IN CONTACT THERE WILL BE A TRANSFER OF ELECTRONS FROM ONE MATERIAL TO THE OTHER UNTIL THE POTENTIALS OF THE MATERIALS ARE SUCH THAT THE FERMI LEVELS ARE ALIGNED AS INDICATED IN FIGURE 3.2. IN THIS CASE, ELECTRONS HAVE BEEN TRANSFERRED FROM MATERIAL A TO MATERIAL B TO ALIGN THE FERMI LEVELS. THE POTENTIAL DIFFERENCE ( $V_{A-B}$ ) BETWEEN THE TWO MATERIALS FOR THE TRANSFERRED CHARGE IS EQUAL TO THE DIFFERENCE IN THE WORK FUNCTIONS ( $\Theta_A - \Theta_B = e \cdot V_{A-B}$ ). THUS, MATERIAL B HAS BECOME NEGA-TIVELY CHARGED AND THE MATERIAL A HAS BECOME POSITIVELY CHARGED.

FIGURE 3.2: (A) METALS ARE SEPARATED; (B) METALS ARE IN CONTACT (REFERENCE 7)

THE SAME BASIC TYPE OF BEHAVIOR CAN BE POSTULATED FOR INSULATING SURFACES IN CONTACT, ALTHOUGH THE DETAILS ARE NOT GENERALLY UNDER-STOOD SINCE THE ENERGY LEVELS ARE NOT WELL DEFINED IN MANY INSULATING MATER-IALS (PARTICULARLY THOSE WHICH ARE AMORPHOUS). IT IS VERY LIKELY THAT ONLY ELECTRONS VERY NEAR THE CONTACTING SURFACES TAKE PART IN THE CHARGING OF HIGHLY INSULATING MATERIALS. IF ANY TWO MATERIALS (A AND B) WHICH HAVE CON-DUCTIVITIES AND PERMITIVITIES  $\sigma_A$ ,  $\sigma_B$ ,  $\varepsilon_A$ , AND  $\varepsilon_B$ , RESPECTIVELY, ARE BROUGHT INTO CONTACT, WE WOULD EXPECT THE CHARGING OF THOSE SURFACES AWAY FROM THE CONTACT AREA TO DEPEND ON THE RELAXATION TIME CONSTANTS  $\tau_A = \varepsilon_A / \sigma_A$  AND  $\tau_B = \varepsilon_B / \sigma_B$ . THESE ARE THE TIME CONSTANTS FOR CHARGE TRANSFER IN THE MATERIALS, AND THEY GIVE A REASONABLE ESTIMATE OF THE TIME NECESSARY FOR REMOTE PORTICES OF THE CONTACTING BODIES TO REACT ELECTRICALLY IN TERMS OF CHARGE DENSITY AFTER CONTACT WITH A CHARGED OBJECT HAS BEEN MADE. THE NET CHARGE SEPARATION OF THESE CONTACTS WILL DEPEND ON THE ELECTRONIC BULK AND SURFACE PROPERTIES OF THE MATERIALS IN CONTACT.

## (2) TRIBOELECTRIC CHARGING

ANOTHER TYPE OF CHARGING, PERHAPS THE MOST COMMON METHOD OF CHARGING AS PREVIOUSLY DISCUSSED, IS TRIBOELECTRIC CHARGING, CAUSED BY RUBBING BETWEEN TWO SURFACES. HOWEVER, IT IS VERY DIFFICULT TO SEPARATE THE PHENOMENA OF CONTACT CHARGING FROM TRIBOELECTRIC (OR CHARGING BY RUBBING).

ALTHOUGH IDEALLY, TRIBOELECTRIC CHARGING REFERS TO CHARGE TRANSFER BY RUBBING (FRICTION) EFFECTS ONLY, COMMON USAGE OF THE TERM TRIBO-ELECTRIC CHARGING LUMPS CONTACT CHARGING AND FRICTIONAL CHARGING OF TWO MATERIALS TOGETHER. TRIBOELECTRIFICATION IS THE RESULT OF MECHANICAL EX-POSURE OF SURFACES THAT ARE MOVING RELATIVE TO ONE ANOTHER CHARGED BY COMING INTO CONTACT. IT IS BELIEVED THIS IS A COMBINATION OF CONTACT CHARGING AIDED BY THE THERMIONIC EMISSION CAUSED BY THE HEAT DUE TO FRICTION.

#### (3) INDUCTION CHARGING

ELECTROSTATIC CHARGES CAN BE INDUCED DUE TO THE PROXIMITY OF A CHARGED OBJECT. THE BASIC DIFFERENCE BETWEEN CONTACT AND INDUCTION CHARGING IS THAT THE CONTACT METHOD REQUIRES ACTUAL PHYSICAL CONTACT BETWEEN TWO OBJECTS WHILE THE INDUCTION METHOD DOES NOT. A BETTER UNDERSTANDING OF THE INDUCTION METHOD IS PROVIDED BY RECOGNIZING THE EXISTENCE OF A STATIC ELECTRIC FORCE FIELD EMINATING FROM A CHARGED BODY. THIS FIELD IS COMPRISED OF LINES OF FORCE WHEREIN OBJECTS OF SIMILAR CHARGE POLARITY REPEL EACH OTHER AND OBJECTS OF UNLIKE CHARGE POLARITY ARE ATTRACTED TO EACH OTHER.

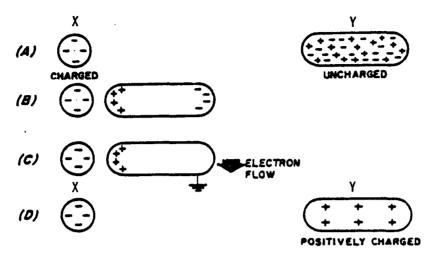

WHEN A CHARGED BODY (X) IS BROUGHT CLOSE TO A NEUTRAL BODY (Y), THE NEUTRAL BODY (Y) IS SUBJECTED TO THE ELECTRIC FIELD OF THE CHARGED BODY (X). IF THE BODY (X) CARRIES A NEGATIVE CHARGE (I.E., CONTAINS AN EXCESS OF FREE ELECTRONS), THE FORCE FIELD OF THAT CHARGE WILL REPEL THE FREE ELEC-TRONS IN BODY (Y) FORCING THEM AWAY FROM THE CHARGE. BODY (Y) IS NOW POLAR-IZED WITH THE POSITIVELY CHARGED SURFACE LOCATED NEAREST (X), THE "CHARGING" BODY, AND THE NEGATIVELY CHARGED SURFACE LOCATED FARTHEST FROM BODY (X), THE NET CHARGE ON BODY (Y), EVEN THOUGH POLARIZED, IS STILL ZERO. IF BODY (Y) IS REMOVED FROM THE INFLUENCE OF THE STATIC FIELD CAUSED BY BODY (X) THE CHARGE ON BODY (Y) WILL REDISTRIBUTE ITSELF AND BODY (Y) WILL RETURN TO A STATE OF UNPOLARIZED NEUTRAL (ZERO) CHARGE. INSTEAD OF REMOVING BODY (Y) FROM THE INFLUENCE OF BODY (X)'S STATIC FIELD, IF THE SURFACE OF BODY (Y) (POLAR-IZED NEGATIVELY) IS TOUCHED TO GROUND, ELECTRONS WILL FLOW TO GROUND AND BODY (Y) WILL HAVE A NET POSITIVE CHARGE. AFTER REMOVING BODY (Y) FROM THE FIELD OF BODY (X), THIS POSITIVE CHARGE WILL BE DISTRIBUTED OVER BODY (Y). BODY (Y) WILL THEN HAVE BEEN CHARGED POSITIVELY BY INDUCTION. THIS PRINCIPLE IS ILLUSTRATED IN THE FOLLOWING DIAGRAM (FIGURE 3.3).

FIGURE 3.3: INDUCTION CHARGING

THE ELECTROSTATIC INDUCTION PHENOMENA CAN BE RESPONSIBLE FOR POLARIZING AN UNGROUNDED OBJECT OR CHARGING A GROUNDED OBJECT AS IS FREQUENTLY EXPERIENCED DURING THE PASSAGE OF A CHARGED CLOUD OVER AN OBJECT. PERSONNEL CAN ALSO INDUCE CHARGES ON NEARBY OBJECTS IN PROPORTION TO THE CHARGES THAT HAVE ACCUMULATED ON THEIR BODIES.

(4) CHARGING BY FREEZING

A NUMBER OF OBSERVERS HAVE FOUND LARGE POTENTIAL DIFFER-ENCES BETWEEN ICE AND WATER PHASES EXIST DURING THE FREEZING OF WATER. IT IS POSTULATED THAT AS A WATER DROP FREEZES, SMALL "SPLINTERS" ARE EJECTED FROM THE FREEZING DROP AND THE SPLINTERS ARE CHARGED OPPOSITELY TO THE RE-MAINING SOLID ICE PARTICLES. THIS MECHANISM CAUSES CLOUD ELECTRIFICATION DURING THUNDERSTORMS.

(5) ION AND ELECTRON BEAM CHARGING

IN A NUMBER OF INSTANCES IT HAS BEEN CONVENIENT TO CHARGE PARTICLES BY BOMBARDING THEM WITH IONS, ELECTRONS, OTHER ATOMIC PARTICLES

(E.G., ALPHA PARTICLES), OR X-RAYS. LET US ASSUME THAT THE PARTICLE IS CHARGED BY THE COLLECTION OF IONS OR ELECTRONS. CONSIDER A CHARGE PARTICLE BEAM IN WHICH THE PARTICLES CARRY A CHARGE "Q" AND HAVE A MASS "M" (FIGURE 3.4). LET THE BEAM CURRENT DENSITY BE J (AMPS/M<sup>2</sup>); THE PARTICLE RADIUS BE "r"; AND THE BEAM RADIUS BE "R". IF THE PARTICLE FALLS THROUGH THE DIAMETER OF THE BEAM WITH A VELOCITY V (M/SEC), IT WILL BE IN THE BEAM A TIME:

$t = \frac{2R}{V}$  (SEC) ..... (17)

DURING THAT TIME THERE WILL BE A CURRENT OF:

$I = \Pi r^2 J \text{ AMPERE}$ (18)

IMPINGING ON THE PARTICLE. THE TOTAL CHARGE TRANSFERRED TO THE PARTICLE SURFACE WILL BE EQUAL TO tI OR:

$Q = \frac{2\pi r^2 JR}{V} (COULOMB) .... (19)$   $= \bigcup_{V} UNCHARGED PARTICLE$   $= \bigcup_{V} UNCHARGED PARTICLE$   $= \bigcup_{V} UNCHARGED PARTICLE$

FIGURE 3.4: THE BEAM METHOD OF CHARGING PARTICLES

EXAMPLE (G): LET US USE SOME TYPICAL NUMBERS FOR THE VARIOUS PARAMETERS AND CALCULATE THE MAXIMUM CHARGE ON THE FALLING PARTICLE:  $r = 10^{-5}$  METER,  $R = 10^{-3}$  METER, J = 0.1 AMPERE/METER<sup>2</sup> AND V = 1.0 METER/SEC

THE CHARGE Q FOR THE PARTICLE AFTER IT TRAVERSES THE ION BEAM IS CALCULATED AS FOLLOWS:

| $Q = \frac{2\pi r^2 JR}{V}$ (COULOMB) (EQUATION 19)           |

|---------------------------------------------------------------|

| $= \frac{2\pi (10^{-5})^2 (1.1) (10^{-3})}{(1.0)} $ (COULOMB) |

| = $1.97 \times 10^{-13}$ (COULOMB)                            |

THE AMOUNT OF CHARGING OF THE PARTICLE FALLING THROUGH THE BEAM ALSO DEPENDS ON THE ENERGY OF THE ELECTRONS OR IONS. INITIALLY THE PARTICLE HAS NO CHARGE ON ITS SURFACE; HENCE THE INCOMING IONS (ELECTRONS) FIND NO RETARDING FIELDS TO KEEP THEM FROM THE SURFACE. AS THE PARTICLE BE-COMES MORE HIGHLY CHARGED WITH ELECTRONS, THE ELECTRONS AND IONS IN THE BEAM ARE ACTED ON BY THE FIELD PRODUCED BY THE CHARGED PARTICLE. IF THE BEAM ELECTRONS OR IONS HAVE AN ENERGY LEVEL THAT IS HIGH\_COMPARED WITH THAT OF THE FALLING PARTICLE, THEY WILL REACH THE SURFACE OF THE FALLING PARTICLE DURING THE ENTIRE TIME PERIOD THAT THE PARTICLE IS IN THE BEAM. ON THE OTHER HAND, IF THE POTENTIAL OF THE FALLING PARTICLE BECOMES COMPARABLE TO THE BEAM ENERGY WHILE IT IS STILL IN THE BEAM, THE IONS (ELECTRONS) IN THE BEAM WILL BE REPELLED AND CHARGING WILL CEASE OR THE RATE OF CHARGE WILL BE MAR-KEDLY REDUCED.

MANY AIR IONIZERS USE ALPHA PARTICLE EMISSION FOR CHARGING PARTICLES IN THE AIR. THE ALPHA PARTICLES COLLIDING WITH ATOMS IN THE AIR CREATE POSITIVELY CHARGED AIR MOLECULES AND FREE ELECTRONS WHICH ALSO COM-BINE WITH AIR MOLECULES FORMING BOTH POSITIVELY CHARGED AND NEGATIVELY CHARGED IONS.

38.

## (6) SPRAY CHARGING

THE PHENOMENON OF THE FORMATION OF CHARGED DROPS IN A CLOUD OR FOG PRODUCED BY AN ATOMIZED SPRAY OF A LIQUID IS COMMONLY DES-CRIBED AS THE BALLOELECTRIC EFFECT. THIS EFFECT IS EXPLAINED AS THE ELECTRIFICATION OF DROPS DURING MECHANICAL ATOMIZATION OF THE LIQUID OCCURS BECAUSE THE DROPS CARRY EXCESS CHARGE OF ONE OR THE OTHER POLAIRY AND THAT THESE CHARGES FORM IN THE VOLUME OF THE DROP AS A RESULT OF FLUCTUATIONS IN THE ION DISTRIBUTION IN THE LIQUID. SOME OTHER RESEARCH WORKERS EXPLAIN THE PHENOMENA ON THE BASIS OF A DOUBLE LAYER OF CHARGE AT THE SURFACE OF THE LIQUID.

IN THE DOUBLE LAYER THEORY, A LAYER OF ORIENTED DIPOLES IS FOUND AT THE LIQUID-GAS INTERFACE. DEPENDING ON THE LIQUID, THE DIPOLES MAY BE ORIENTED WITH NEGATIVE POLES OUTWARD AND POSITIVE POLES INWARD. IN THIS CASE, THE INWARD ENDS OF THE DIPOLES ATTRACT AND IN SOME CASES BIND VERY TIGHTLY SOME OF THE NEGATIVE IONS PRESENT IN THE LIQUID. THE IONS OF POSI-TIVE SIGN IN THE LIQUID ARE LESS STRONGLY HELD TO THEIR POSITIVE COUNTERPARTS, AND THEY THEREFORE MOVE RANDOMLY IN THE LIQUID WITH MORE EASE.

THUS, THE DOUBLE LAYER AND ITS ATTACHED NEGATIVE IONS CONSTITUTE A CHARGED LAYER WHICH, WHEN SPRAYED OR OTHERWISE DISRUPTED TO FORM SMALLER DROPLETS, WILL LEAD TO NET NEGATIVE CHARGES ON THE DROPLETS. THE POSITIVE CHARGES TEND TO REMAIN ON THE SPRAY CONTAINER. THE PRESENCE OR ADDITION OF IMPURITIES OR SALTS OF VARIOUS KINDS AND IN VARIOUS AMOUNTS CAN ALTER QUITE DRASTICALLY THE SPRAY CHARGING PROCESS.

IT IS TO BE NOTED THAT THE TIME CONSTANTS FOR CHARGE AND MASS TRANSFER OF VARIOUS LIQUIDS PLAY A VERY IMPORTANT ROLE. IN ANY OF THESE PHENOMENA. THESE TIME CONSTANTS ARE DEPENDENT UPON THE CONDUCTIVITY OF THE LIQUID AND THE MASS TRANSFER OF THE DROPLETS. IF THE NEGATIVE CHARGES

ARE MECHANICALLY REMOVED FASTER THAN THE NEGATIVE CHARGES CAN BE TRANS-FERRED BACK THROUGH THE LIQUID, THE CHARGE PER UNIT MASS OF THE DROPLET WILL BEGIN TO FALL. A HIGHLY INSULATING LIQUID MAY REACH THE POINT WHERE A NET CHARGE IS NOT POSSIBLE, AND CAN GO FROM AN ASYMMETRICAL CHARGING SITUATION TO A SYMMETRICAL SITUATION WHERE EACH DROPLET MAY BE SLIGHTLY CHARGED, ALTHOUGH THE NET CHARGE (AVERAGED OVER ALL DROPLETS SPRAYED) WILL BE ZERO. IT SHOULD BE POINTED OUT THAT ANY LOCAL FIELDS AT THE LIQUID SUR-FACE WILL AFFECT THE RESULTS DRASTICALLY AND WILL LEAD TO INCORRECT INTER-PRETATION OF ANY DATA OBTAINED UNLESS THEIR PRESENCE IS TAKEN INTO ACCOUNT.

(7) OTHER METHODS OF CHARGING

OTHER LESS KNOWN METHODS OF ELECTROSTATIC CHARGING ALSO PERTINENT TO ESD AND ESD CONTROL ARE AS FOLLOWS:

#### (a) CHARGING BY THERMIONIC EMISSION

IN SOME INSTANCES, PARTICLES ARE RAISED TO TEMPERA-TURES HIGH ENOUGH TO PERMIT THERMIONIC EMISSION OF ELECTRONS TO TAKE PLACE AS OCCURS IN THE FILAMENT OF AN ELECTRON TUBE. IF SOME OF THESE ELECTRONS ARE REMOVED BY AN EXTERNAL FIELD OR BY A NEAR ENCOUNTER WITH ANOTHER SURFACE, THE PARTICLE COULD END UP WITH A POSITIVE CHARGE.

## (b) PHOTOELECTRIC CHARGING

IF LIGHT FALLS ON THE SURFACE OF A PARTICLE, THE LIGHT QUANTA CAN IMPART SUFFICIENT ENERGY TO ELECTRONS ON THE SURFACE TO EJECT THEM FROM THE PARTICLE LEAVING THE PARTICLE POSITIVELY CHARGED. THIS PHENOMENA IS KNOWN AS PHOTOELECTRIC CHARGING.

### (c) FIELD EMISSION CHARGING

IF AN UNCHARGED PARTICLE (LIQUID OR SOLID) ENTERS A REGION IN WHICH THERE IS AN ELECTRIC FIELD, THE PARTICLE WILL BE POLARIZED.

THAT IS, THERE WILL BE A TRANSFER OF CHARGE WITHIN THE PARTICLE SO THAT ONE END OF THE PARTICLE BECOMES NEGATIVELY AND THE OTHER END POSITIVELY CHARGED. IF THE FIELD INTENSITY, E, IS HIGH ENOUGH, ELECTRONS MAY BE EXTRACTED BY THE HIGH FIELD FROM THE NEGATIVE END (ELECTRON FIELD EMISSION) AND/OR POSITIVE IONS MAY BE EXTRACTED FROM THE POSITIVE END (POSITIVE ION) FIELD EMISSION. IF ELECTRONS LEAVE THE PARTICLE, THE PARTICLE BECOMES POSITIVELY CHARGED AND EXPERIENCES A FORCE IN THE DIRECTION OF THE ELECTRIC FIELD.

## (d) CORONA CHARGING

IF A PARTICLE IS CAUSED TO TRAVEL THROUGH A REGION OF IONIZED GAS IN WHICH THE CHARGE IS PREDOMINANTLY OF ONE POLARITY OR THE OTHER, THE PARTICLE ACQUIRES A NET NON-ZERO CHARGE. IN REALITY, THE SITUA-TION IS MORE COMPLEX BECAUSE IN ANY IONIZED GAS THERE ARE IONS OF BOTH POLARITIES (OR POSITIVE IONS AND ELECTRONS OR NEGATIVE IONS) PRESENT, EVEN THOUGH IONS OF ONE POLARITY MAY PREDOMINATE. IN THE LATTER CASE, THE PAR-TICLE WILL CHARGE TO THE POLARITY OF THE MOST PREDOMINANT IONS. THE PARTICLE WILL BE CHARGED TO A VALUE DEPENDING ON THE TEMPERATURE OF THE IONS AND ELECTRONS IN THE GAS AND ON THEIR MASSES. THE IONIZED GAS COULD BE FORMED DUE TO CORONA DISCHARGE OF A SHARP POINTED OBJECT, CHARGED TO A HIGH VOLTAGE.

#### (e) SURFACE CHARGING BY DEFORMATION AND CLEAVAGE

DEFORMATION OF A SOLID BODY CAN GIVE RISE TO SURFACE CHARGES. THIS OCCURS BY THE REORIENTATION OF POLAR MOLECULES OR DISPLACEMENT OF IONS UNDER THE ACTION OF AN EXTERNAL PRESSURE, AND THE GENERATION AND MIGRATION OF DISLOCATIONS. THE FIRST MECHANISM REQUIRES A PARTICULAR CRYSTAL SYMMETRY.

## B. PARAMETERS INFLUENCING THE MAGNITUDE OF STATIC CHARGE GENERATION

(1) CONDUCTIVITY

THE ABILITY OF A MATERIAL TO SURRENDER ITS ELECTRONS OR ABSORB EXCESS ELECTRONS IS A FUNCTION OF THE CONDUCITIVITY OF THE MATERIAL. FOR EXAMPLE, IN A GOOD CONDUCTOR, SUCH AS COPPER, ELECTRONS MOVE ABOUT FREELY, AND RAPIDLY. IF GROUNDED A CONDUCTIVE MATERIAL WOULD GIVE THE CHARGE UP TO GROUND AND BECOME NEUTRAL.

FOR HIGHLY NON-CONDUCTIVE (INSULATIVE) MATERIALS, SUCH AS PLASTICS, IT IS EXTREMELY EASY TO DISRUPT THE MOLECULAR STRUCTURE AND CAUSE THE MATERIAL TO CHARGE WITH THE SLIGHTEST FRICTION, HEAT OR PRESSURE. HOW-EVER, IF THE CONDUCTIVITY OF THE INSULATIVE MATERIAL CAN BE INCREASED, THEN, PREVENTING STATIC ELECTRICITY BECOMES RELATIVELY EASY SINCE THE CHARGE WILL BE DISPERSED OVER THE SURFACE OF THE MATERIAL, AND IF GROUNDED WILL FLOW TO GROUND.

FOR EXAMPLE, ADDING CONDUCTIVITY TO PLASTICS (E.G., ANTI-STATS WHICH CREATE A CONDUCTIVE LAYER, OR IMPREGNATING THE PLASTIC WITH A CONDUCTIVE SUBSTANCE) WILL MOVE THESE MATERIALS HIGHER INTO THE CONDUCTIVITY RANGE AND REDUCE THE BUILDUP OF STATIC ELECTRICITY DUE TO ANY CHARGING MECH-ANISM. SOME ANTISTATS, IMPREGNATED WITHIN THE PLASTICS, BLEED TO THE SURFACE AND REACT WITH THE HUMIDITY IN THE AIR TO FORM A CONDUCTIVE SWEAT LAYER. TOPICAL ANTISTATIC SPRAYS USED TO PROVIDE A SLIGHTLY CONDUCTIVE COATING ARE TYPICALLY MADE UP FROM A DETERGENT BASED MATERIAL THAT HAS BEEN DILUTED IN A SOLVENT, SUCH AS A MILD ALCOHOL. A FIRE RETARDANT IS ADDED TO COMBAT THE FLAMMABILITY OF THE SOLVENT, FREONS ARE ADDED TO PROVIDE SPRAY PRESSURE, ENDING UP WITH THE FINAL PRODUCT COMMONLY KNOWN AS AN AEROSOL ANTI-STATIC SPRAY. AS THIS SPRAY LEAVES THE NOZZLE OF THE AEROSOL CAN, THE FREONS

NORMALLY EVAPORATE IMMEDIATELY. A SHORT TIME AFTER CONTACT WITH THE MATER-IAL TO BE COATED, THE FIRE RETARDANT AND SOLVENTS EVAPORATE, LEAVING A DETERGENT OR SLIGHTLY CONDUCTIVE COATING ON THE SURFACE OF THE MATERIAL. THE PLASTIC HAS NOW BECOME MORE CONDUCTIVE AND AS LONG AS THIS COATING IS NOT DISTURBED, IT WILL HELP RETARD THE GENERATION OF STATIC ELECTRICITY ON THIS MATERIAL.

#### (2) <u>HUMIDITY</u>

HUMID AIR HELPS TO DISSIPATE GENERATED ELECTROSTATIC CHARGES BY KEEPING SURFACES MOIST WITH A CONDUCTIVE SWEAT LAYER OF WATER AND DUST PARTICLES. ELECTROSTATIC VOLTAGE LEVELS GENERATED CAN INCREASE SUBSTANTIALLY WITH A DECREASE IN RELATIVE HUMIDITY WHERE THE SWEAT LAYER IS DEPLETED AS SHOWN IN TABLE III-A. HOWEVER, IT IS ALSO EVIDENT FROM TABLE III-A THAT RELATIVELY HIGH ELECTROSTATIC VOLTAGES CAN STILL BE GENER-ATED WITH RELATIVE HUMIDITY AS HIGH AS 90%. RELATIVE HUMIDITY LEVELS IN ESD PROTECTIVE AREAS SHOULD BE MAINTAINED IN THE RANGE OF 40 TO 60% OR HIGHER AS LONG AS IT DOES NOT RESULT IN ACCELERATING RUST FORMATION OR RESULT IN OTHER DETRIMENTAL EFFECTS. WHERE HIGH RELATIVE HUMIDITY LEVELS CANNOT BE MAINTAINED THE USE OF IONIZED AIR CAN BE USED TO AID IN DISSIPATING ELECTRO-STATIC CHARGES ON INSULATORS.

## C. MATHEMATICAL EXPRESSIONS FOR ELECTROSTATIC DISCHARGE (ESD)

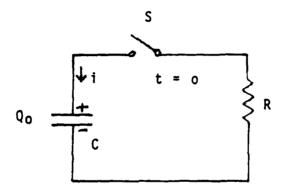

WHAT TYPICALLY HAPPENS DURING AN ELECTROSTATIC DISCHARGE CAN BE SIMULATED BY A CAPACITOR CHARGED TO SOME POTENTIAL AND THEN DISCHARGED THROUGH A RESISTOR. CONSIDER THE CIRCUIT IN FIGURE 3.5. IT IS ASSUMED THAT CAPACITOR C HAS BEEN CHARGED TO A VOLTAGE V =  $Q_0/C$  PRIOR TO t = 0. THE CHARGE  $Q_0$  MIGHT HAVE BEEN PRESENT AT THE PLATES OF THE CAPACITOR FOR SOME PERIOD OF TIME PRIOR TO THE CLOSING OF SWITCH(S) SINCE A PERFECT DIELECTRIC

| MEANS OF                                 | RELATIVE HUMIDITY |               |  |

|------------------------------------------|-------------------|---------------|--|

| STATIC GENERATION                        | LOW - 10-20%      | HIGH - 65-90% |  |

| WALKING ACROSS CARPET                    | 35,000            | 1,500         |  |

| WALKING OVER VINYL<br>FLOOR              | 12,000            | 250           |  |

| WORKER AT BENCH                          | 6,000             | 100           |  |

| VINYL ENVELOPES FOR<br>WORK INSTRUCTIONS | 7,000             | 600           |  |

| COMMON POLY BAG PICKED<br>UP FROM BENCH  | 20,000            | 1,200         |  |

| WORK CHAIR PADDED WITH<br>URETHANE FOAM  | 18,000            | 1,500         |  |

TABLE III-A TYPICAL MEASURED ELECTROSTATIC VOLTAGES (REFERENCE 8)

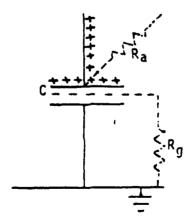

MATERIAL IS ASSUMED. ACTUALLY THE DIELECTRIC LEAKAGE, Rg AND THE CHARGE BLEEDING OFF INTO THE AIR, Ra (FIGURE 3.6) WILL CAUSE THE CHARGE TO GRADU-ALLY DIMINISH TO ZERO. WITH VALUES OF Ra/Rg ON THE ORDER OF  $10^{13}$  OHMS, THE TIME CONSTANT WOULD BE RC =  $10^{13} \times 10^{-10} = 10^3$  SECONDS OR 17 MINUTES WITH THE DISCHARGE CURRENT BEING QUITE LOW. THIS TIME IS REFERRED TO AS RELAXA-TION TIME IN ELECTROSTATICS. THIS IS A PARAMETER OF PRIME IMPORTANCE WHEN CONSIDERING THE ESD HAZARD TO SEMICONDUCTORS. RELAXATION TIME IS A MEASURE OF THE TIME REQUIRED FOR A CHARGE TO DISSIPATE BY LEAKAGE. IT IS EQUAL TO:

$\tau = \varepsilon_r \varepsilon_0 / \gamma \qquad (20)$

$\tau = RC \qquad (21)$

WHERE:

$\varepsilon_{0}$  is the Absolute dielectric constant for free space (8.85  $\times$  10<sup>-14</sup> sec/ohm cm).

- $\varepsilon_{\mu}$  = RELATIVE DIELECTRIC CONSTANT, DIMENSIONLESS

- $\gamma = SPECIFIC CONDUCTIVITY (OHM CM)^{-1}$

- R = EFFECTIVE RESISTANCE TO GROUND CONSIDERING ALL PARALLEL

PATHS (OHMS)

- C = CAPACITANCE OF THE CHARGED OBJECT (FARADS)

FIGURE 3.6: CHARGE STORED AND LEAKAGE PATHS

THE CAPACITOR DISCHARGE PHENOMENA (FIGURE 3.5), AT AND AFTER t = 0 IS DESCRIBED BY THE FOLLOWING DIFFERENTIAL EQUATION:

SUBJECT TO THE CONDITION THAT  $q = Q_0 AT t = 0$ , THE CHARGE, q, IN EQUATION (22), IS:

$$q = Q_0 + \int_0^t di dt \qquad (23)$$

WHERE:

$+ \int_{0}^{L} i dt$  is the charge transferred to (charging) or from (DISCHARGING) THE CAPACITOR PLATES AS A RESULT OF CURRENT FLOW. EQUATION (22) CAN BE WRITTEN IN TERMS OF q AS:

$R \frac{dq}{dt} + \frac{q}{c} = 0 \quad .... \quad (24)$

A SOLUTION OF THE ABOVE EQUATION FOR q AS A FUNCTION OF TIME IS:

SINCE:

R (Aae

$$\alpha t$$

) +  $\frac{A}{C} \alpha t$  = Ae  $\alpha t$  (Ra +  $\frac{1}{c}$ ) = 0

PROVIDED THAT:

$$(R\alpha + \frac{1}{C}) = 0$$

or  $\alpha = -\frac{1}{RC}$

USING INITIAL CONDITION (q =  $Q_0$  AT t = 0) ON EQUATION (25):

$A = Q_0$ , THEREFORE:

$$q = Q_0 e^{-t/RC}$$

(26)

= VC e^{-t/RC}

AND THE CIRCUIT CURRENT:

= I<sub>o</sub> e<sup>-t/ $\tau$ </sup>

$$i = \frac{dq}{dt} = -\frac{Q_0}{RC} e^{-t/RC} \qquad (27)$$

EQUATION (26) SHOWS THAT THE CHARGE AT THE PLATES OF THE CAPACITOR SUBSIDES FROM ITS INITIAL VALUE OF  $Q_0$  AT A TIME RATE WHICH IS GOVERNED BY THE RC PRODUCT. EQUATION (27) SHOWS THAT THE CURRENT AT t = 0, IS:

THE LENGTH OF TIME REQUIRED FOR q (OR i) TO LOSE 63.2% OF ITS TOTAL CHARGE IS  $\tau$  = RC, SINCE IT IS THIS VALUE OF TIME WHICH, WHEN ENTERED INTO EQUATION (27), REDUCES THE CHARGE q TO .368 Q<sub>0</sub>. IN 5 $\tau$  THE CHARGE WILL BE REDUCED TO APPROXIMATELY 99% OF Q<sub>0</sub>. THE CHARGE q CHANGES FROM Q<sub>0</sub>, AT t = 0, TO ZERO VALUE ONLY AT t =  $\infty$ . THE PRODUCT RC =  $\tau$  IS CALLED THE TIME CONSTANT OF THE CIRCUIT.

EXAMPLE (H): CONSIDER A CHARGED HUMAN WITH THE FOLLOWING VALUES FOR THE DISCHARGE PARAMETERS:

C = 100 PF, R = 1,500 OHM, AND V = 10,000 VOLTS

THE PEAK CURRENT

$$I_0 = \frac{V_0}{R} = \frac{10,000}{1,500} = 6.66$$

AMPERES

THE INSTANTANEOUS POWER DISSIPATED IN THE RESISTOR IS:

$$P_{i} = i_{i}^{2} R = R I_{o}^{2} e^{-2t/\tau}$$

WHERE:

= RC = 150 NSEC

THE AVERAGE POWER OVER FIVE TIME CONSTANTS IS:

$$P_{AV} = \frac{1}{5\tau} \int_{0}^{5\tau} R I_{0}^{2} e^{-2t/\tau} dt$$

$$P_{AV} = \frac{R I_{0}^{2}}{10} (1 - e^{-10})$$

$$=\frac{R I_0^2}{10}$$

= 6653 WATTS

THE AVERAGE POWER DISSIPATED IN THE RESISTOR OVER 5 RC (=750 N SEC) TIME PERIOD IS THEN CALCULATED TO BE 6653 WATTS. THE ENERGY IS 6653 X 750 X  $10^{-9} = 5 \times 10^{-3}$  JOULES. IN THIS EXAMPLE MOST OF THE ENERGY IN THE CAPACITOR IS DISSIPATED IN THE RESISTOR IN A VERY SHORT PERIOD OF TIME (750 N SEC). CONSEQUENTLY, THE POWER IS QUITE HIGH. IN REALITY, PART RESISTANCE ADDS CONSIDERABLE RESISTANCE WHEN DISCHARGING THROUGH A PART WHICH REDUCES THE POWER LEVEL, LENGTHENS THE DISCHARGE PULSE AND RESULTS IN MOST OF THE STORED ENERGY BEING DISSIPATED IN THE PART ITSELF.

48.

EXAMPLE (I): EXPERIENCE HAS SHOWN THAT PERSONNEL IN A MANUFACTURING EN-VIRONMENT COMMONLY ATTAIN POTENTIALS OF 10,000 VOLTS OR MORE JUST WALKING ACROSS THE FLOOR, ESPECIALLY UNDER CONDITIONS OF LOW HUMIDITY. FOR AN ANTI-STATIC TABLE MAT, AN ANTI-STATIC FLOOR MAT OR A WRIST STRAP TO BE EFFECTIVE IT SHOULD HAVE A RESISTANCE TO GROUND TO ALLOW DISCHARGE FROM 10,000 VOLTS DOWN TO A SAFE LIMIT (FOR EXAMPLE 100 VOLT) IN APPROXIMATELY ONE MILLISECOND. THE MAXIMUM RESISTANCE TO GROUND FOR THE EFFECTIVE DISSIPATION OF SUCH POTENTIALS IS CALCULATED AS FOLLOWS:

$$V = V_0 e^- \frac{t}{RC}$$

WHERE:

V = 100 VOLTS (ASSUMED SAFE LEVEL)

V<sub>0</sub> = 10,000 VOLTS (INITIAL VOLTAGE OF OBJECT OR PERSON)

t = 1 MILLISECOND (ALLOWABLE TIME FOR DISCHARGE TO V)

C = 100 PF

R = MAXIMUM ALLOWABLE RESISTANCE TO GROUND IN OHMS

$$100 = 10,000 \text{ EXP} \left(-\frac{10^{-3}}{100 \text{ X } 10^{-12} \text{ R}}\right)$$

$$R = \frac{1}{\ell n} \frac{1}{100 \text{ X10}^{-7}}$$

= 2.17 X 10<sup>6</sup> = 2.17 MEGOHMS

NOTE: THIS IS AN ILLUSTRATIVE MATHEMATICAL CALCULATION TO FIND THE MAXIMUM RESISTANCE TO GROUND FOR THE EFFECTIVE DISSIPATION OF STATIC VOLTAGE TO A SAFE LEVEL. THE SAFE LEVEL VOLTAGE AND THE TIME TO REACH THE VALUE SHOULD NOT BE CONSIDERED AS ACCEPTED VALUES.

EXAMPLE (I) (CONTINUED): THUS, A RESISTANCE OF 2 × 10<sup>6</sup> OHMS TO GROUND THROUGH EITHER A TABLE MAT OR FLOOR MAT OR WRIST STRAP OR ANY OF THE COMBINATIONS, ASSURES THAT DISCHARGE TO A SAFE LIMIT (100 VOLTS) WILL OCCUR WITHIN ONE MILLISECOND. THIS, FOR ALL PRACTICAL PURPOSES, MINIMIZES THE CHANCE THAT A STATIC SENSITIVE ELECTRONIC COMPONENT CAN BE EXPOSED TO A STATIC CAUSED ELECTRICAL OVERSTRESS.

### IV. PRIME STATIC GENERATORS

#### A. TYPICAL CHARGE GENERATORS

TYPICAL PRIME CHARGE SOURCES COMMONLY ENCOUNTERED IN A MANU-FACTURING FACILITY ARE SHOWN IN TABLE IV-A. THESE SOURCES INCLUDE THE WORLD AROUND US. THEY CONSIST OF OUR BUILDING FLOOR AND WALLS, CHAIRS, WORK SURFACES, CLOTHING, PACKAGING, TOOLS, TEST AND PROCESSING EQUIPMENT. THESE PRIME SOURCES ARE COMMONLY NON-CONDUCTORS AND TYPICALLY SYNTHETIC NON-CONDUCTIVE TYPE MATERIALS. ELECTROSTATIC VOLTAGE LEVELS GENERATED BY NON-CONDUCTORS CAN BE EXTREMELY HIGH AND ARE SUSTAINED FOR LONG PERIODS OF TIME SINCE CHARGES ARE IMMOBILE, ARE NOT DISSIPATED OVER THE SURFACE OF THE SUBSTANCE, OR READILY CONDUCTED TO ANOTHER CONTACTING SUBSTANCE. HOWEVER, IONS IN THE AIR AND LOW LEAKAGE CURRENT BASED UPON THE RESISTIVITY OF THE MATERIAL WILL SLOWLY DISSIPATE THE CHARGE TO A NEARBY MASS OR GROUND. THE MORE MOISTURE IN THE AIR THE FASTER A CHARGE WILL DISSIPATE. THIS IS DUE TO THE MOISTURIZING OF SURROUNDING MATERIALS WHICH USUALLY MAKES THEM MORE CONDUCTIVE (SEE SECTION III). THE GENERATION OF 15,000 VOLTS FROM PRIME SOURCES IN A TYPICAL MANUFACTURING FACILITY WITHOUT ESD PROTECTIVE CONTROLS IS NOT UNUSUAL.

#### B. MANUFACTURING PROCESSES GENERATING STATIC ELECTRICITY

MANY OF THE PROCESSES INVOLVED IN THE MANUFACTURE OF ELECTRONIC EQUIPMENT CAN GENERATE VARYING LEVELS OF STATIC VOLTAGES. SOME EXAMPLES OF THESE PROCESSES ARE AS FOLLOWS:

(1) CRYOGENIC COOLANTS

CRYOGENIC COOLANTS ARE COMMONLY USED FOR TROUBLE-SHOOTING AND ENVIRONMENTAL TESTING. FACTORY TEST TECHNICIANS, IN ORDER TO ISOLATE A

#### TABLE IV-A

### TYPICAL PRIME CHARGE SOURCES

- WORK SURFACES

- •• WAXED, PAINTED OR VARNISHED SURFACES

- COMMON VINYL OR PLASTICS

- FLOORS

- SEALED CONCRETE

- WAXED, FINISHED WOOD

- COMMON VINYL TILE OR SHEETING

- CLOTHES

- COMMON CLEAN ROOM SMOCKS

- COMMON SYNTHETIC PERSONNEL GARMENTS

- NON-CONDUCTIVE SHOES

- •• VIRGIN COTTON\*

- CHAIRS

- **ee** FINISHED WOOD

- •• VINYL

- FIBERGLASS

- PACKAGING AND HANDLING

- COMMON PLASTIC BAGS, WRAPS, ENVELOPES

- COMMON BUBBLE PACK, FOAM

- COMMON PLASTIC TRAYS, PLASTIC TOTE BOXES, VIALS, PARTS BINS

- ASSEMBLY, CLEANING, TEST AND REPAIR AREAS

- SPRAY CLEANERS

- COMMON PLASTIC SOLDER SUCKERS

- SOLDER IRONS WITH UNGROUNDED TIPS

- •• SOLVENT BRUSHES (SYNTHETIC BRISTLES)

- •• CLEANING OR DRYING BY FLUID OR EVAPORATION

- TEMPERATURE CHAMBERS

- CRYOGENIC SPRAYS

- **•• HEAT GUNS AND BLOWERS**

- SAND BLASTING

- •• ELECTROSTATIC COPIERS

**\*VIRGIN COTTON CAN BE A STATIC SOURCE AT LOW RELATIVE HUMIDITIES SUCH AS BELOW 30%.**

DEFECTIVE INTEGRATED CIRCUIT, OFTEN USE A CANNED CRYOGENIC SUCH AS KOOL-ZIT, QUICK FREEZE,<sup>®</sup> OR OTHER BRAND NAMES TO COOL A SMALL ZONE ON AN ASSEMBLY BOARD. LIQUID NITROGEN (LN<sub>2</sub>) IS ALSO USED FOR THIS PURPOSE. STATIC CHARGE GENERA-TION IS USUALLY DEVELOPED DURING THIS PROCESS BY THE FOLLOWING METHODS:

(a) GAS EXPANSION INTO THE ATMOSPHERE OF DIFFERENT GASSES PRO-DUCES FRICTION BETWEEN THE MOLECULES OF THE GASSES. THIS PHENOMENON OCCURS AT THE EXPANSION POINT OF AN AEROSOL SPRAY CAN NOZZLE.

(b) AS THE CRYOGENIC LIQUID CONTACTS THE SURFACE OF THE ASSEMBLY BOARD, THE LOWERED TEMPERATURE CAUSES THE HUMIDITY (WATER) IN THE AIR TO CONDENSATE ON THE SURFACE. AT THE INTERFACE BETWEEN THE ASSEMBLY'S SURFACE AND THE WATER CONDENSATE A STATIC POTENTIAL DIFFERENCE IS PRODUCED.

(2) ULTRA-VIOLET (UV) LIGHT

ULTRA-VIOLET LIGHT OFTEN USED FOR VISUAL INSPECTION CAUSES NEGATIVELY CHARGED MATERIALS TO LOSE THEIR CHARGE. ALSO, IF THE MATERIAL IS UNCHARGED, THAT MATERIAL WILL ACQUIRE A POSITIVE CHARGE AS A RESULT OF THE ILLUMINATION.

THE CHARGE GENERATION REQUIRES APPROXIMATELY THIRTY MINUTES TO AN HOUR TO DEVELOP A CHARGE HIGH ENOUGH TO CAUSE A PROBLEM, DEPENDENT UPON THE TYPE OF MATERIAL THAT IS BEING ILLUMINATED. NORMAL UV LIGHT INSPECTION TIME SHOULD NOT CAUSE ANY PROBLEM. PROLONGED EXPOSURE COULD RESULT IN VOLT-AGE LEVELS THAT COULD DAMAGE PARTS HIGHLY SENSITIVE TO ESD. THEREFORE, ASSEMBLIES WITH ESDS PARTS SHOULD NOT BE PLACED NEAR A UV LIGHT SOURCE FOR LONG PERIODS OF TIME.

# (3) FLUID FLOW

MACHINES INCORPORATING FLUID FLOW OR EVAPORATION SUCH AS FLOW SOLDER MACHINES AND VAPOR DE-GREASERS ARE SOURCES OF STATIC CHARGE. THE

VAPOR DE-GREASING PROCESS REQUIRES THAT THE ASSEMBLIES OR PARTS BE CLEANED IN A LIQUID REGION AND THEN BE HELD IN THE VAPOR REGION FOR A PERIOD OF TIME.

THE LIQUID PORTION OF THE FREON (TF, TE, ETC.) IS CONDUCTIVE AND WILL NOT GENERATE A CHARGE. HOWEVER, THE VAPOR REGION IS NON-CONDUCTIVE. AS THE VAPOR CONDENSES ON THE SURFACE OF THE ASSEMBLY OR COMPONENTS, A CHARGE OF UP TO 400 VOLTS CAN BE GENERATED. AS THE CONDENSATE FALLS FROM THE ASSEMBLY, THE CHARGE IS CARRIED AWAY AND NO RESIDUAL CHARGE REMAINS. HOWEVER, BY THIS TIME THE STATIC CHARGE COULD HAVE CAUSED A FAILURE OF A SENSITIVE PART ON THAT ASSEMBLY.

(4) CONFORMAL COATING

CONFORMAL COATING OF PRINTED WIRING BOARD ASSEMBLIES IN-VOLVES VARIOUS FORMS OF THE FOLLOWING STEPS:

- TAPING

- SPRAY OR DIP COATING OF POLYURETHANE OR OTHER COATING MATERIAL

- CURING IN AMBIENT ROOM TEMPERATURE

- CURING IN LAMINAR AIR FLOW OVENS WHILE MOUNTED IN METAL

FRAME CARD-EDGE HOLDERS OR ON POLYPROPYLENE HOLDING

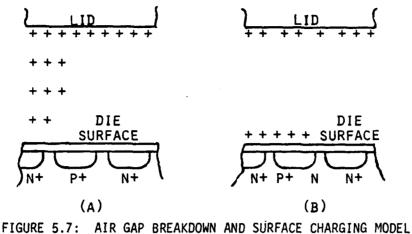

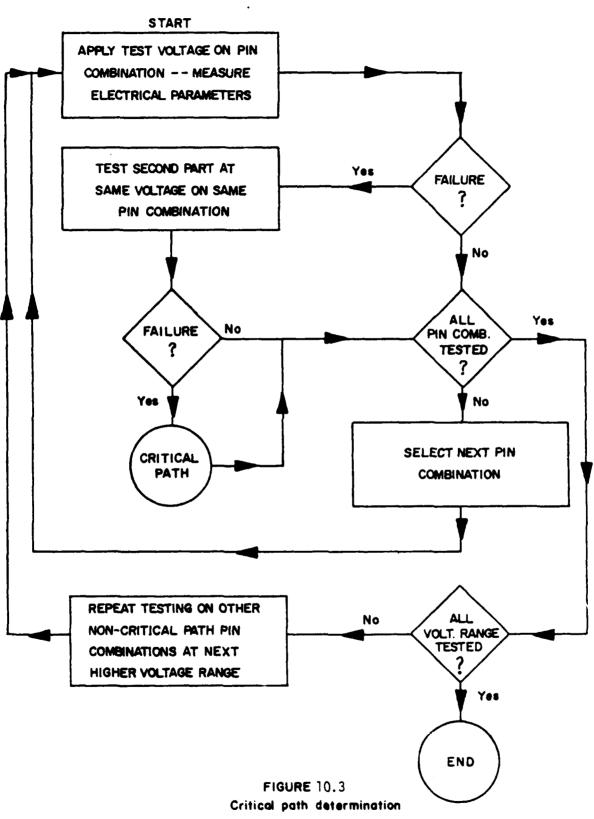

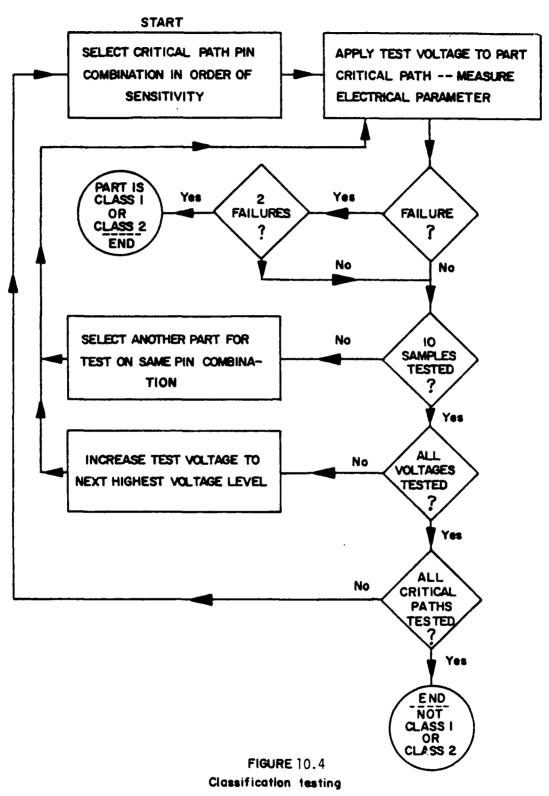

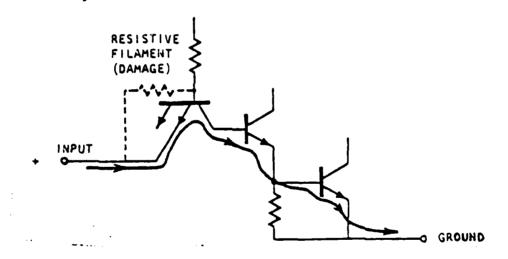

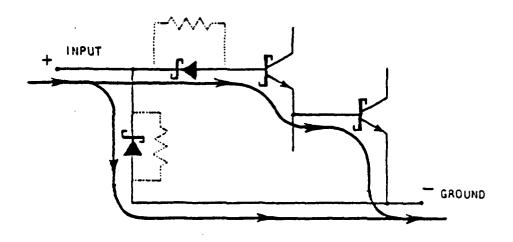

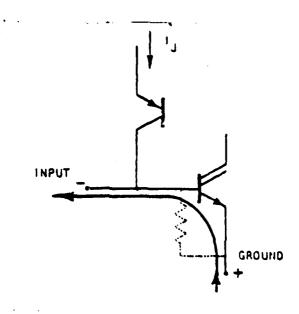

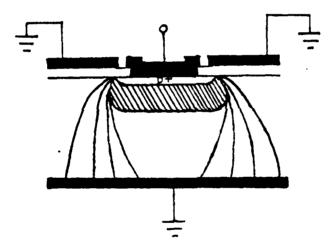

TRAYS