# **Avalon Interface Specifications**

101 Innovation Drive San Jose, CA 95134 www.altera.com

Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Contents**

| Chapter 1. Introduction                                      |      |

|--------------------------------------------------------------|------|

| 1.1. Avalon Properties and Parameters                        |      |

| 1.2. Signal Types                                            | 1-4  |

| 1.3. Interface Timing                                        |      |

| 1.4. Related Documents                                       | 1-4  |

|                                                              |      |

| Chapter 2. Clock Interfaces                                  |      |

| 2.1. Clock Input (Sink)                                      |      |

| 2.1.1. Properties                                            |      |

| 2.1.2. Signal Types                                          |      |

| 2.1.3. associatedClock Interfaces                            |      |

| 2.2. Clock Output (Source)                                   |      |

| 2.2.1. Properties                                            |      |

| 2.2.2. Signal Types                                          | 2-2  |

| Observer O. Augley Manney Manney Listerfaces                 |      |

| Chapter 3. Avalon Memory-Mapped Interfaces                   | 2.1  |

| 3.1. Introduction                                            |      |

| 3.2. Slaves                                                  |      |

| 3.3. Slave Interface Properties                              |      |

| 3.4. Slave Timing                                            |      |

| 3.4.1. Synchronous Interface                                 |      |

| 3.4.2. Performance                                           |      |

| 3.4.3. Electrical Characteristics                            |      |

| 3.5. Slave Transfers                                         |      |

| 3.5.1. Typical Slave Read and Write Transfers                |      |

| 3.5.2. Slave Read and Write Transfers with Fixed Wait-States |      |

| 3.5.3. Pipelined Transfers                                   |      |

| 3.5.3.1. Slave Pipelined Read Transfer with Variable Latency |      |

| 3.5.3.2. Slave Pipelined Read Transfer with Fixed Latency    |      |

| 3.5.4. Burst Transfer                                        |      |

| 3.5.4.1. Slave Write Bursts                                  |      |

| 3.5.4.2. Slave Read Bursts                                   |      |

| 3.5.4.3. Line–Wrapped Bursts                                 |      |

| 3.5.4.4. Flow Control                                        |      |

| 3.6. Address Alignment                                       |      |

| 3.6.1. Avalon-MM Slave Addressing                            |      |

| 3.6.2. Avalon-MM Tri-State Slave Addressing                  |      |

| 3.6.3. Native Addressing                                     | 3-17 |

| 3.7. Masters                                                 |      |

| 3.8. Master Signal Types                                     | 3-18 |

| 3.9. Master Interface Properties                             |      |

| 3.10. Master Transfers                                       | 3-21 |

| 3.10.1. Master Pipelined Read Transfer                       |      |

| 3.10.2. Burst Transfers                                      |      |

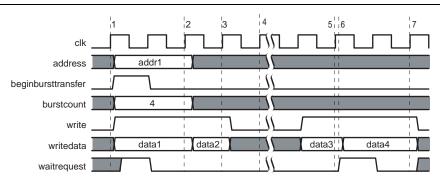

| 3.10.2.1. Master Write Bursts                                | 3-24 |

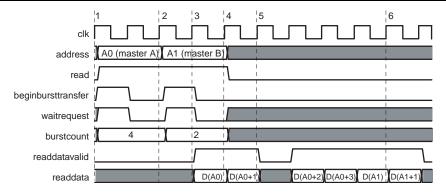

| 3.10.2.2. Master Read Bursts                                 |      |

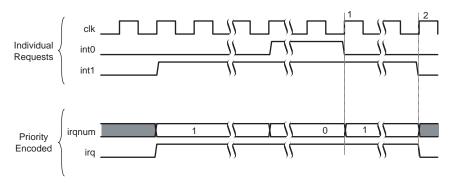

| Chapter 4. | Interrupt Interfaces                                              |

|------------|-------------------------------------------------------------------|

| 4.1. Inte  | errupt Sender 4-                                                  |

| 4.1.1.     | Signal Types 4-                                                   |

| 4.1.2.     | Interrupt Sender Properties                                       |

| 4.2. Inte  | errupt Receiver                                                   |

| 4.2.1.     | Interrupt Receiver Properties                                     |

| 4.2.2.     | Signal Types 4-7                                                  |

| 4.2.3.     | Interrupt Timing                                                  |

| Chapter 5. | Avalon Memory-Mapped Tri-state Interfaces                         |

| 5.1. Tri-  | state Slave Signal Types                                          |

| 5.1.1.     | address Behavior                                                  |

| 5.1.2.     | outputenable and read Behavior 5-3                                |

| 5.1.3.     |                                                                   |

| 5.1.4.     |                                                                   |

| 5.2. tri-s | state Slave Properties 5-4                                        |

| 5.3. Slav  | ve Transfers 5-{                                                  |

| 5.3.1.     | Asynchronous Transfers                                            |

| 5.3        | .1.1. Setup Time 5-0                                              |

| 5.3        | .1.2. Hold Time 5-0                                               |

| 5.3        | .1.3. Example Read and Write Using Setup, Hold and Wait Times 5-0 |

| 5.3.2.     | Synchronous Transfers                                             |

| 5.3.3.     | Pipelined Slave Read Transfers 5-6                                |

| 5.4. Ma    | ster Transfers                                                    |

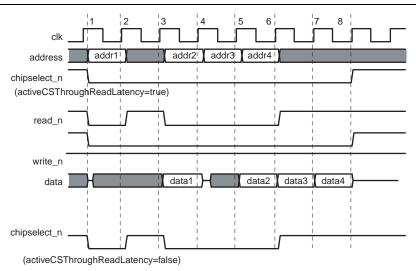

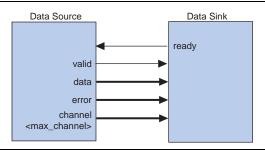

| Chapter 6. | Avalon Streaming Interfaces                                       |

|            | oduction 6-:                                                      |

| 6.1.1.     | Features                                                          |

| 6.1.2.     | Terms and Concepts 6-7                                            |

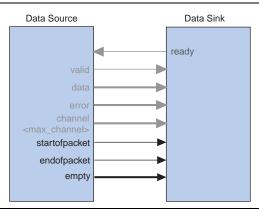

| 6.2. Ava   | alon-ST Interface Signals6-3                                      |

| 6.2.1.     | Signal Polarity 6                                                 |

|            | Signal Sequencing and Timing                                      |

|            | .2.1. Synchronous Interface                                       |

|            | .2.2. Člock Enables                                               |

| 6.3. Ava   | alon-ST Interface Properties6                                     |

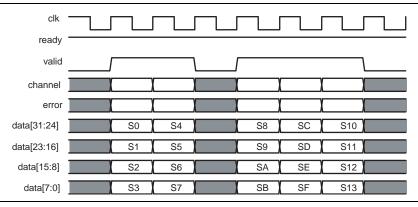

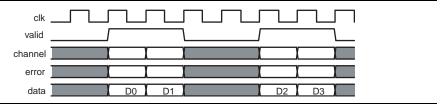

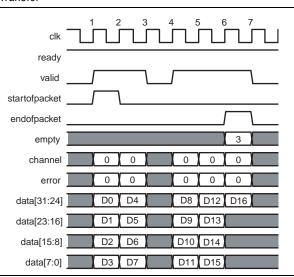

|            | pical Data Transfers 6                                            |

| 6.4.1.     | Signal Details 6-                                                 |

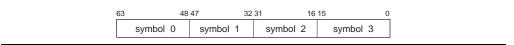

| 6.4.2.     | Data Layout 6-0                                                   |

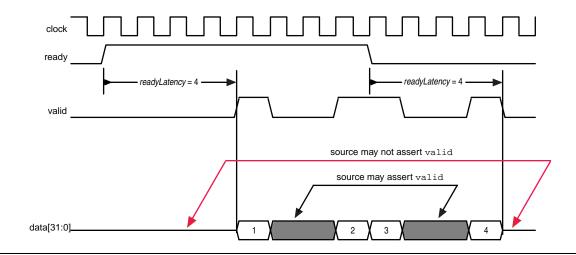

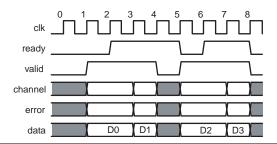

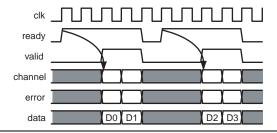

| 6.5. Dat   | ta Transfer without Backpressure 6-6                              |

| 6.6. Dat   | ta Transfer with Backpressure                                     |

|            | ket Data Transfers 6-9                                            |

| 6.7.1.     | Signal Details 6-9                                                |

| 6.7.2.     | Protocol Details                                                  |

| Chapter 7. | Conduit Interfaces                                                |

|            | perties                                                           |

|            | nals                                                              |

| Additional | Information                                                       |

|            | nt Revision History                                               |

|            | Contact Altera                                                    |

|            | phic Conventions                                                  |

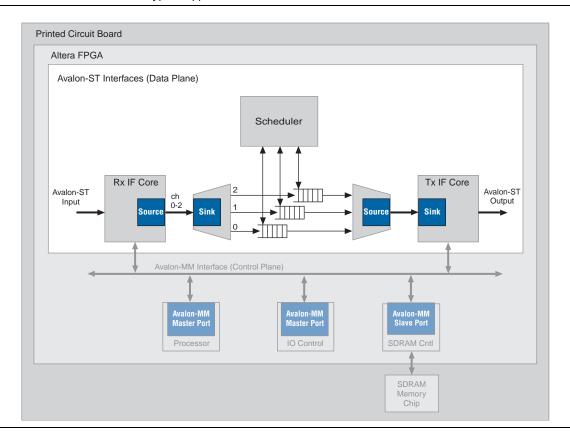

### 1. Introduction

Avalon® interfaces simplify system design by allowing you to easily connect components in an FPGA. The Avalon interface family defines interfaces for use in both high-speed streaming and memory-mapped applications. These standard interfaces are designed into the components available in the SOPC Builder and the MegaWizard® Plug-In Manager. You can also use these standardized interfaces in your custom components.

This specification defines all of the Avalon interfaces. After reading it, you should understand which interfaces are appropriate for your components and which signal types are used for which desired behaviors. There are six different interface types:

- Avalon Memory Mapped Interface (Avalon-MM)—an address-based read/write interface typical of master–slave connections.

- Avalon Streaming Interface (Avalon-ST)—an interface that supports the unidirectional flow of data, including multiplexed streams, packets, and DSP data.

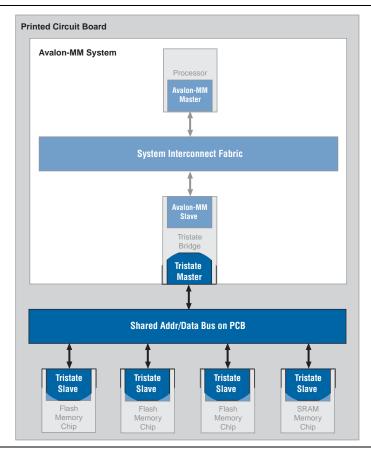

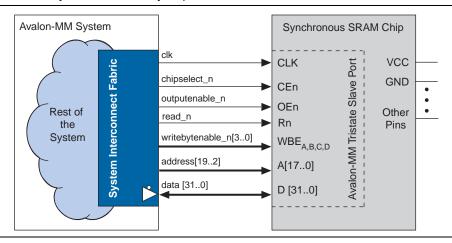

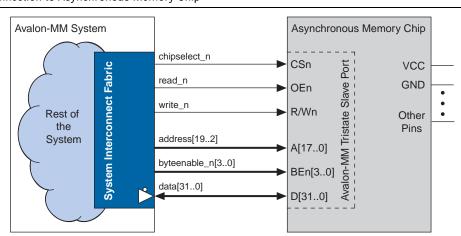

- Avalon Memory Mapped Tristate Interface—an address-based read/write interface to support off-chip peripherals. Multiple peripherals can share data and address buses to reduce the pincount of an FPGA and the number of traces on the PCB.

- Avalon Clock—an interface that drives or receives clock and reset signals to synchronize interfaces and provide reset connectivity.

- Avalon Interrupt—an interface that allows components to signal events to other components.

- Avalon Conduit—an interface that allows signals to be exported out at the top level of an SOPC Builder system where they can be connected to other modules of the design or FPGA pins.

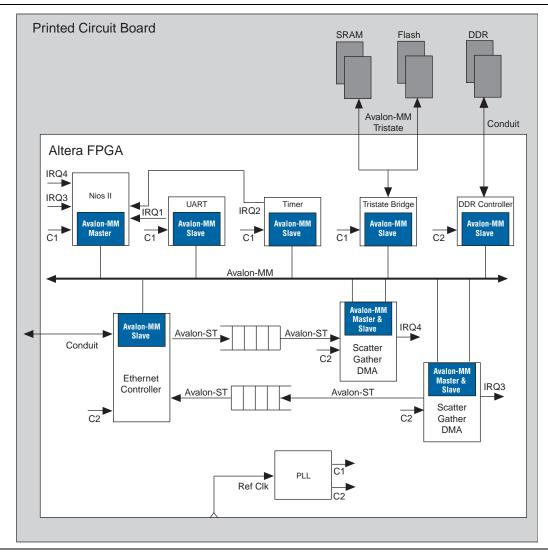

A single component can include any number of these interfaces and can also include multiple instances of the same interface type. For example, in Figure 1–1, the Ethernet Controller includes four different interface types: Avalon-MM, Avalon-ST, clock, and conduit.

This specification supersedes the previous specifications published separately for the Avalon-MM interface and the Avalon-ST interfaces.

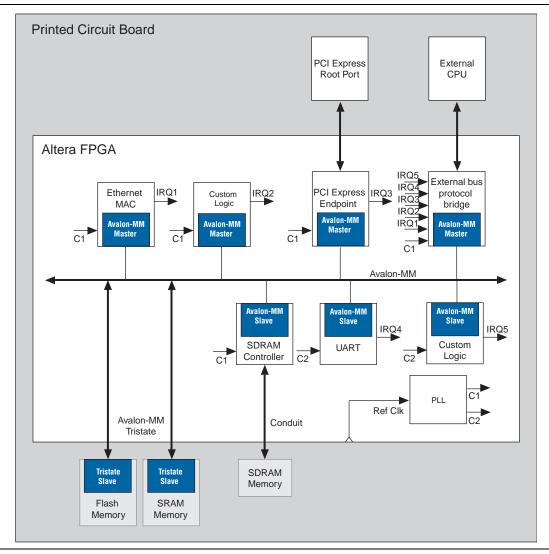

Figure 1–1 and Figure 1–2 illustrate the use of each of the Avalon interfaces.

1-2 Chapter 1: Introduction

Figure 1-1. Avalon Interfaces in a System Design with Scatter Gather DMA Controller and Nios II Processor

In Figure 1–1, the Nios® II processor accesses the control and status registers of on-chip components using an Avalon-MM interface. The scatter gather DMAs send and receive data using Avalon-ST interfaces. Four components include interrupt interfaces that are serviced by software running on the Nios II processor. A PLL accepts a clock via a clock sink interface and provides two clock sources. Finally, two components include conduit interfaces to access off-chip resources.

Chapter 1: Introduction 1–3

Figure 1–2. Avalon Interfaces in a System Design with PCI Express Endpoint and External Processor

In Figure 1–2, an external processor accesses the control and status registers of on-chip components via an external bus bridge with an Avalon-MM interface. The PCI Express root port controls the printed circuit board and the other components of the FPGA by driving an on-chip PCI Express endpoint with an Avalon-MM master interface. Five components include interrupts that are handled by the external processor. As in Figure 1–1, a PLL accepts a reference clock via a clock sink interface and provides two clock sources. Finally, the flash and SRAM memories use an Avalon-MM tristate interface to share FPGA pins.

## 1.1. Avalon Properties and Parameters

Avalon interfaces use properties to describe their behavior. For example, the setupTime and holdTime properties of an Avalon-MM tristate interface specify the timing of external memory devices. The maxChannel property of Avalon-ST interfaces allows you to state the number of channels supported by the interface. The specification for each interface type defines all of its properties and specifies the default values. For a complete list of properties for each interface type, refer to the following sections:

- For Avalon-MM properties, refer to: "Slave Interface Properties" on page 3–5 and "Master Interface Properties" on page 3–21

- For Avalon-MM tristate properties, refer to: "tri-state Slave Properties" on page 5–4

- For Avalon-ST properties, refer to: "Avalon-ST Interface Properties" on page 6–4

- For the properties of interrupts, refer to: "Interrupt Sender Properties" on page 4–1 and "Interrupt Receiver Properties" on page 4–2

## 1.2. Signal Types

Each of the Avalon interfaces defines a number of signal types and their behavior. Many signal types are optional, allowing component designers the flexibility to select only the signal types necessary. For example, the Avalon-MM interface includes optional beginbursttransfer and burstcount signal types used only for components that support bursting. The Avalon-ST interface includes the optional startofpacket and endofpacket signal types for interfaces that support packets.

With the exception of conduit interfaces, each interface may only include one signal of each signal type. Active-low signals are permitted for many signal types. Active-high signals are generally used in this document.

## 1.3. Interface Timing

Subsequent chapters of this document include timing information that describes transfers for individual interface types interfaces. There is no guaranteed performance for any of these interfaces; actual performance depends on many factors, including component design and system implementation.

Most Avalon interfaces must not be edge sensitive to signals other than the clock, because the signals may transition multiple times before they stabilize. The exact timing of signals between clock edges varies depending upon the characteristics of the selected Altera device.

### 1.4. Related Documents

You can find additional information on related topics in the following documents:

Quartus II Handbook Volume 4: SOPC Builder

This volume includes information on memory-mapped and streaming interfaces, Tcl scripting, designing memory sub-systems, and interconnect components.

Quartus II Handbook Volume 5: Embedded Peripherals

This volume includes documentation for the many embedded peripherals that are available in SOPC Builder.

■ Building a Component Interface with Tcl Scripting Commands.

This is a reference for a programmatic interface that you can use to define SOPC Builder components.

You can also complete a one-hour online course, *Using SOPC Builder*, that is available on the Altera web site.

1–6 Chapter 1: Introduction

Related Documents

## 2. Clock Interfaces

Clock interfaces are used to define the clock and resets used by a component. Typical components have one or more clock inputs; they rarely have clock outputs. A phase locked loop (PLL) is an example of a component that has both a clock input and clock outputs. Figure 2–1 is a simplified illustration showing the most important inputs and outputs of a PLL component.

**PLL Core** altpll Megafunction reset areset Clock Output c0 Interface1 с1 Clock Clock Output Input Interface2 Interface Clock Output Interface n ref\_clk inclk

Figure 2-1. PLL Core Clock Outputs and Inputs

## 2.1. Clock Input (Sink)

A clock input interface provides synchronization and reset control for a component. A typical component has a clock input to provide a timing reference for other interfaces and internal logic.

All reset inputs are connected to the logical OR of all system reset requests. Reset inputs are always asserted asychronously. If the clock input interface has a clock input and a reset input, the reset is deasserted synchronously to the clock input.

## 2.1.1. Properties

There are no properties for the clock sink interface.

## 2.1.2. Signal Types

Table 2–1 lists the clock input signals.

Table 2–1. Clock Input Signal Types

| Signal Type      | Width | Direction | Required | Description                                                                                |

|------------------|-------|-----------|----------|--------------------------------------------------------------------------------------------|

| clk              | 1     | Input     | No       | A clock signal. Provides synchronization for internal logic and for other interfaces.      |

| reset<br>reset_n | 1     | Input     | No       | Reset input. Resets the internal logic of an interface or component to a determined state. |

|                  |       |           |          | reset is synchronized to the clock input in the same interface.                            |

#### 2.1.3. associatedClock Interfaces

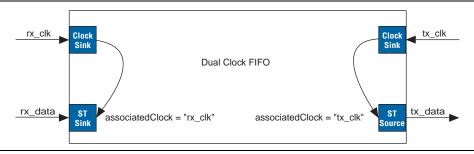

All synchronous interfaces have an associatedClock property that specifies which clock input on the component is used as a synchronization reference for the interface. This property is illustrated in Figure 2–2.

Figure 2-2. associatedClock Property

## 2.2. Clock Output (Source)

A clock source interface, or clock output interface, is an interface that drives a clock signal out of a component. Clock output interfaces cannot have reset signals.

## 2.2.1. Properties

There are no properties for clock source interfaces.

## 2.2.2. Signal Types

Table 2–2 lists the clock source signals.

Table 2–2. Clock Source Signal Types

| Signal Type | Width | Direction | Required | Description             |

|-------------|-------|-----------|----------|-------------------------|

| clk         | 1     | Output    | Yes      | An output clock signal. |

## 3. Avalon Memory-Mapped Interfaces

### 3.1. Introduction

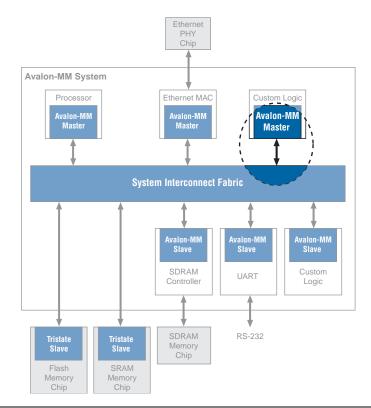

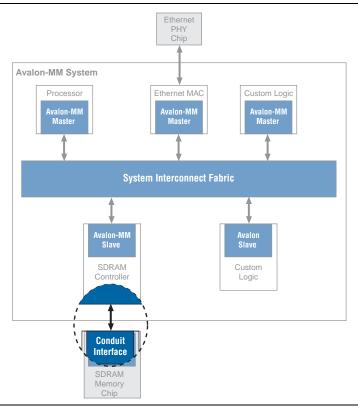

Avalon Memory-Mapped (Avalon-MM) interfaces are used for read/write interfaces on master and slave components in a memory-mapped system. These components include microprocessors, memories, UARTs, and timers, and have master and slave interfaces connected by a system interconnect fabric. Avalon-MM interfaces can describe a wide variety of components, from an SRAM which supports simple, fixed-cycle read/write transfers to a more complex, pipelined interface capable of burst transfers. Figure 3–1 shows a typical system, highlighting the Avalon-MM slave interface connection to the system interconnect fabric.

PHY Chip Avalon-MM System Ethernet MAC Custom Logic Processor **System Interconnect Fabric** Avalon-MM Slave RAM Custom UART Controller Logic RAM RS-232 Memory SRAM

Figure 3-1. Focus on Avalon-MM Slave Transfers

Features of the Avalon-MM interface include:

Chip

- Definition of a point-to-point connection between a component and an interconnect fabric

- Freedom to implement only the required subset of signals

Memory Chip

- Variable data widths: 8, 16, 32, 64, . . . 1024

- Automatic interconnect generation

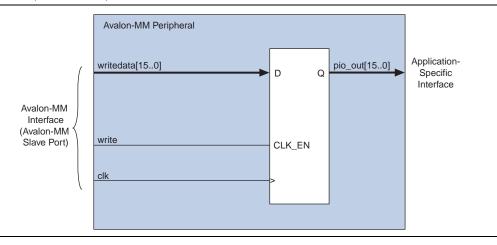

Avalon-MM components typically include only the signals required for the component logic. The 16-bit general-purpose I/O peripheral shown in Figure 3–2 only responds to write requests, therefore it only includes the slave signals required for write transfers.

Figure 3–2. Example Slave Component

Each signal in an Avalon-MM slave corresponds to exactly one Avalon-MM signal type. An Avalon-MM port can use only one instance of each signal type.

## 3.2. Slaves

Table 3–1 lists the signal types that constitute the Avalon-MM slave. This specification does not require all signals to exist in an Avalon-MM slave. The minimum requirements are readdata for a read-only interface or writedata and write for a write-only interface.

**Table 3–1.** Avalon-MM Slave Port Signals (1) (Part 1 of 4)

| Signal Type         | Width                                   | Dir | Req'd | Description                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|---------------------|-----------------------------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Fundamental Signals |                                         |     |       |                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| read_n              | 1                                       | In  | No    | Asserted to indicate a read transfer. If present, readdata is required.                                                                                                                                                                                                                  |  |  |  |  |  |

| write<br>write_n    | 1                                       | In  | No    | Asserted to indicate a write transfer. If present, writedata is required.                                                                                                                                                                                                                |  |  |  |  |  |

| address             | 1-32                                    | In  | No    | Specifies an offset into the slave address space. Each slave address value selects a word of slave data. For example, address=0 selects the first <slave data="" width=""> bits of slave data; address=1 selects the second <slave data="" width=""> bits of slave data.</slave></slave> |  |  |  |  |  |

| readdata            | 8,16,32,<br>64,128,<br>256,512,<br>1024 | Out | No    | The readdata provided by the slave in response to a read transfer.                                                                                                                                                                                                                       |  |  |  |  |  |

**Table 3–1.** Avalon-MM Slave Port Signals (1) (Part 2 of 4)

| Signal Type               | Width                                       | Dir | Req'd | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------|---------------------------------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| writedata                 | 8,16,32,  <br>64,128,  <br>256,512,<br>1024 | In  | No    | Data from the system interconnect fabric for write transfers.  The width must be the same as the width of readdata if both are present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| byteenable byteenable_n   | 1,2,4,8,<br>16,32,64,<br>128                | In  | No    | Enables specific byte lane(s) during transfers.  Each bit in byteenable corresponds to a byte in writedata and readdata. During writes, byteenables specify which bytes are being written to; other bytes should be ignored by the slave. During reads, byteenables indicates which bytes the master is reading. Slaves that simply return readdata with no side effects are free to ignore byteenables during reads.  When more than one bit is asserted, all asserted lanes are adjacent. The number of adjacent lines must be a power of two, and the specified bytes must be aligned on an address boundary for the size of the data. The following values are legal for a 32-bit slave:  1111 writes full 32 bits  0011 writes lower 2 bytes |  |

|                           |                                             |     |       | 1100 writes upper 2 bytes 0001 writes byte 0 only 0010 writes byte 1 only 0100 writes byte 2 only 1000 writes byte 3 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| begintransfer             | 1                                           | In  | No    | Asserted by the system interconnect fabric for the first cycle of each transfer regardless of waitrequest and other signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                           |                                             |     | Wait- | State Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| waitrequest waitrequest_N | 1                                           | Out | No    | Asserted by the slave when it is unable to respond to a read or write request. When asserted, the control signals to the slave, with the exception of begintransfer and beginbursttransfer, remain constant, as is illustrated by Figure 3–7 on page 3–13. An Avalon-MM slave may assert waitrequest during idle cycles. An Avalon-MM master may initiate a transaction when waitrequest is asserted. The design of Avalon-MM slaves must take these possibilities into account.                                                                                                                                                                                                                                                                  |  |

**Table 3–1.** Avalon-MM Slave Port Signals (1) (Part 3 of 4)

| Signal Type                      | Width | Dir | Req'd  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------|-------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| arbiterlock<br>arbiterlock_n     | 1     | In  | No     | arbiterlock ensures that once a master wins arbitration, it maintains access to the slave for multiple transactions. It is de-asserted coincident with read or write and with the deassertion of the last locked transaction read or write signal. Arbiterlock assertion does not guarantee that arbitration will be won, but after the arbiterlock-asserting master has been granted, it retains grant until it deasserts arbiterlock, whether or not it is making an access. |

|                                  |       |     |        | A master equipped with arbiterlock cannot be a burst master. Arbitration priority values for arbiterlock-equipped masters are ignored.                                                                                                                                                                                                                                                                                                                                         |

|                                  |       |     |        | arbiterlock is particularly useful for read-modify-write operations, where master A reads 32-bit data that has multiple bitfields, changes one field, and writes the 32-bit data back. If master B were to able to write between Master A's read and the write, master A's write would undo what master B had done.                                                                                                                                                            |

|                                  |       |     |        | arbiterlock is also for tristate-pin sharing: an SDRAM controller can use it to lock arbitration to execute an unbroken sequence of commands to an SDRAM device.                                                                                                                                                                                                                                                                                                               |

|                                  |       | •   | Pipe   | eline Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| readdatavalid<br>readdatavalid_n | 1     | Out | No     | Used for variable-latency, pipelined read transfers. Asserted by the slave to indicate that the readdata signal contains valid data in response to a previous read request. A slave with readdatavalid must assert this signal for one cycle for each read access it has received. There must be at least one cycle of latency between acceptance of the read and assertion of readdatavalid. Figure 3–5 on page 3–10 illustrates the readdatavalid signal.                    |

|                                  | I     | ı   | Bu     | ırst Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| burstcount                       | 1-11  | In  | No     | During the first cycle of a burst, burstcount indicates the number of transfers the burst contains. A burstcount port of width <n> can encode a max burst of size 2(<n>-1). The minimum burstcount is 1.</n></n>                                                                                                                                                                                                                                                               |

| beginbursttransfer               | 1     | In  | No     | Asserted for the first cycle of a burst to indicate when a burst transfer is starting. This signal is deasserted after one cycle regardless of the value of waitrequest. Refer to Figure 3–3 for an example of its use.                                                                                                                                                                                                                                                        |

|                                  | •     |     | Flow ( | Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| readyfordata                     | 1     | Out | No     | Used for transfers with flow control. Indicates that the component is ready for a write transfer.                                                                                                                                                                                                                                                                                                                                                                              |

| dataavailable                    | 1     | Out | No     | Used for transfers with flow control. Indicates that the component is ready for a read transfer.                                                                                                                                                                                                                                                                                                                                                                               |

**Table 3–1.** Avalon-MM Slave Port Signals (1) (Part 4 of 4)

| Signal Type    | Width | Dir | Req'd | Description                                                     |  |  |

|----------------|-------|-----|-------|-----------------------------------------------------------------|--|--|

| Reset Signals  |       |     |       |                                                                 |  |  |

| resetrequest   | - '   |     |       |                                                                 |  |  |

| resetrequest_n |       |     |       | The system reset signal is the logical OR of all reset signals. |  |  |

#### Notes to Table 3-1:

(1) All Avalon signals are active high. Avalon signals that can also be asserted low list a  $\_n$  versions of the signal in the **Signal Type** column.

## 3.3. Slave Interface Properties

Table 3–2 describes the interface properties for an Avalon-MM slave interface.

**Table 3–2.** Avalon-MM Slave Interface Properties (Part 1 of 2)

| Name          | Default<br>Value | Legal Values           | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| readLatency   | 0                | 0–63                   | Read latency for fixed-latency slaves. Not used on interfaces that include the readdatavalid signal. Refer to Figure 5–5 on page 5–9 for an timing diagram that uses this property.                                                                                                                                                                                                                                           |

| timingUnits   | cycles           | cycles,<br>nanoseconds | Specifies the units for setupTime, holdTime, writeWaitTime and readWaitTime. Use cycles for synchronous devices and nanoseconds for asynchronous devices. Almost all Avalon-MM slave devices are synchronous. One example of a device that requires asynchronous timing is an Avalon-MM slave that reads and writes an off-chip bidirectional port. That off-chip device might have a fixed settling time for bus turnaround. |

| writeWaitTime | 0                | 0–1000<br>cycles       | For slave interfaces that don't use the waitrequest signal, writeWaitTime indicates the number of cycles or nanoseconds before the slave accepts a write. The timing is as if the slave asserted waitrequest for writeWaitTime cycles or nanoseconds. Refer to Figure 5–4 on page 5–8 for a timing diagram that uses this property.                                                                                           |

| readWaitTime  | 1                | 0-1000<br>cycles       | For slave interfaces that don't use the waitrequest signal, readWaitTime indicates the number of cycles or nanoseconds before the slave responds to a read. The timing is as if the slave asserted waitrequest for readWaitTime Cycles.                                                                                                                                                                                       |

| holdTime      | 0                | 0-1000<br>cycles       | Specifies time in timingUnits between the deassertion of write and the deassertion of chipselect, address, and data. (Only applies to write transactions.)                                                                                                                                                                                                                                                                    |

| setupTime     | 0                | 0-1000<br>cycles       | Specifies time in timingUnits between the assertion of chipselect, address, and data and assertion of read or write.                                                                                                                                                                                                                                                                                                          |

Table 3-2. Avalon-MM Slave Interface Properties (Part 2 of 2)

| Name                               | Default<br>Value | Legal Values                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| maximumPendingRead<br>Transactions | 1 (1)            | 1–64                                            | The maximum number of pending reads which can be queued up by the slave. Refer to Figure 3–5 on page 3–10 for a timing diagram that uses this property.                                                                                                                                                                                                                                                                                                        |

| burstOnBurstBoundariesOnly         | false            | true,false                                      | If true, burst transfers presented to this interface are guaranteed to begin at addresses which are multiples of the burst size.                                                                                                                                                                                                                                                                                                                               |

| linewrapBursts                     | false            | true,false                                      | If true, indicates that the slave implements a line wrapping burst instead of an incrementing burst. With a wrapping burst, when the address reaches a burst boundary, it wraps back to the previous burst boundary such that only the low order bits need to be used for addressing. To address 0xC, a wrapping burst with burst boundaries every 32 bytes across a 32-bit interface would write to addresses 0xC, 0x10, 0x14, 0x18, 0x1C, 0x0, 0x4, and 0x8. |

| maxBurstSize                       | 1                | 64                                              | The maximum burst size that a slave can accept.                                                                                                                                                                                                                                                                                                                                                                                                                |

| bridgesToMaster                    | null             | Avalon-MM<br>master on the<br>same<br>component | An Avalon-MM bridge consists of a slave and a master, and has the property that an access to the slave requesting a particular byte or bytes will cause the same byte or bytes to be requested by the master.                                                                                                                                                                                                                                                  |

| associatedClock                    |                  | _                                               | Name of the clock interface that this Avalon-MM slave interface is synchronous to.                                                                                                                                                                                                                                                                                                                                                                             |

#### Note to Table 3-2:

## 3.4. Slave Timing

This section describes issues related to timing and sequencing of Avalon-MM slave signals.

## 3.4.1. Synchronous Interface

The Avalon-MM interface is a synchronous protocol. Each Avalon-MM port is synchronized to an associated clock interface. Signals may be combinational if they are driven from the outputs of registers that are synchronous to the clock signal. An Avalon-MM component must not be sensitive to any signal besides the reference clock. This document does not dictate how or when signals transition between clock edges and timing diagrams are devoid of fine-grained timing information.

#### 3.4.2. Performance

There is no guaranteed performance of the Avalon-MM interface. The maximum performance is dependent on component design and system implementation.

<sup>(1)</sup> If a component accepts more read transfers than the value indicated here, the internal pending read FIFO may overflow, causing the system to

#### 3.4.3. Electrical Characteristics

The Avalon-MM interface specification does not specify any electrical characteristics.

### 3.5. Slave Transfers

This section defines two basic concepts before introducing the slave transfer types.

- *Transfer*—A transfer is a read or write operation of a word of data, between an Avalon-MM slave and the system interconnect fabric. Avalon-MM transfers words ranging in size from 8–1024 bits. Transfers take one or more clock cycles to complete.

- Both masters and slaves are part of a transfer; the Avalon-MM master initiates the transfer and the Avalon-MM slave responds to it.

- Master-slave pair —This term refers to the master port and slave port involved in a transfer. During a transfer, the master port's control and data signals pass through the system interconnect fabric and interact with the slave port.

### 3.5.1. Typical Slave Read and Write Transfers

This section describes a typical Avalon-MM slave that supports read and write transfers with slave-controlled waitrequest. The slave can stall the system interconnect fabric for as many cycles as required by asserting the waitrequest signal. If a slave uses waitrequest for either read or write transfers, it must use waitrequest for both.

The slave receives address, byteenable, read or write, and writedata after the rising edge of the clock. The slave port must assert waitrequest before the next rising clock edge to hold off the transfers. When the slave asserts waitrequest, the transfer is delayed and the address and control signals are held constant. Transfers complete on the rising edge of the first clk after the slave port deasserts waitrequest.

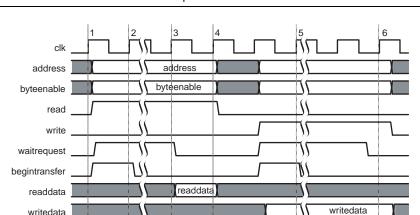

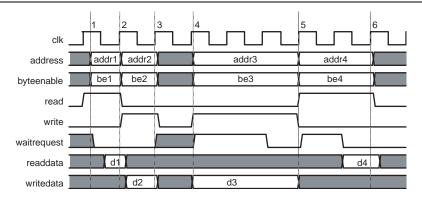

There is no limit on how long a slave port can stall. Therefore, you must ensure that a slave port does not assert waitrequest indefinitely. Figure 3–3 shows read and write transfers using waitrequest.

Figure 3-3. Slave Read and Write Transfers with Waitrequest

#### Notes to Figure 3-3:

- (1) address, read, and begintransfer are asserted after the rising edge of clk. waitrequest is asserted stalling the transfer.

- (2) waitrequest is sampled. Because waitrequest is asserted, the cycle becomes a wait-state, and address, read, write, and byteenable remain constant. Begintransfer is not held constant.

- (3) The slave presents valid readdata and deasserts waitrequest.

writedata

- (4) readdata and deasserted waitrequest are sampled, completing the transfer.

- (5) address, writedata, byteenable, begintransfer, and write signals are asserted. The slave responds by asserting waitrequest, stalling the transfer.

- (6) The slave captures writedata and deasserts waitrequest, ending the transfer.

#### 3.5.2. Slave Read and Write Transfers with Fixed Wait-States

waitrequest for <*n*> cycles per transfer.

Instead of using waitrequest to hold off a transfer, a slave can specify fixed wait-states using the readWaitTime and writeWaitTime properties. The address and control signals (byteenable, read, and write) are held constant for the duration of the transfer. The read/write timing with readWaitTime/writeWaitTime set to <n> is exactly the same as asserting

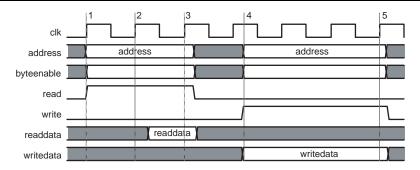

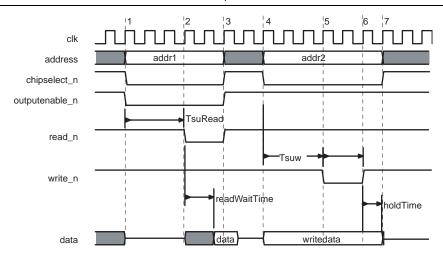

Figure 3-4 shows an example slave read and write transfers with writeWaitTime = 2 and readWaitTime = 1.

Figure 3-4. Slave Read and Write Transfer with Fixed Wait-States

#### Notes to Figure 3-4:

- (1) The master asserts address and read on the rising edge of clk.

- (2) The next rising edge of clk marks the end of the first and only wait-state cycle because the readWaitTime is 1.

- (3) The slave captures readdata on the rising edge of clk, and the read transfer ends.

- (4) writedata, address, byteenable, and write signals are available to the slave.

- (5) Because writeWaitTime is 2, the transfer terminates after completing. The data and control signals are held constant until this time.

Transfers with a single wait-state are commonly used for synchronous, on-chip peripherals. The peripheral can capture address and control signals on the rising edge of clk, and has one full cycle to return data. Components with zero wait-states are allowed, but may decrease achievable frequency because they generate the response in the same cycle as the request.

### 3.5.3. Pipelined Transfers

Avalon-MM pipelined read transfers increase the throughput for synchronous slave devices that require several cycles to return data for the first access, but can return one data value per cycle for some time thereafter. New pipelined read transfers can be started before readdata for the previous transfers is returned. Write transfers cannot be pipelined.

A pipelined read transfer is divided into two phases: an address phase and a data phase. A master initiates a transfer by presenting the address during the address phase; a slave port fulfills the transfer by delivering the data during the data phase. The address phase for a new transfer (or multiple transfers) can begin before the data phase of a previous transfer completes. This delay is called *pipeline latency*, which is the duration from the end of the address phase to the beginning of the data phase.

The key differences between how wait-states and pipeline latency affect transfer timing is as follows:

- Wait-states—Wait-states determine the length of the address phase, and limit the maximum throughput of a port. If a slave requires one wait-state to respond to a transfer request, then the port requires at least two clock cycles per transfer.

- Pipeline Latency—Pipeline latency determines the time until data is returned independently of the address phase. A pipelined slave port with no wait-states can sustain one transfer per cycle, even though it may require several cycles of latency to return the first unit of data.

Wait-states and pipelined reads can be supported concurrently, and pipeline latency can be either fixed or variable, as discussed in the following sections.

#### 3.5.3.1. Slave Pipelined Read Transfer with Variable Latency

An Avalon-MM pipelined slave takes one or more cycles to produce data after address and control signals have been captured. A pipelined slave port may have multiple pending read transfers at any given time. Variable-latency pipelined read transfers use the same set of signals as non-pipelined read transfers, with one additional signal, readdatavalid. Slave peripherals that use readdatavalid are considered pipelined with variable latency; the readdata and readdatavalid signals can be asserted the cycle after the read cycle is asserted, at the earliest.

The slave port must return readdata in the same order that it accepted the addresses. Pipelined slave ports with variable latency must use waitrequest. The slave can assert waitrequest to stall transfers to maintain the number of pending transfers at an acceptable level.

The maximum number of pending transfers is a property of the slave interface. The system interconnect fabric builds logic which routes readdata to the requesting masters, parameterized by this maximum number. It is the responsibility of the slave interface, not the system interconnect fabric, to keep the number of pending reads from exceeding the stated maximum. Typically, the slave interface restricts the number of pending reads by asserting waitrequest when that number has reached the maximum value

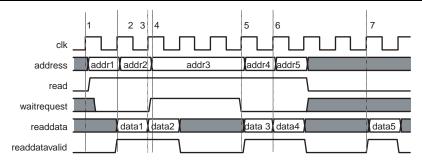

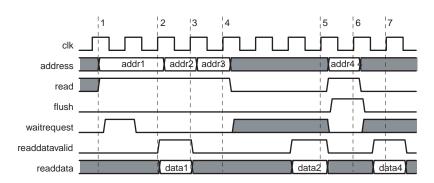

Figure 3–5 shows several slave read transfers between the system interconnect fabric and a pipelined slave with variable latency. In this example, the slave can accept a maximum of two pending transfers and uses waitrequest to prevent overrunning this maximum.

Figure 3–5. Slave Pipelined Read Transfers with Variable Latency

#### Notes to Figure 3-5:

- (1) The master asserts address and read, initiating a read transfer.

- (2) The slave captures addr1, and immediately provides the response data1 and asserts readdatavalid.

- (3) The slave captures addr2 and immediately provides the response data2 and asserts readdatavalid.

- (4) The slave asserts waitrequest causing the third transfer to be stalled for 2 cycles.

- (5) The slave drives readdatavalid and valid readdata in response to the third read transfer.

- (6) The data from transfer 3 is captured by the interconnect as addr4 is captured by the slave.

- (7) data5 is presented with readdatavalid completing the data phase for the final pending read transfer.

If the slave cannot handle a write transfer while it is processing pending read transfers, the slave must assert its waitrequest and stall the write operation until the pending read transfers have completed. The Avalon-MM specification does not define the value of readdata in the event that a slave accepts a write transfer to the same address as a currently pending read transfer. Pipelined slaves with variable latency must support waitrequest.

#### 3.5.3.2. Slave Pipelined Read Transfer with Fixed Latency

The address phase for fixed latency slave read transfers is identical to the variable latency case. After the address phase, a pipelined slave port with fixed read latency takes a fixed number of clock cycles to return valid readdata, as indicated by the readWaitTime property. The system interconnect fabric captures readdata on the appropriate rising clock edge, and the data phase ends.

During the address phase, the slave port can assert waitrequest to hold off the transfer or can specify readWaitTime for a fixed number of wait states. The address phase ends on the next rising edge of clk after wait-states, if any.

During the data phase, the slave drives readdata after a fixed latency. If the slave has a read latency of <*n*>, the slave port must present valid readdata on the <*nth*> rising edge of clk after the end of the address phase.

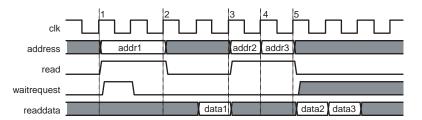

Figure 3–6 shows multiple data transfers to a slave pipelined port that uses waitrequest and has a fixed read latency of 2 cycles.

Figure 3-6. Slave Pipelined Read Transfer with Fixed Latency of Two Cycles

#### Notes to Figure 3-6:

- (1) A master initiates a read transfer by asserting read and addrl. The slave asserts waitrequest to hold off the transfer for one cycle.

- (2) The slave deasserts waitrequest and captures addr1 at the rising edge of clk. The address phase ends here.

- (3) The slave presents valid readdata after 2 cycles, ending the transfer.

- (4) addr2 and read are asserted for a new read transfer.

- (5) The master initiates a third read transfer during the next cycle, before the data from the prior transfer is returned.

#### 3.5.4. Burst Transfer

A burst executes multiple transfers as a unit, rather than treating every word independently. Bursts may increase throughput for slave ports that achieve greater efficiency when handling multiple word at a time, such as DDR. The net effect of bursting is to lock the arbitration for the duration of the burst. If a slave provides both read and write functionality and supports bursting, it must support both burst reads and burst writes.

To support bursts, an Avalon-MM slave includes a burstcount input signal. If a slave has a burstcount input, it is considered burst capable.

The burstcount signal behaves as follows:

- At the start of a burst, burstcount presents the number of sequential transfers in the burst.

- For width < n > of burstcount, the maximum burst length is  $2^{< N > -1}$ . The minimum legal burst length is one.

To support slave read bursts, a slave must also support:

- wait-states with the waitrequest signal.

- Pipelined transfers with variable latency with the readdatavalid signal.

At the start of a burst, the slave sees the address and a burst length value on burstcount. For a burst with an address of <a> and a burstcount value of <b>, the slave must perform <b> consecutive transfers starting at address <a>. The burst completes after the slave receives (write) or returns (read) the <Bth> word of data. The bursting slave must capture address and burstcount only once for each burst. The slave logic must infer the address for all but the first transfers in the burst. A slave can also use the input signal beginbursttransfer, which the system interconnect fabric asserts for the first cycle of each burst.

#### 3.5.4.1. Slave Write Bursts

These rules apply when a slave write burst begins with burstcount greater than one:

- If a burstcount of <n> is presented at the beginning of the burst, then the slave must accept <n> successive units of writedata to complete the burst. Arbitration between the master-slave pair is locked until the burst completes, guaranteeing that data arrives, in order, from the master port that initiated the burst.

- The slave must only capture writedata when write is asserted. During the burst, write can be deasserted to indicate that it is not presenting valid writedata. Deasserting write does not terminate the burst; it only delays it.

- The slave can delay a transfer by asserting waitrequest which forces writedata, write, and byteenable to be held constant, as usual.

- The functionality of the byteenable signal is the same for bursting and non-bursting slaves. For a 32-bit master burst-writing to a 64-bit slave, starting at byte address 4, the first write transfer seen by the slave is at its address 0, with byteenable = 8b′11110000.

- The byteenable signals do not all have to be asserted. A burst master writing unaligned data can use the byteenable signal to identify the data being written.

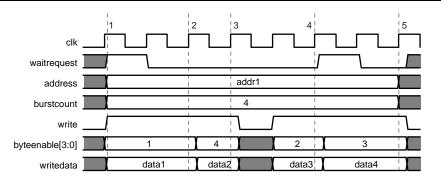

Figure 3–7 demonstrates a slave write burst of length 4. In this example, the slave port asserts waitrequest twice delaying the burst.

Figure 3-7. Slave Write Burst

#### Notes to Figure 3-7:

- (1) The master asserts address, burstcount, write, and drives the first unit of writedata. The slave immediately asserts waitrequest, indicating that it is not ready to proceed with the transfer.

- (2) waitrequest is low; the slave captures addr1, burstcount, and the first unit of writedata. On subsequent cycles of the transfer, address and burstcount are ignored.

- (3) The slave port captures the second unit of data at the rising edge of clk.

- (4) The burst is paused while write is deasserted.

- (5) The slave captures the third unit of data at the rising edge of clk.

- (6) The slave asserts waitrequest. In response, all outputs are held constant through another clock cycle.

- (7) The slave captures the last unit of data on this rising edge of clk. The slave write burst ends.

In Figure 3–7, the beginbursttransfer signal is asserted for the first clock cycle of a burst and is deasserted on the next clock cycle. Even if the slave asserts waitrequest, the beginbursttransfer signal is only asserted for the first clock cycle.

#### 3.5.4.2. Slave Read Bursts

Slave read bursts are similar to slave pipelined read transfers with variable latency. A read burst has distinct address and data phases, and the slave port uses the readdatavalid signal to indicate when it is presenting valid readdata. The difference is that a single read burst address results in multiple data transfers.

These rules apply to slave read bursts:

- When burstcount is <*n*>, the slave must return <*n*> words of readdata to complete the burst.

- The slave presents each word by providing readdata and asserting readdatavalid for a cycle. Deassertion of readdatavalid delays but does not terminate the burst data phase.

- The byteenables presented with a read burst command apply to all cycles of the burst. A byteenable value of 1 means that the least significant byte is being read across all of the read cycles.

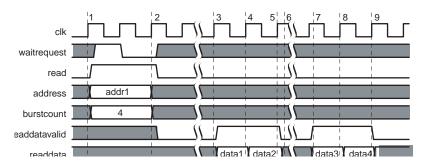

Figure 3–8 illustrates a system with two bursting masters accessing a slave. Note that Master B can drive a read request before the data has returned for Master A.

Figure 3–8. Slave Read Burst

#### Notes to Figure 3-8:

- (1) Master A asserts address (A0), burstcount, and read after the rising edge of clk. The slave asserts waitrequest, causing all inputs except beginbursttransfer to be held constant through another clock cycle.

- (2) The slave captures A0 and burstcount at this rising edge of clk. A new transfer could start on the next cycle.

- (3) Master B drives address (A1), burstcount, and read. The slave asserts waitrequest, causing all inputs except beginbursttransfer to be held constant. The slave could have returned read data from the first read request at this time, at the earliest.

- (4) The slave presents valid readdata and asserts readdatavalid, transferring the first word of data for master A.

- (5) The second word for master A is transferred. The slave deasserts readdatavalid pausing the read burst. The slave port can keep readdatavalid deasserted for an arbitrary number of clock cycles.

- (6) The first word for master B is returned.

#### 3.5.4.3. Line-Wrapped Bursts

Processors with data or instruction caches gain efficiency by using line-wrapped bursts. When a processor requests data, and the data is not in the cache, the cache controller reads enough data from the memory to fill the entire cache line. For a processor with a cache line size of 64 bytes, a cache miss causes 64 bytes to be read from memory. If the processor reads from address 0xC when the cache miss occurred, then an incrementing addressing burst uses read addresses 0x0, 0x4, 0x8, 0xC, 0x10, 0x14, 0x18, and 0x1C – the data that the processor requested is not available until the fourth read. With wrapping bursts, the address order is 0xC, 0x10, 0x14, 0x18, 0x1C, 0x0, 0x4, and 0x8 such that the data that the processor requested is returned first.

For more information about burst transfers and burst adapters refer to the *Avalon Memory-Mapped Design Optimizations* chapter in the *Embedded Design Handbook*.

### 3.5.4.4. Flow Control

A slave can support the dataavailable and readyfordata signals to indicate when it has data available for reading or has space available to which data can be written. Masters that have the doStreamReads and doStreamWrites properties set see waitrequest asserted when they access a slave with the dataavailable and readyfordata signals deasserted, respectively.

For flow control to work, both interfaces in the master-slave pair must support it. If one or both of the ports does not use flow control, then the transfer proceeds as if neither port had it. Flow control signals cannot be used with Avalon-MM tristate ports.

In a master-slave pair that uses flow control, after a master port initiates a transfer, the system interconnect fabric initiates a transfer with the target slave port only if the readyfordata or dataavailable signals indicate that the slave port it is ready for the transfer. While the slave port is not ready, the system interconnect fabric forces the master port to wait.

A slave port can assert dataavailable at any time to indicate that it has read data available. While dataavailable is asserted, a new transfer from a master port with flow control can begin on the next rising edge of clk. A slave port can only deassert dataavailable at the end of a read transfer. The signal is immediately valid for successive transfers that might follow.

A slave port can assert readyfordata at any time to indicate that it can accept write data. While readyfordata is asserted, a new transfer from a master port with flow control can begin on the next rising edge of clk.

Flow control is a deprecated feature. Altera recommends that you use the Avalon Streaming (Avalon-ST) and the ready and valid signals for new designs. For more information about Avalon-ST interfaces refer to Chapter 6, Avalon Streaming Interfaces.

## 3.6. Address Alignment

For systems in which master and slave data widths differ, the system interconnect manages address alignment issues. The Avalon-MM interface resolves data width differences, so that any master port can communicate with any slave port, regardless of the respective data widths.

### 3.6.1. Avalon-MM Slave Addressing

*Dynamic bus sizing* refers to a service provided by the system interconnect fabric that dynamically manages data during transfers between master-slave pairs of differing data widths, such that all slave data are aligned in contiguous bytes in the master address space.

If the master is wider than the slave, data bytes in the master address space map to multiple locations in the slave address space. For example, when a 32-bit master port performs a read transfer from a 16-bit slave port, the system interconnect fabric executes two read transfers on the slave side on consecutive addresses, and presents 32-bits of slave data back to the master port.

If the master is narrower than the slave, then the system interconnect fabric manages the slave byte lanes. During master read transfers, the system interconnect fabric presents only the appropriate byte lanes of slave data to the narrower master. During master write transfers, the system interconnect fabric automatically asserts the byteenable signals to write data only to the specified slave byte lanes.

Slaves must have a data width of 8, 16, 32, 64, 128, 256, 512 or 1024 bits. Table 3–3 shows how slave data of various widths is aligned within a 32-bit master. In Table 3–3, OFFSET[N] refers to a slave word size offset into the slave address space.

| Mootor Puto                       | 32-Bit Master Data                                       |                                    |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------|------------------------------------|--|--|--|--|--|

| Master Byte<br>Address <i>(1)</i> | When Accessing a 16-Bit Slave Port                       | When Accessing a 64-Bit Slave Port |  |  |  |  |  |

| 0x00                              | OFFSET[1] <sub>15.0</sub> :OFFSET[0] <sub>15.0</sub> (2) | OFFSET[0] <sub>310</sub>           |  |  |  |  |  |

| 0x04                              | OFFSET[3] <sub>15.0</sub> :OFFSET[2] <sub>15.0</sub>     | OFFSET[0] <sub>6332</sub>          |  |  |  |  |  |

| 0x08                              | OFFSET[5] <sub>15.0</sub> :OFFSET[4] <sub>15.0</sub>     | OFFSET[1] <sub>310</sub>           |  |  |  |  |  |

| 0x0C                              | OFFSET[7] <sub>15.0</sub> :OFFSET[6] <sub>15.0</sub>     | OFFSET[1] <sub>6332</sub>          |  |  |  |  |  |

|                                   |                                                          |                                    |  |  |  |  |  |

Table 3-3. Dynamic Bus Sizing Master-to-Slave Address Mapping

#### Notes to Table 3-3:

- (1) Although the master is issuing byte addresses, it is accessing full 32-bit words.

- (2) For all slave entries, [<n>] is the word offset and the subscript values are the bits in the word.

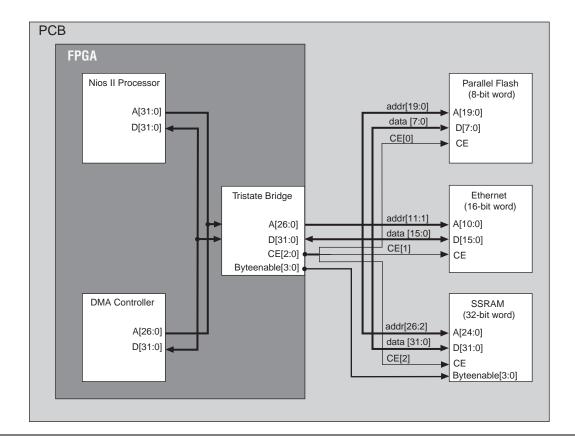

### 3.6.2. Avalon-MM Tri-State Slave Addressing

In contrast to Avalon-MM slaves which are accessed using the word size that the Avalon-MM slave defines, Avalon-MM tri-state slaves are accessed using byte addresses. Using byte addresses allows multiple slave devices with different word sizes to be connected to the same address pins of the FPGA. Figure 3–9 illustrates this point.

Figure 3-9. Connecting a Tristate Bridge to Components with Different Address Widths and Word Sizes

It is important to understand these differences in addressing to avoid costly respins of PCBs.

- Avalon-MM masters always drive word-aligned addresses that are aligned to the masters' own width. A 32-bit master port drives addresses aligned on 4-byte boundaries, such as: 0x00, 0x04, 0x08, 0x0c. Masters use the byteenable signal to access individual byte lanes.

- Avalon-MM slaves respond to word addresses as defined by the slave device. The word size must be a power of 2, between 2<sup>3</sup>–2<sup>10</sup>. The byteenable signals specify valid data when transfers occur between masters and slave with different word sizes. For example, the interface for an Avalon-MM slave device with 4, 64-bit locations would include 2 address bits, addr[1:0] and 8 byte enables, byteenable[7:0].

- Avalon-MM tri-state slaves are accessed using byte addresses. If an Avalon-MM master is accessing a 32-bit tri-state component, you should not connect the two least significant bits on the PCB. The third least significant bit connects to address[0] of the device.

In Figure 3–9, the Ethernet device has a 16-bit word size; however, because it is accessed through a tri-state bridge, the tri-state bridge issues a byte address. The left-shift from using address wires [10:0] to wires [11:1] occurs on the PCB.

### 3.6.3. Native Addressing

In versions of the SOPC Builder software before v8.0, a slave interface could specify that it had *native addressing*. When a master port addresses a slave port with the native address alignment property, all slave data is aligned on *native master* address boundaries. When a master port reads from a narrower slave port, the slave data bits map to the lower bits of the master data, and the upper master data bits are padded with zero. During write transfers, the upper bits are ignored. For example, if a 16-bit master port reads an 8-bit slave port, the readdata signal is of the form 0x00 < nn >, where < n > represents valid data, meaning that each word address as seen by each master addresses a different word on the slave. When a 32-bit master accesses a 64-bit slave, the upper 32 bits get coded to 0. Depending on how the slave handles the data, this coding could have negative side-effects.

With native addressing, the effective address map of the slave is dependent on the master that is accessing it, and in some cases, the address span of the slave changes as masters are added to the system. In many cases, extra logic is required to handle accesses from different masters, leading to increased logic usage and performance degradation.

Native addressing is now deprecated, meaning that it is still supported by the system interconnect fabric, but is not recommended for new components.

## 3.7. Masters

This section defines the behavior of Avalon-MM master transfers between a master and the system interconnect fabric as shown in Figure 3–10.

Figure 3-10. Focus of Avalon-MM Master Transfers

The signal types available for Avalon-MM masters allow you to create masters that use bursts for both reads and writes. Because the system interconnect fabric creates point-to-point connections between master and slave pairs, you can increase the throughput of your system by initiating reads with multiple pipelined slave peripherals. In responding to reads, when a slave peripheral has valid data it asserts readdatavalid and the system interconnect fabric enables the connection between the master and slave pair.

The following sections provide details of the signal types available for Avalon-MM masters and provide timing diagrams that detail these transfers.

## 3.8. Master Signal Types

Table 3–4 lists the signal types that constitute the Avalon-MM interface for master ports.

**Table 3–4.** Avalon-MM Master Signals (Part 1 of 3)

| Signal Type                | Width                                 | Direction | Req'd    | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------|---------------------------------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |                                       | Funda     | mental S | ignals                                                                                                                                                                                                                                                                                                                                                                                                                                |

| address                    | 1-32                                  | Out       | Yes      | The address signal represents a byte address regardless of the data-width of the master. The value of the address must be aligned to the data width. To write to specific bytes within a data word, the master must use the byteenable signal.                                                                                                                                                                                        |

|                            |                                       |           |          | Masters always issue byte addresses, regardless of the data width of the master or slave port. The system interconnect fabric translates this address into a word address in the slave's address space so that each slave access is for a word of data from the perspective of the slave.                                                                                                                                             |

| read<br>read n             | 1                                     | Out       | No       | Read request signal from the master. Not required if the master never performs read transfers.                                                                                                                                                                                                                                                                                                                                        |

|                            |                                       |           |          | If present, readdata must also be present.                                                                                                                                                                                                                                                                                                                                                                                            |