## MB86064

## Dual 14-bit 1GSa/s DAC

The Fujitsu MB86064 is a Dual 14-bit 1GSa/s digital to analog converter (DAC), delivering exceptional dynamic performance. Each high performance DAC core is capable of generating multi-standard, multi-carrier communication transmit signals, suitable for 2, 2.5 and 3G systems. DAC data is input via two high-speed LVDS ports. These operate in a pseudo double data rate (DDR) mode, with data latched on both rising and falling edges of the clock. Alternatively, the device can be configured as a multiplexed dual-port single DAC. To simplify system integration the DAC operates from a clock running at half the DAC conversion rate.

### Features

- Dual 14-bit, 1GSa/s Digital to Analog conversion

- Exceptional dynamic performance

- 74dBc ACLR for 4 UMTS carriers @ 276MHz direct-IF

- 100MHz image-free generated bandwidth capability

- supports UMTS plus digital pre-distortion bandwidth

- Proprietary performance enhancement features

- LVDS data interface

- Register selectable on-chip LVDS termination resistors

- Fujitsu 4-wire serial control interface

- Two 16k point programmable on-chip waveform memories

- Low power 3.3V analog and 1.8V digital operation

- 750mW single DAC operation power dissipation at 1GSa/s

- 0.18µm CMOS technology with Triple Well

- Performance enhanced EFBGA package

- Industrial temperature range operation (-40°C to +85°C)

## Applications

- Multi-carrier, Multi-standard cellular infrastructure

CDMA, W-CDMA, GSM/EDGE, UMTS

- Wideband communications systems

- High Direct-IF architectures

- Arbitrary waveform generation

- Test equipment

- Radar, video & display systems

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

Page 1 of 52

Disclaimer: The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

October 2004 Version 1.1 FME/MS/DAC80/DS/4972

# FUjITSU

MB86064 Dual 14-bit 1GSa/s DAC

## Contents

| 1 | Fun        | ctional Description                                   | . 4 |

|---|------------|-------------------------------------------------------|-----|

|   | 1.1        |                                                       |     |

|   |            | 1.1.1 Input Clock                                     |     |

|   |            | 1.1.2 DAC Core Clocks Programmable Delays             |     |

|   |            | 1.1.3 Waveform Memory Module Clock Programmable Delay |     |

|   |            | 1.1.4 Clock Outputs                                   |     |

|   |            | 1.1.5 Loop Clock                                      |     |

|   | 1.2        | DAC Data.                                             |     |

|   |            | 1.2.1 Data from the LVDS Interface                    |     |

|   |            | 1.2.2 Adjusting the Input Data Timing                 |     |

|   |            | 1.2.3 Data from the Waveform Memory Module            |     |

|   | 1.3        | DAC Core Current References                           |     |

|   | 1.4        | Voltage Reference                                     |     |

|   | 1.5        | Analog Output Reference Resistor                      |     |

|   | 1.6        | Analog Outputs                                        |     |

|   |            | 1.6.1 Frequency Planning                              |     |

|   | 1.7        | Reset and Power Down                                  | 16  |

| 2 | Sori       | al Control Interface                                  | 17  |

| 2 | 2.1        | Programming a Read/Write Cycle                        |     |

|   | 2.1        |                                                       | 17  |

| 3 | Wav        | eform Memory Module                                   | 20  |

|   | 3.1        | Dual Port, Interleaved LVDS Data via the WMM          |     |

|   | 3.2        | Waveform Memory Module Operation                      |     |

|   |            | 3.2.1 Waveform Memory Access via the Serial Interface |     |

|   |            | 3.2.2 Writing Data into the Memories.                 |     |

|   | 3.3        | Software Reset                                        | 27  |

|   |            |                                                       | ~~  |

| 4 |            | trical Characteristics                                |     |

|   | 4.1        | Absolute Maximum Ratings.                             |     |

|   | 4.2<br>4.3 | Digital Interface Specifications.                     |     |

|   | 4.3<br>4.4 | DC Specifications                                     | 29  |

|   | 4.4<br>4.5 | Dynamic Performance                                   |     |

|   | 4.5<br>4.6 | Clock Specifications.                                 |     |

|   | 4.0<br>4.7 | Serial Interface Timing Specifications                |     |

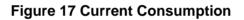

|   | 4.7        | Power Consumption                                     |     |

|   | 1.0        |                                                       | 00  |

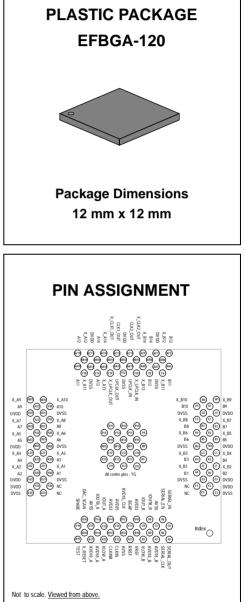

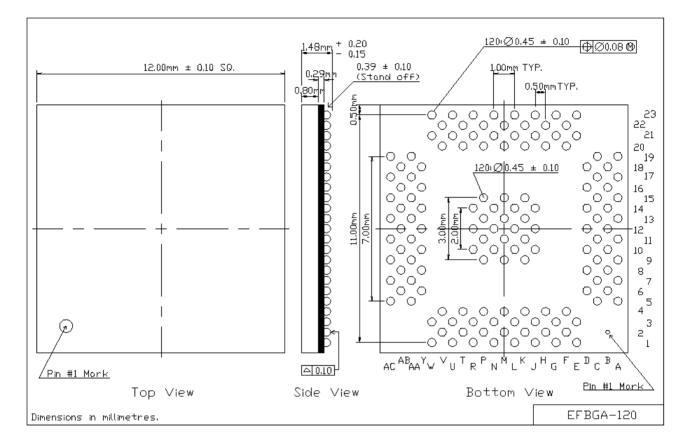

| 5 | Мес        | hanical Data                                          | 35  |

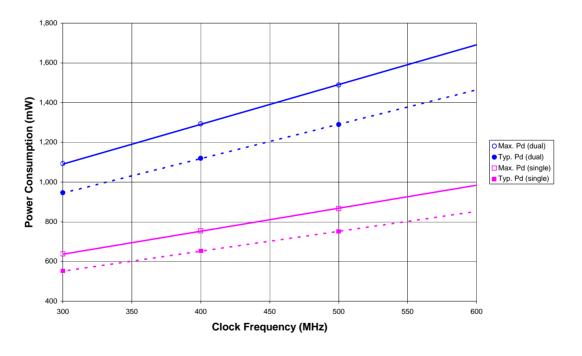

|   | 5.1        | Pin Assignment                                        |     |

|   | 5.2        | Pin Definition                                        |     |

|   | 5.3        | Package Data                                          | 39  |

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

## FUJITSU

|     | 5.4                      | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

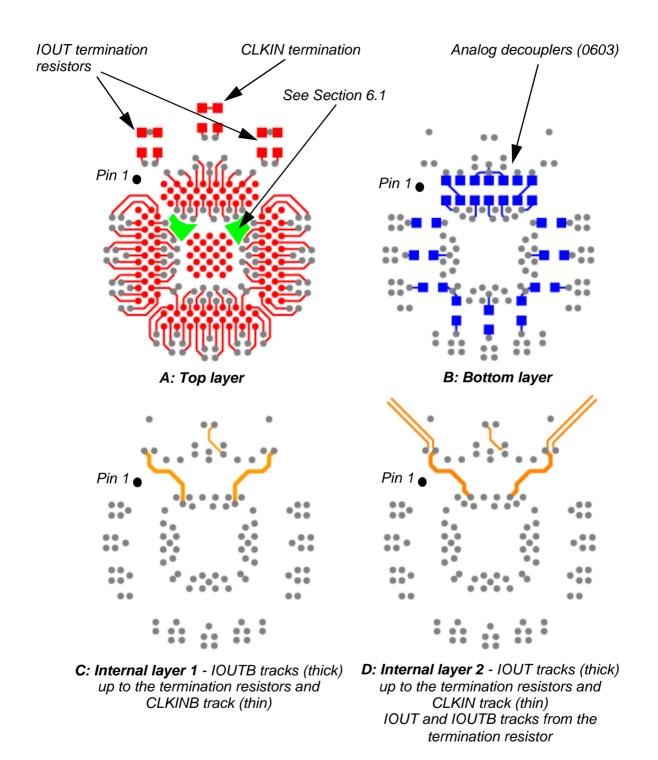

| 6   | 6.1<br>6.2<br>6.3<br>6.4 | lication Notes40PCB Power & Ground Plane Splits and Decoupling40Input Clock Interfacing42Clock Duty Cycle Optimisation43Analog Output Interfacing44Example Setup Register Settings456.5.1Dual DAC, LVDS data, Clock Outputs enabled456.5.2Single DAC, LVDS data port A, driving DAC A456.5.3Multiplexed LVDS data into DAC A (A=EVEN, B=ODD)456.5.4Waveform Memory Module, Different A & B Waveforms45Technical Support47 |

| 7   |                          | elopment Kit48Using DKUSB-1 in Target Applications49                                                                                                                                                                                                                                                                                                                                                                      |

| Арр | endix                    | A Default Register Settings50A.1DAC Core Registers50A.2Waveform Memory Module Registers51                                                                                                                                                                                                                                                                                                                                 |

CAUTION ELECTROSTATIC DISCHARGE SENSITIVE DEVICE

High electrostatic charges can accumulate in the human body and discharge without detection. Ensure proper ESD procedures are followed when handling this device.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

Page 3 of 52

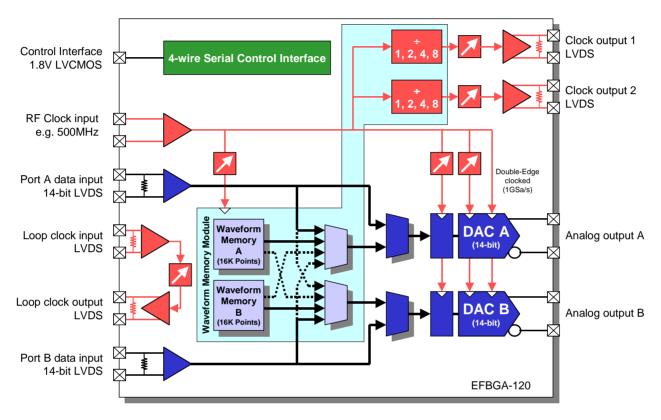

## **1** Functional Description

The MB86064 is a high performance Dual 14-bit 1GSa/s DAC. In addition to two DAC cores the device features a host of features designed to help both system integration and operation. A functional block diagram is shown in Figure 1.

Figure 1 MB86064 Functional Block Diagram

The device features a number of proprietary performance enhancement features. For example, analog performance at high frequencies is enhanced by novel current switch and switch driver designs which provide constant data-independent switching delay, reducing jitter and distortion. Each DAC core can be regarded as two interleaved DACs running at half rate. The main reason for adopting this approach is that the switch driver inherently includes a multiplex function through its two input ports. Compared to a conventional switch driver this allows twice as long to acquire and convert, though because the two paths share current sources they match exactly at low frequencies. In terms of input data, this approach allows easy interfacing to DDR data generating devices.

Also integrated into the device is a comprehensive Waveform Memory Module (WMM). Waveforms can be downloaded, via the serial control interface, to drive the DAC cores in the absence of a suitable external data generator.

Page 4 of 52

Disclaimer : The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

# FUĴITSU

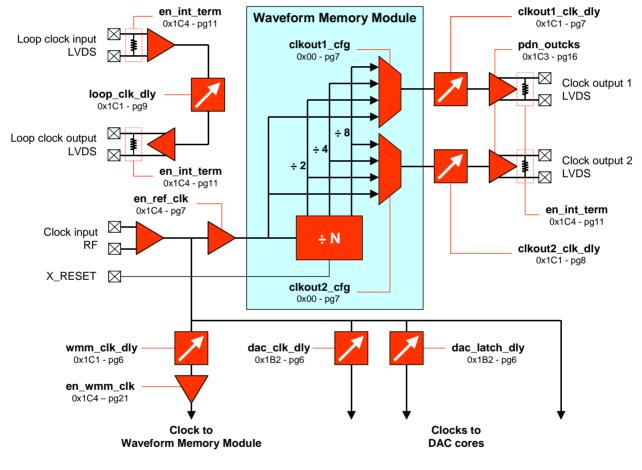

## 1.1 Clock

The device requires an input clock at half the DAC conversion rate, with sufficient spectral purity to not impact the target analog output performance. The DAC cores are clocked on both rising and falling edges of the input clock. This forms an effect of two interleaved converters in each DAC core. A characteristic of this architecture is a suppressed image of the generated signal, appearing reflected about Fs(dac)/4 = (Fclk-Fsig). Any duty cycle error in the input clock will exacerbate this image. This can be minimised by trimming the differential DC offset at the clock input pins.

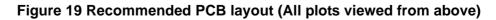

### 1.1.1 Input Clock

The input clock should be applied to the MB86064 through input pins CLKIN and CLKINB. The device is designed to accept a differential sinusoidal clock. Once on chip and converted to CMOS the clock is distributed to a number of blocks throughout the device. The DAC cores are supplied directly from the input clock buffer to ensure minimal degradation to the clock's purity.

Figure 2 Clock Distribution

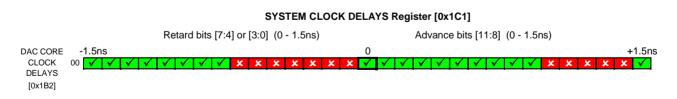

### 1.1.2 DAC Core Clocks Programmable Delays

The DAC core clocks contain programmable delays. These allow adjustment to the point at which data is clocked into the DAC core and when the analog portion of the DAC subsequently latches the

| Copyright $@$ 2004 Fujitsu Microelectronics Europe GmbH | Production | Page 5 of 52 |

|---------------------------------------------------------|------------|--------------|

|                                                         |            |              |

### MB86064 Dual 14-bit 1GSa/s DAC

data. The delay settings are programmed through register DAC CORE CLOCK DELAYS, bits *dac\_clk\_dly* and *dac\_latch\_dly*. Based on detailed evaluation by Fujitsu these registers should be programmed in accordance with the recommendations given in Table 1.

| Label       |   | Reg | Bits |     | DAC Core Digital Clock Delay |

|-------------|---|-----|------|-----|------------------------------|

| Labei       | 3 | 2   | 1    | 0   | (0 - 1.5ns, 100ps steps)     |

|             | 0 | 0   | 0    | 0   | Minimum (* Recommended *)    |

|             | : | :   | :    | ••• |                              |

| dac_clk_dly | 0 | 1   | 0    | 0   | Medium (default)             |

|             | : | :   | :    | ••• |                              |

|             | 1 | 1   | 1    | 1   | Maximum                      |

#### Table 1: DAC Core Register: DAC CORE CLOCK DELAYS [0x1B2]

| Label         |   | Reg | Bits |   | DAC Core Analog Latch Clock Delay |  |

|---------------|---|-----|------|---|-----------------------------------|--|

| Labei         | 7 | 6   | 5    | 4 | (0 - 1.5ns, 100ps steps)          |  |

|               | 0 | 0   | 0    | 0 | Minimum (* Recommended *)         |  |

|               | : | :   | :    | : |                                   |  |

| dac_latch_dly | 0 | 1   | 0    | 0 | Medium (default)                  |  |

|               | : | :   | :    | : |                                   |  |

|               | 1 | 1   | 1    | 1 | Maximum                           |  |

Note: **Bold** type indicates default setting. See Appendix A.

### **1.1.3 Waveform Memory Module Clock Programmable Delay**

A programmable delay stage is provided in the clock path prior to being applied to the Waveform Memory Module. This delay stage is programmed through register SYSTEM CLOCK DELAYS, bits *wmm\_clk\_dly*. See Table 2.

| Label       |    | Reg Bits |    |    | Waveform Memory Module Clock Delay |

|-------------|----|----------|----|----|------------------------------------|

| Laber       | 15 | 14       | 13 | 12 | (0 - 1.5ns, 100ps steps)           |

|             | 0  | 0        | 0  | 0  | Minimum (default & recommended)    |

| wmm_clk_dly | :  | :        | :  | :  |                                    |

|             | 1  | 1        | 1  | 1  | Maximum                            |

Page 6 of 52

Disclaimer : The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

#### 1.1.4 Clock Outputs

Two clock outputs, CLK1\_OUT and CLK2\_OUT, are provided to enable synchronisation of data generating devices to the DAC. The reference clock used by the Clock Output block can be disabled if required. See Table 3.

| Table 3: DAC Core Register: SYSTEM MISC [0x1C4] (Pai | t 1 of 3) |

|------------------------------------------------------|-----------|

|                                                      |           |

| SYSTEM MISC<br>(bit) | Label      | Function                                                       |  |  |

|----------------------|------------|----------------------------------------------------------------|--|--|

| 0                    | en_ref_clk | Reference clock control<br>0 = Enabled (default), 1 = Disabled |  |  |

The output frequency can be individually selected as the input clock divided-by-1, 2, 4 or 8. Configuration is through register WMM CONFIG, bits *clkout1\_cfg* and *clkout2\_cfg*. See Table 4.

| Label        |   | Reg | Bits |   |                                           |

|--------------|---|-----|------|---|-------------------------------------------|

| Label        | 3 | 2   | 1    | 0 | Divided Clock Output Configuration        |

|              |   |     | 0    | 0 | Clock output 1 = clock input (default)    |

| alleaute afe |   |     | 0    | 1 | Clock output 1 = clock input divided by 2 |

| clkout1_cfg  |   |     | 1    | 0 | Clock output 1 = clock input divided by 4 |

|              |   |     | 1    | 1 | Clock output 1 = clock input divided by 8 |

|              | 0 | 0   |      |   | Clock output 2 = clock input (default)    |

| alkout2 of a | 0 | 1   |      |   | Clock output 2 = clock input divided by 2 |

| clkout2_cfg  | 1 | 0   |      |   | Clock output 2 = clock input divided by 4 |

|              | 1 | 1   |      |   | Clock output 2 = clock input divided by 8 |

#### Table 4: Waveform Memory Module Register: WMM CONFIG [0x00] (Part 1 of 2)

Also, programmable delay stages are provided in both CLK1\_OUT and CLK2\_OUT outputs. These clock output delays are programmed through register SYSTEM CLOCK DELAYS *clkout1\_clk\_dly* and *clkout2\_clk\_dly*. See Table 5 and Table 6.

| Table 5. DAC Core Register  | SVSTEM CLOCK DEL AVS | $\left[0 \times 1 C 1\right] \left( \text{Part 2 of } 4 \right)$ |

|-----------------------------|----------------------|------------------------------------------------------------------|

| Table 5: DAC Core Register: | SISTEN CLUCK DELATS  | [UXICI] (Fait 2 01 4)                                            |

| Label           |   | Reg | Bits |   | <b>Clock Output Delay</b><br>(0 - 1.5ns, 100ps steps) |

|-----------------|---|-----|------|---|-------------------------------------------------------|

| Laber           | 7 | 6   | 5    | 4 |                                                       |

|                 | 0 | 0   | 0    | 0 | Minimum (default)                                     |

| clkout1_clk_dly | : | :   | :    | : |                                                       |

|                 | 1 | 1   | 1    | 1 | Maximum                                               |

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

MB86064 Dual 14-bit 1GSa/s DAC

#### Table 6: DAC Core Register: SYSTEM CLOCK DELAYS [0x1C1] (Part 3 of 4)

| Label           | Reg Bits |   |   |   | Clock Output Delay       |

|-----------------|----------|---|---|---|--------------------------|

| Laber           | 3        | 2 | 1 |   | (0 - 1.5ns, 100ps steps) |

|                 | 0        | 0 | 0 | 0 | Minimum (default)        |

| clkout2_clk_dly | :        | : | : | : |                          |

|                 | 1        | 1 | 1 | 1 | Maximum                  |

The clock outputs are designed to drive a doubly-terminated LVDS line (7mA drive into a bridged 50 $\Omega$  load) for the best possible signal integrity. 100 $\Omega$  termination resistors should be connected across the Q and Q signals at each end of the differential line. Enabling the internal LVDS terminations provides the required source termination on-chip.

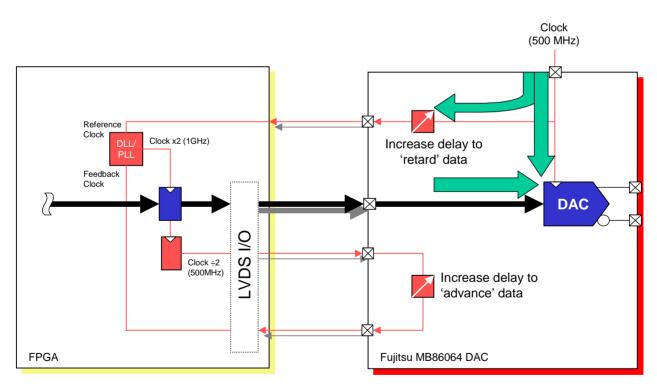

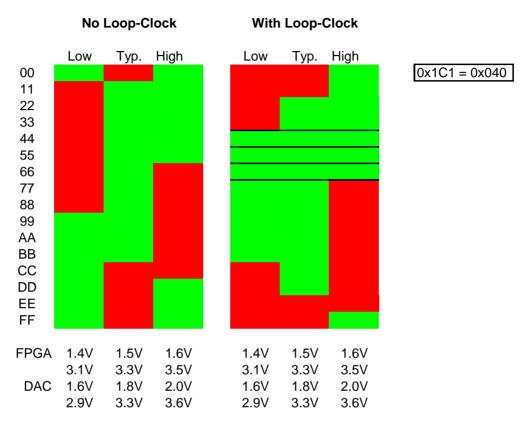

#### 1.1.5 Loop Clock

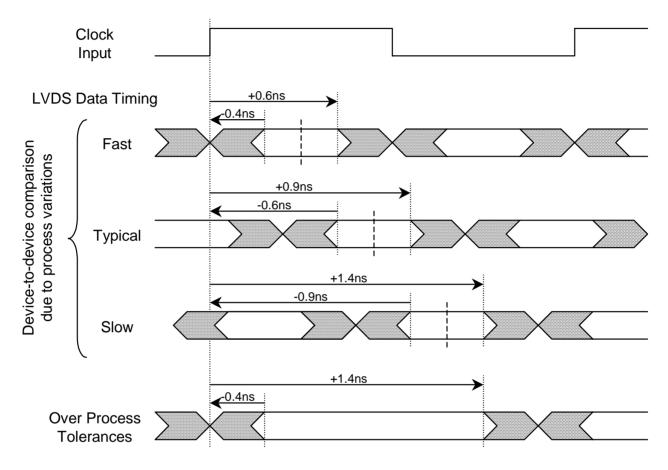

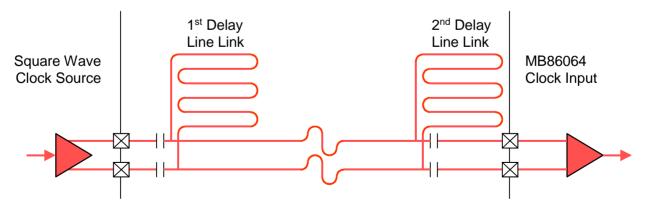

Maintaining valid clock-to-data timing becomes increasingly difficult at higher clock rates, particularly over tolerance with device-to-device variations. The MB86064 minimises potential problems through its DDR data interface and by providing a unique loop-clock facility.

Figure 3 Loop Clock Implementation

The on-chip 'loop' consists of an LVDS input buffer connected to an LVDS output buffer through a programmable delay stage. This loop-through, and the associated tracking from/to the data

generating device, can be incorporated in the feedback loop of a Delay-Locked Loop (DLL) or Phase-Locked Loop (PLL) clock generator, within the generating device. This enables the system to compensate for variations in input/output (I/O) and propagation delays in both the data generating device and the DAC. PCB and/or cable propagation delays within the loop are also compensated for but these are not expected to exhibit significant variation between systems. It is the I/O & on-chip delays that will dominate.

It is important to make sure that the Clock Output frequency is within the specification of the DLL/PLL. If it is too high an appropriate divided clock output should be programmed as detailed in Table 7.

With the loop clock implemented as illustrated in Figure 3, increasing the Clock Output delay delays the data arriving at the DAC relative to the DAC input clock. By contrast increasing the Loop Clock delay, within the feedback loop of the DLL/PLL, advances the relative timing.

It is important not to adjust both delays simultaneously else they will counteract each other. Either the Clock Output delay or the Loop Clock delay, or both, should be zero.

Connections to the loop clock are via pins LPCLK\_IN and LPCLK\_OUT. The loop clock delay is programmed through register SYSTEM CLOCK DELAYS, *loop\_clk\_dly*. See Table 7.

| Label        | Reg Bits |    |   |                            | Loop Clock Delay  |

|--------------|----------|----|---|----------------------------|-------------------|

| Laber        | 11       | 10 | 9 | 8 (0 - 1.5ns, 100ps steps) |                   |

|              | 0        | 0  | 0 | 0                          | Minimum (default) |

| loop_clk_dly | :        | :  | : | :                          |                   |

|              | 1        | 1  | 1 | 1                          | Maximum           |

Table 7: DAC Core Register: SYSTEM CLOCK DELAYS [0x1C1] (Part 4 of 4)

Assuming the DAC Core Clock Delays have been set to their recommended value (0x00), adjustment of the Clock Output and Loop Clock delays produces a diagram where valid & invalid data latching points can be identified. This is illustrated in Figure 4.

#### Figure 4 Data Eye Adjustment Using Loop Clock

The results in Figure 4 are unique to the particular test setup. This example used an Altera Stratix FPGA evaluation platform driving a Fujitsu development kit at 800MSa/s. Another circuit

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

#### MB86064 Dual 14-bit 1GSa/s DAC

implementation would be expected to exhibit different absolute timings but similar relative adjustments.

#### Figure 5 Maintaining Valid Clock-to-Data Timing using Look Clock

Having evaluated a prototype design and final clock delay settings chosen, the real benefit of using the loop clock facility is in maintaining valid clock-to-data timing at these settings. Figure 5 illustrates this in operation by using excessive variation in supply voltages to emulate both fast and slow FPGA and DAC components being used together in production.

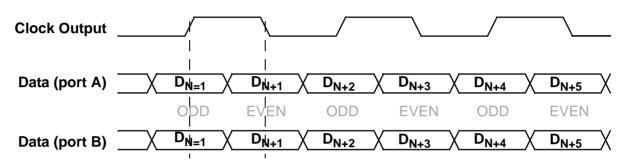

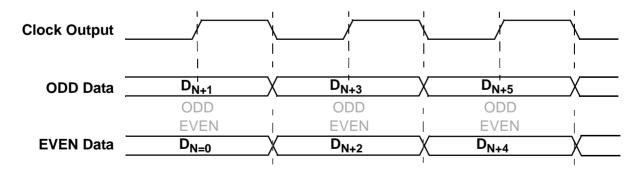

## 1.2 DAC Data

Each DAC core can be considered as two identical halves, referred to as ODD and EVEN. EVEN samples are latched on the falling edge of Clock Output, whilst ODD samples are latched on the rising edge.

٩

Data should be presented to the DAC cores as unsigned binary, 14-bit data. Bit 14 is the MSB, and bit 1 is the LSB.

Figure 6 ODD and EVEN Data Sampling

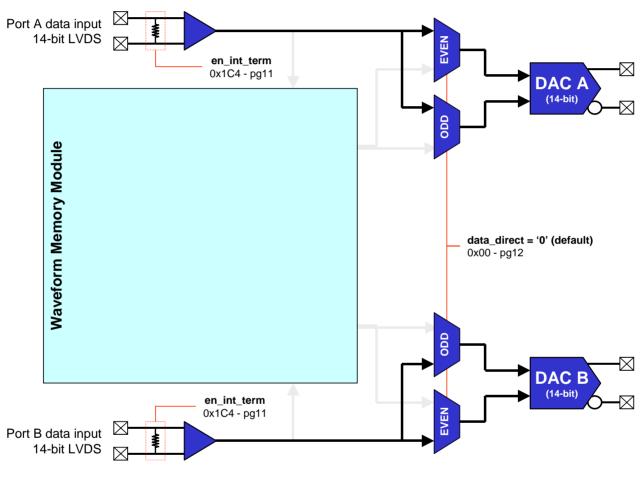

Data can be supplied to the DAC cores either externally via the LVDS data bus or internally from the Waveform Memory Module.

### 1.2.1 Data from the LVDS Interface

External data is input to the MB86064 through LVDS data ports A (pins A[14:1]) and B (pins B[14:1]). On-chip 100 $\Omega$  termination resistors are provided to reduce the external component count, selectable through register SYSTEM MISC *en\_int\_term*. See Table 8 on page 11.

| SYSTEM MISC<br>(bit) | Label | Function                                                                                                                                                                                   |

|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                    |       | Internal 100R LVDS termination enable (All LVDS data inputs, loop<br>clock input, loop clock output and reference clock outputs)<br>0 = Disabled, <b>1 = Termination enabled (default)</b> |

Table 8: DAC Core Register: SYSTEM MISC [0x1C4] (Part 2 of 3)

The data may be routed to the DAC cores through a number of paths. The most direct path routes data straight from the LVDS input buffers to the DAC core input latches. This is the default configuration, with the DAC input multiplexers set to accept data from the LVDS inputs according to register WMM CONFIG, *data\_direct*. See Table 9 below.

The DAC exhibits a pipeline delay through the device of 18 input clock edges.

#### Table 9: Waveform Memory Module Register: WMM CONFIG [0x00] (Part 2 of 2)

| WMM CONFIG<br>(bit) | Label       | Function                                                                                            |

|---------------------|-------------|-----------------------------------------------------------------------------------------------------|

| 4                   | data direct | DAC A and DAC B data source<br><b>0 = LVDS data directly (default)</b> , 1 = Waveform Memory Module |

Figure 7 Direct Data Routing from the LVDS Interface

### 1.2.2 Adjusting the Input Data Timing

When using the Clock Outputs to synchronise the data generator it is possible to adjust the relative input data timing through DAC Core register SYSTEM CLOCK DELAYS [7:4] & [3:0], *clkout1\_clk\_dly* & *clkout2\_clk\_dly*. See Table 5 and Table 6. Increasing this setting delays the arrival of input data.

Page 12 of 52

#### Production

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

When using the Loop Clock, the delay set by *loop\_clk\_dly* (Table 7) opposes this and effectively advances the input data relative to the reference clock edge. Together these adjustments provide approximately 3ns trim range for clock-to-data timing, in 100ps steps.

#### Figure 8 LVDS Input Data Timing

For further details refer to sections 1.1.4 and 1.1.5.

#### **1.2.3** Data from the Waveform Memory Module

Data routing within the Waveform Memory Module is flexible enough to allow A and B data to be interleaved onto a single DAC core. However, primarily the Waveform Memory Module is intended to be loaded with waveforms and subsequently read back to drive the DAC cores. A complete description of how to use the Waveform Memory Module is given in Section 3.

### **1.3 DAC Core Current References**

Internal current references are required to be configured according to which DAC core(s) are enabled. These are controlled by the DAC Core Register DAC CONFIG.

```

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

```

Production

|   | CONFIG<br>its) | Configuration                          |

|---|----------------|----------------------------------------|

| 1 | 0              |                                        |

| Х | Х              | With DAC A and DAC B disabled          |

| 1 | Х              | With DAC A enabled, DAC B disabled     |

| Х | 1              | With DAC A disabled, DAC B enabled     |

| 0 | 0              | With DAC A and DAC B enabled (default) |

#### Table 10: DAC Core Register: DAC CONFIG [0x1C0]

The appropriate setting of these bits is dependent on the power-down status of the DAC cores, determined by register POWER DOWN [0x1C3] bits *pdn\_daca* and *pdn\_dacb*.

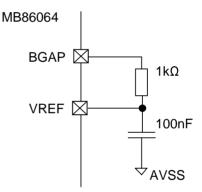

## 1.4 Voltage Reference

A 1.2V bandgap reference is provided on-chip, although this is left unconnected when an external reference is to be used. To use the internal bandgap reference, pins BGAP and VREF should be linked via a  $1k\Omega$  resistor. VREF should be decoupled to AVSS with a 100nF capacitor.

For maximum absolute accuracy an external voltage reference should be used. This should be connected to VREF through a  $1k\Omega$  resistor and decoupled as described above. The external voltage reference should be powered from the AVD25 pin, which is a regulated 2.5V output with high power supply noise rejection.

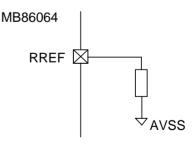

## 1.5 Analog Output Reference Resistor

From the voltage reference the full scale analog output current is defined by an external reference resistor,  $R_{ref}$ , where,

$$R_{ref} \approx \frac{16 \times V_{ref}}{I_{OP}}$$

e.g. With Vref = 1.20V, to give a 20mA full scale output, Rref = 960 $\Omega$ . Designs that for simplicity use a 1k $\Omega$  resistor will result in a marginally lower full scale output current of 19.2mA (-0.35dB) unless using an external reference to provide a higher voltage of 1.25V.

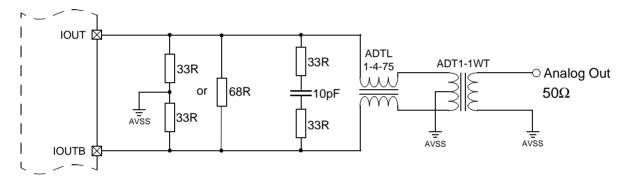

## 1.6 Analog Outputs

The DAC outputs are differential current type. A termination resistor, or load, should be used appropriate for the recommended output swing. Each DAC may be individually powered down.

```

Page 14 of 52

```

#### Production

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Disclaimer : The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

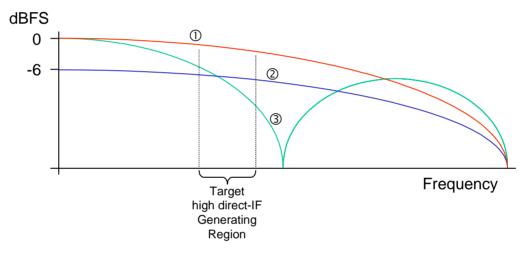

Analog output performance benefits from the chosen DAC core architecture, identified in Section 1 as similar to two interleaved DACs running at half rate. The big advantage of this approach compared to a single DAC running at half the rate is much reduced sinx/x roll-off which gives increased output power and better in-band flatness when generating high output frequencies (e.g. 200MHz and above). This is illustrated in Figure 9 as line 1. An alternative approach using a return-to-zero output stage admittedly has the same sinx/x roll off (and switch driver speed) but 6dB lower output power and a large image at Fclk-Fout. See Line 2. For reference, line 3 illustrates a conventional DAC running at half rate.

Another aspect of this comparison which should not be overlooked concerns noise performance, increasingly quoted in units of dBm/Hz. In terms of SNR there is some 7dBs of degradation to consider when comparing a 300MHz test for a standard 400MSa/s DAC with the MB86064 running at 800MSa/s. This is relevant to the Noise floor figures quoted in section 4.5 Dynamic Performance.

Figure 9 Benefits of DAC core Architecture to Sinx/x Response

### 1.6.1 Frequency Planning

Systems that require superior dynamic performance should not ignore the DAC from the task of frequency planning. To do so could result in impractical specifications or at worst increase the cost and power of the converter that would need to be selected. The MB86064 is designed to deliver the very best dynamic performance across wide bandwidths, as required for communications systems and in particular for multi-carrier applications. Preferred generating bands can be demonstrated as those centred at 0.2, 0.3 and 0.4 Fdac. In addition, while allowing certain images in-band though at levels unlikely to impact on performance other possible centre frequencies are 0.125 and 0.375 Fdac.

It is important to remember that conventional DACs running at half the rate or those incorporating a return-to-zero output stage are subject to exactly the same frequency planning constraints as these are defined by Nyquist's theorem. However, a key advantage of the MB86064 is its ability to generate wide bandwidth signals in the 2nd Nyquist zone where conventional DACs will be prevented from doing so due to Sinx/x attenuation.

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

## 1.7 Reset and Power Down

Pin X\_RESET is the device reset pin. On the falling edge of X\_RESET the device is reset and all registers are set to their default values. After a reset most parts of the device are powered down. See Table 11, DAC Core Register POWER DOWN. Power to each internal block may be individually controlled through this register.

| POWER DOWN<br>(bit) | Label         | Function                                                                                          |                     |

|---------------------|---------------|---------------------------------------------------------------------------------------------------|---------------------|

| 0                   | pdn_reglo     | Low voltage (~1.1V) regulator control<br><b>0 = Enabled (default)</b> , 1 = Powered down          |                     |

| 1                   | pdn_regck     | 1.8V clock regulator control<br><b>0 = Enabled (default)</b> , 1 = Powered down                   |                     |

| 2                   | pdn_reg18     | 1.8V DAC regulator control<br><b>0 = Enabled (default)</b> , 1 = Powered down                     |                     |

| 3                   | pdn_reg25     | 2.5V bandgap regulator control<br><b>0 = Enabled (default)</b> , 1 = Powered down                 |                     |

| 4                   | pdn_ckandrefs | DAC common circuit (clocks, references and bia<br>0 = All enabled (default), 1 = All powered down |                     |

| 5                   | pdn_outcks    | Divided output clocks<br><b>0 = Enabled (default)</b> , 1 = Powered down                          |                     |

| 6                   | pdn_loopcks   | Loop clocks<br>0 = Enabled, <b>1 = Powered down (default)</b>                                     |                     |

| 7                   | pdn_odatb     | Access to TEST output pin by DAC B<br>0 = Enabled, <b>1 = Disabled (default)</b>                  |                     |

| 8                   | pdn_odata     | Access to TEST output pin by DAC A<br>0 = Enabled, <b>1 = Disabled (default)</b>                  |                     |

| 9                   | pdn_indatb    | DAC B data input power down control<br>0 = Enabled, <b>1 = Powered down (default)</b>             |                     |

| 10                  | pdn_indata    | DAC A data input power down control<br>0 = Enabled, <b>1 = Powered down (default)</b>             |                     |

| 11                  | pdn_dacb      | DAC B control<br>0 = Enabled, <b>1 = Powered down (default)</b>                                   | N.B. See note below |

| 12                  | pdn_daca      | DAC A control<br>0 = Enabled, <b>1 = Powered down (default)</b>                                   | N.B. See note below |

Table 11: DAC Core Register: POWER DOWN [0x1C3]

The DAC control register bits, *pdn\_daca* & *pdn\_dacb*, must be set in conjunction with the DAC CONFIG register bits to ensure the correct internal reference current is used. See section 1.3.

Examples of typical settings are:

- 0x0000B80 DAC A enabled for LVDS data

- 0x0001580 DAC B enabled for LVDS data

- 0x0000180 Both DACs enabled for LVDS data

All are based on both the divided clock outputs and loop-clocks being enabled.

```

Page 16 of 52

```

Disclaimer : The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

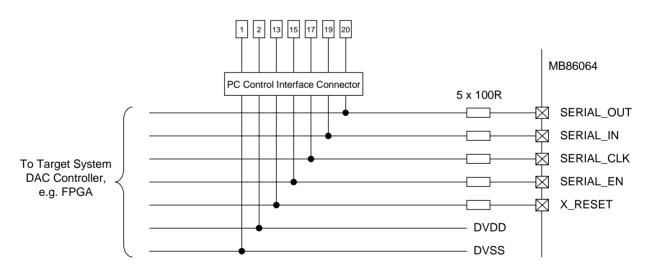

## 2 Serial Control Interface

A simple 4-wire serial control interface is used to control the MB86064. The serial interface uses pins SERIAL\_IN, SERIAL\_OUT, SERIAL\_CLK and SERIAL\_EN. Programmed settings are stored in a number of registers which are individually accessible using either an 7-bit (WMM Registers) or 10-bit (DAC Core Registers) address/control word. Data may be written to or read from each of these registers.

The serial interface uses 1.8V LV-CMOS logic levels.

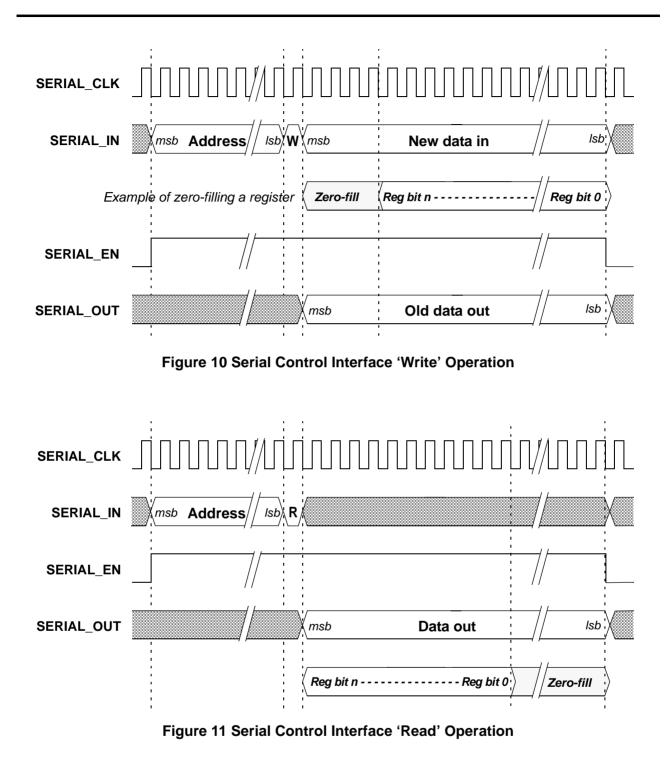

## 2.1 **Programming a Read/Write Cycle**

To perform a read or write cycle SERIAL\_EN should be taken high on the falling edge of SERIAL\_CLK. This will indicate the start of a frame when latched on the next rising edge. At the same time SERIAL\_IN should be driven, MSB first, with the address of the register to be accessed. Data is latched into the device on each rising edge of SERIAL\_CLK. The register address should be followed with the read/write instruction bit. For a read cycle this bit is '0', for a write cycle this bit is '1'. The device is now ready to transfer data in or out of the addressed register.

If the selected register is to be written to, the data should be presented to SERIAL\_IN, MSB first. The data packet only needs to be as long as the register that is being written to, with the LSB presented in the final time slot. If the data source has a fixed length packet size, longer than the register, the data packet should be zero-filled at the MSB end. Once the data has been transferred into the register, SERIAL\_EN should be taken low on the falling edge of SERIAL\_CLK to indicate the end of the read/write cycle and frame. During a write cycle, as data is loaded into the selected register, the previous contents are output on SERIAL\_OUT, MSB first.

If the selected register is being read, data will be output on SERIAL\_OUT, MSB first, nominally coincident with the falling edge of SERIAL\_CLK. Once the register has been read additional clock cycles will produce zero-filled bits until the read cycle is terminated. A read cycle may be terminated by taking the SERIAL\_EN low on the falling edge of SERIAL\_CLK.

All Waveform Memory Module registers, apart from WMM [EVEN/ODD] RAM DATA, read back as eight bit long registers. All other registers will read back at their true length.

Figure 10 and Figure 11 show the write and read cycles (as functional timing diagrams) in more detail.

In designs where SERIAL\_CLK is halted after a Write operation, at least three additional clock cycles should be allowed after SERIAL\_EN has return low. This is necessary to complete the internal register programming.

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

Disclaimer: The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

MB86064 Dual 14-bit 1GSa/s DAC

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

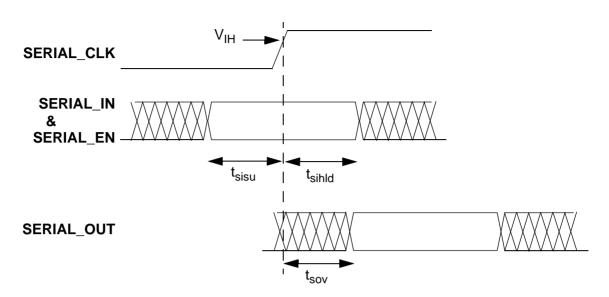

Figure 12 Serial Control Interface Timing Requirements

For initial testing & evaluation it is assumed that customers will use the Fujitsu PC USB Programming cable and software, both with the product development kit and for initial target application debug. See Section 7 for further information.

**5U**

## 3 Waveform Memory Module

Enabling the Waveform Memory Module allows interleaving of the LVDS data to drive a single DAC core as well as access to any downloaded waveforms. The on-chip waveform memories allow the DAC cores to be exercised with user programmable waveforms without the need for an external high speed pattern generator. The memories are physically implemented using four 2k x 64-bit static RAMs, assigned as two per DAC for ODD and EVEN samples. The memories can be configured to drive two different waveforms of equal length, up to 16k points each, to be routed to DAC A and DAC B independently. Alternatively, it is possible to download multiple waveforms, totalling 16k points or less, to be selected as required. This last configuration takes advantage of the ability to specify the waveform start address and length.

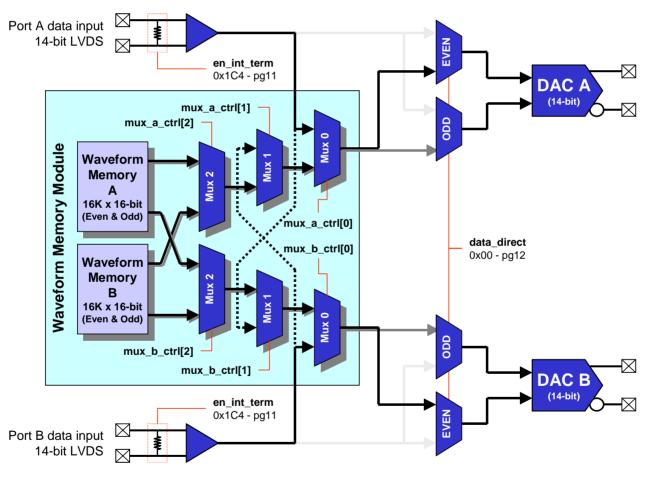

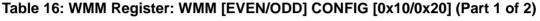

Data routing within the Waveform Memory Module is determined by three cascaded multiplexers, mux\_[a/b/c]\_ctrl[0:2], as illustrated in Figure 13.

Figure 13 Waveform Memory Module Data Routing

Page 20 of 52

Production

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

FUĴITSU

The data multiplexers are controlled by the WMM Registers, WMM [EVEN/ODD] MUX CTRL. Setting of these registers is referred to in the following two sections.

| WMM [EVEN/<br>ODD] MUX CTRL<br>(bit) | Label         | Function                                                                                                                                     |

|--------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                    | mux_a_ctrl[0] | Mux 0 control bit<br><b>0 = Data from LVDS input port A (default)</b><br>1 = Data from Mux 1                                                 |

| 1                                    | mux_a_ctrl[1] | Mux 1 control bit<br><b>0 = Data from LVDS input port B (default)</b><br>1 = Data from Mux 2                                                 |

| 2                                    | mux_a_ctrl[2] | Mux 2 control bit (1). See also mux_a_ctrl[3] setting.<br>0 = Data from RAM A - 16K points mode (default)<br>1 = not used                    |

| 3                                    | mux_a_ctrl[3] | Mux 2 control bit (2)<br><b>0 = mux_a_ctrl[2] operates as normal (default)</b><br>1 = When mux_a_ctrl[2] = 0, RAM B is used instead of RAM A |

| 4                                    | mux_b_ctrl[0] | Mux 0 control bit<br><b>0 = Data from LVDS input port B (default)</b><br>1 = Data from Mux 1                                                 |

| 5                                    | mux_b_ctrl[1] | Mux 1 control bit<br><b>0 = Data from LVDS input port A (default)</b><br>1 = Data from Mux 2                                                 |

| 6                                    | mux_b_ctrl[2] | Mux 2 control bit (1). See also mux_b_ctrl[3] setting.<br>0 = Data from RAM B - 16k points mode (default)<br>1 = not used                    |

| 7                                    | mux_b_ctrl[3] | Mux 2 control bit (2)<br><b>0 = mux_b_ctrl[2] operates as normal (default)</b><br>1 = When mux_b_ctrl[2] = 0, RAM A is used instead of RAM B |

| Table 12: Waveform Memory Mo | odulo Rogistor: WMM [EVEN     |  |

|------------------------------|-------------------------------|--|

|                              | ouule ivegister. wivini [LvLi |  |

To use any of the Waveform Memory Module modes it is necessary to first enable the module's clock through register SYSTEM MISC, bit *en\_wmm\_clk* (see Table 13).

#### Table 13: DAC Core Register: SYSTEM MISC [0x1C4] (Part 3 of 3)

| SYSTEM MISC<br>(bit) | Label      | Function                                                                           |

|----------------------|------------|------------------------------------------------------------------------------------|

| 1                    | en wmm cik | Waveform Memory Module clock control<br>0 = Enabled, <b>1 = Disabled (default)</b> |

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

## 3.1 Dual Port, Interleaved LVDS Data via the WMM

By routing the external LVDS data through the Waveform Memory Module it is possible to interleave A and B data into one of the DAC cores. To configure the device in this mode EVEN & ODD multiplexers need to be set differently.

| WMM EVEN MUX CTRL<br>[0x11] | WMM ODD MUX CTRL<br>[0x21] | DA          | C A          |

|-----------------------------|----------------------------|-------------|--------------|

| mux_a_ctrl[0]<br>(bit 0)    | mux_a_ctrl[0]<br>(bit 0)   | ODD data in | EVEN data in |

| '1'                         | '0' (default)              | Port A      | Port B       |

| '0' (default)               | '1'                        | Port B      | Port A       |

#### Table 14: Configuration for Interleaved Data to DAC A

#### Table 15: Configuration for Interleaved Data to DAC B

| WMM EVEN MUX CTRL<br>[0x11] | WMM ODD MUX CTRL<br>[0x21] | DA          | СВ           |

|-----------------------------|----------------------------|-------------|--------------|

| mux_b_ctrl[0]<br>(bit 4)    | mux_a_ctrl[0]<br>(bit 4)   | ODD data in | EVEN data in |

| '1'                         | '0' (default)              | Port B      | Port A       |

| '0' (default)               | '1'                        | Port A      | Port B       |

Remember to set register WMM CONFIG [0x00] bit *data\_direct* to '1' (see Table 9)

The DAC will now sample alternate input ports, for consecutive DAC samples, as the EVEN and ODD routing through the Waveform Memory Module is not the same.

#### Figure 14 Interleaved Mode ODD and EVEN Data Sampling

Page 22 of 52

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

## 3.2 Waveform Memory Module Operation

To make full use of the Waveform Memory Module user waveforms may be downloaded to the onchip memories. Different waveforms of equal length may be stored in each RAM, totalling up to 16k points (in multiples of eight points). Configuration of the WMM [EVEN/ODD] MUX CTRL registers will determine which vector is routed to which DAC.

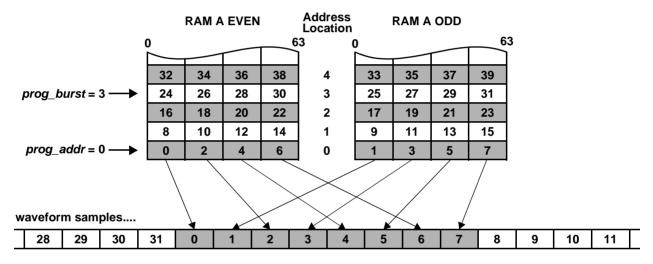

Before the waveform memories can be used they must be enabled through register WMM [EVEN/ODD] CONFIG, bit *ram\_ih*. See Table 16.

| WMM [EVEN/<br>ODD] CONFIG<br>(bit) | Label  | Function                                                                                   |

|------------------------------------|--------|--------------------------------------------------------------------------------------------|

| 1                                  | ram_ih | Waveform Memory inhibit control<br>0 = Memories Enabled<br>1 = Memories Disabled (default) |

#### Figure 15 Waveform Memories Routing Diagram

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

*ODD* and *EVEN* RAM elements within the module allow data to be routed to the ODD and EVEN phase DAC core data latches, similar to when data is input via the LVDS data interface and double edge clocking is used. As an example, to route data from RAM A to DAC A, and RAM B to DAC B,

• set register WMM [EVEN/ODD] MUX CTRL bits *mux\_a\_ctrl[1]* & [0] and *mux\_b\_ctrl[1]* & [0]. Both the EVEN and ODD registers should be set the same. All other bits should be set to their default value.

To swap these data paths,

• set register WMM [EVEN/ODD] MUX CTRL bits *mux\_a\_ctrl[3]* and *mux\_b\_ctrl[3]*. Both the EVEN and ODD registers should be set the same.

#### 3.2.1 Waveform Memory Access via the Serial Interface

To access the waveform memories the RAM Access Controllers must first be configured. The RAM Access Controllers are configured through registers WMM [EVEN/ODD] RAM CTRL. See Table 17.

| WMM [EVEN/<br>ODD] RAM CTRL<br>(bits) | Label       | Function                                                                                                                                         |

|---------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| [10:0]                                | prog_addr   | RAM access start address                                                                                                                         |

| [21:11]                               | prog_burst  | RAM access burst size<br>Access burst size should be programmed as ((No. of points/8) - 1)<br>A value of zero indicates a single word access     |

| 22                                    | prog_rw     | RAM serial interface access mode<br><b>0 = Read mode (default)</b><br>1 = Write mode                                                             |

| 23                                    | prog_sel(1) | RAM write select (1). <b>Dependent on prog_sel(2) setting</b><br><b>0 = Write data to RAM A (default)</b><br>1 = Write data to RAM B             |

| 24                                    | prog_sel(2) | RAM write select (2)<br><b>0 = prog_sel(1) operates as normal (default)</b><br>1 = Writes the same data to both RAM A and RAM B                  |

| 25                                    | prog_start  | RAM Access Controller control<br><b>0 = Cycle through vector address range (default)</b><br>1 = Program RAMs<br><i>This bit is self clearing</i> |

#### Table 17: Waveform Memory Module Registers: WMM [EVEN/ODD] RAM CTRL [0x12/0x22]

When programming the WMM on-chip memories ensure that the Clock Input ( $f_{Clk}$ ) is greater than 16 times the serial interface clock frequency ( $f_{sclk}$ ) for correct operation.

Page 24 of 52

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

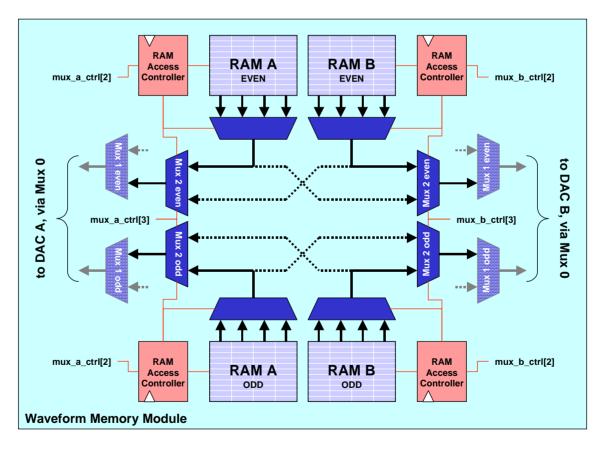

The WMM [EVEN/ODD] RAM CTRL registers *prog\_addr* fields are used to define the start address of the waveform. These fields should be set to 0 in order to store a full 16k point waveform. For the multiple waveform mode, the number entered into these fields is the start location within the 2k x 64-bit ODD/EVEN RAM element that the waveform is to be stored. One address location in this field translates to eight waveform vector points because four points are stored at each address of the ODD and EVEN RAM blocks.

The WMM [EVEN/ODD] RAM CTRL registers *prog\_burst* fields sets the length of the stored waveform, defined as the number of waveform points divided by eight, minus one. Every RAM address in each of the ODD, EVEN, RAM A and RAM B memories corresponds to a 64-bit location. Each location is divided into four 16-bit samples.

Figure 16 shows an example of how a 32 point vector is stored. In this example  $prog_addr$  is set to 0 and  $prog_burst = 3$ .

Figure 16 Waveform Vector Storage in on-chip Memories

*prog\_addr* and *prog\_burst* must be the same for RAM A and RAM B when routing data to the DACs.

Register bit *prog\_rw* is used to select between reading from and writing to the RAMs through the serial interface. This bit should be set to '1' to write data into the RAMs, but does not need to be cleared to route data out to the DACs. Bit *prog\_rw* only needs to be cleared if data in the RAMs is to be read out through the serial interface.

Register bit *prog\_sel(1)* selects between RAM A and RAM B when data is being written or read via the serial interface. This bit has no function when data is being read out to the DACs. Register bit *prog\_sel(2)* allows the data to be written to both RAM A and RAM B simultaneously.

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Register bit *prog\_start* is used to indicate the start of a write cycle to the RAMs. This bit is self clearing. See section 3.2.2 for details of the write cycle.

### 3.2.2 Writing Data into the Memories

The process of writing data into the RAMs is controlled by the RAM Access Controllers, which expect data to be presented through the serial interface in a set sequence through the WMM [EVEN/ODD] RAM DATA registers.

The RAM Access Controllers will expect to receive the number of RAM data words specified in the register WMM [EVEN/ODD] RAM CTRL *prog\_burst* field. If additional RAM data words are sent, the data will be ignored. However, if less than the specified number of data words is sent, the RAM Access Controller will not return to the idle state until the sequence has been completed by receipt of the correct number of RAM data words. This will corrupt the sequence in the RAM if the next RAM data word received is not intended for that RAM element. A write sequence may be terminated early with a software reset (see section 3.3).

The 64-bit wide WMM [EVEN/ODD] RAM DATA registers are used to transfer pre-formatted data into the RAM address location selected by the RAM Access Controller. See Table 18. The 14-bit DAC data should be MSB aligned to the 15th bit of the waveform sample (DAC data D14 aligned to waveform bit 14 [15:0], i.e. register bits 0, 15, 16, 31, 32, 47, 48, 63 etc. are not used).

| WMM EVEN RAM<br>DATA<br>(bits) | Label     | Function                                    |

|--------------------------------|-----------|---------------------------------------------|

| [15:0]                         | prog_data | Waveform EVEN sample word <i>n</i>          |

| [31:16]                        |           | Waveform EVEN sample word <i>n+2</i>        |

| [47:32]                        |           | Waveform EVEN sample word <i>n+4</i>        |

| [63:48]                        |           | Waveform EVEN sample word <b><i>n</i>+6</b> |

Table 18: Waveform Memory Module Registers: WMM [EVEN/ODD] RAM DATA [0x13/0x23]

| WMM ODD RAM<br>DATA<br>(bits) | Label     | Function                                   |  |

|-------------------------------|-----------|--------------------------------------------|--|

| [15:0]                        | prog_data | Waveform ODD sample word <b>n+1</b>        |  |

| [31:16]                       |           | Waveform ODD sample word <b>n+3</b>        |  |

| [47:32]                       |           | Waveform ODD sample word <b><i>n</i>+5</b> |  |

| [63:48]                       |           | Waveform ODD sample word <b>n+7</b>        |  |

The following sequence could be followed,

- write the first pre-formatted RAM data word to register WMM EVEN RAM DATA

- write to register WMM EVEN RAM CTRL with bit prog\_start set

- consecutively write the remaining RAM data words to register WMM EVEN RAM DATA.

Disclaimer : The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering. The information and circuit diagrams in this document are presented "as is", no license is granted by implication or otherwise.

Once the RAM Access Controller returns to the idle state, after a successful write sequence, data transfer to the DACs starts automatically. Until the other RAM element is programmed, the output from the DAC will be corrupt.

• repeat the above sequence for the ODD RAM element. The order in which the EVEN/ODD RAMs are programmed is not important

Once all of the RAMs have been programmed, the RAM Access Controllers need to be synchronised. This is best achieved first by a master hardware reset followed by two software resets. As the WMM configuration registers, but not the RAMs, will be cleared by the master reset these should be reprogrammed. This is illustrated by the worked example in section 6.5.4.

### 3.3 Software Reset

The Waveform Memory Module may be reset through a software reset function. This is activated through register BIST [EVEN/ODD] CONFIG bit *swrst*. This bit is self clearing.

| WMM [EVEN/<br>ODD] CONFIG<br>(bit) | Label | Function                                                                                                                     |

|------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0                                  | swrst | Software reset control bit<br><b>0 = Normal operation (default)</b> , 1 = Software Reset<br><i>This bit is self clearing</i> |

Table 19: WMM Register: WMM [EVEN/ODD] CONFIG [0x10/0x20] (Part 2 of 2)

#### MB86064 Dual 14-bit 1GSa/s DAC

## 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

| Beremeter              | Notoo                                                                                                                                                 | Symbol             |                        | Units |                        |       |  |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|-------|------------------------|-------|--|--|--|--|--|

| Parameter              | Notes                                                                                                                                                 | Symbol             | Min.                   | Тур.  | Max.                   | Units |  |  |  |  |  |

| Supply voltage         |                                                                                                                                                       |                    |                        |       |                        |       |  |  |  |  |  |

| Analog supply          |                                                                                                                                                       | V <sub>AVD33</sub> |                        |       | 3.6                    | V     |  |  |  |  |  |

| Digital Supply         |                                                                                                                                                       | V <sub>DVDD</sub>  |                        |       | 2.0                    | V     |  |  |  |  |  |

| Input Voltage          |                                                                                                                                                       |                    |                        |       |                        |       |  |  |  |  |  |

| LVDS inputs            |                                                                                                                                                       | V <sub>LVDS</sub>  | V <sub>DVSS</sub> -0.5 |       | V <sub>DVDD</sub> +0.5 | V     |  |  |  |  |  |

| Digital control inputs |                                                                                                                                                       | V <sub>CON</sub>   | V <sub>DVSS</sub> -0.5 |       | V <sub>DVDD</sub> +0.5 | V     |  |  |  |  |  |

| Analog Output Voltage  |                                                                                                                                                       | Vo                 | V <sub>DVSS</sub> -1   |       | V <sub>DVDD</sub> +0.5 | V     |  |  |  |  |  |

| Analog Output Current  | 1                                                                                                                                                     | Ι <sub>Ο</sub>     |                        |       | +25                    | mA    |  |  |  |  |  |

| Storage Temperature    |                                                                                                                                                       | T <sub>ST</sub>    | -40                    |       | +85                    | °C    |  |  |  |  |  |

| Junction Temperature   |                                                                                                                                                       | ТJ                 | -40                    |       | +125                   | °C    |  |  |  |  |  |

|                        | $T_A$ (min) to $T_A$ (max), AVD33 = +3.3V, AVSS = 0V, DVDD = +1.8V, DVSS = 0V, I <sub>FS</sub> = 20mA.<br>1. IOUT & IOUTB AVSS - 0.5V to AVD18 + 0.5V |                    |                        |       |                        |       |  |  |  |  |  |

## 4.2 Digital Interface Specifications

| Deremeter                                                                                                                                   | Neteo | Symbol          |                              | Unito |                              |       |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|------------------------------|-------|------------------------------|-------|

| Parameter                                                                                                                                   | Notes | Symbol          | Min.                         | Тур.  | Max.                         | Units |

| CMOS control inputs                                                                                                                         |       |                 |                              |       |                              |       |

| High-level input voltage                                                                                                                    |       | VIH             | 1.2                          |       | V <sub>DVDD</sub>            | V     |

| Low-level input voltage                                                                                                                     |       | V <sub>IL</sub> | V <sub>DVSS</sub>            |       | 0.6                          | V     |

| CMOS control outputs                                                                                                                        |       |                 |                              |       |                              |       |

| High-level output voltage                                                                                                                   | 1     | V <sub>OH</sub> | V <sub>DVDD</sub> -<br>0.275 |       |                              | V     |

| Low-level output voltage                                                                                                                    | 2     | V <sub>OL</sub> |                              |       | V <sub>DVSS</sub> +<br>0.225 | V     |

| LVDS data inputs                                                                                                                            |       |                 |                              |       |                              |       |

| Common mode input voltage                                                                                                                   |       | V <sub>CM</sub> | 0.9                          |       | 1.4                          | V     |

| Differential input voltage                                                                                                                  |       | V <sub>ID</sub> | 100                          | 350   | 600                          | mV    |

| Setup time                                                                                                                                  | 3     | t <sub>s</sub>  | -0.4                         | -0.6  |                              | ns    |

| Hold time                                                                                                                                   | 3     | t <sub>h</sub>  |                              | 0.9   | 1.4                          | ns    |

| $T_A$ (min) to $T_A$ (max), AVD33 = +3.3V, AVSS =<br>1. $I_{OH}$ = +4mA<br>2. $I_{OL}$ = -4mA<br>3. Referenced to the input clock (CLKIN) & |       |                 |                              |       |                              |       |

Page 28 of 52

#### Production

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

# FUJITSU

## 4.3 DC Specifications

| Deromator                                         | Notes | Cumulant         |      | Linita |      |                  |

|---------------------------------------------------|-------|------------------|------|--------|------|------------------|

| Parameter                                         | Notes | Symbol           | Min. | Тур.   | Max. | Units            |

| DC Accuracy                                       |       |                  |      |        |      |                  |

| Integral Non Linearity                            |       | INL              |      | 1.1    | 2.0  | LSB <sub>1</sub> |

| Differential Non Linearity                        |       | DNL              |      | 0.6    | 1.0  | LSB <sub>1</sub> |

| Analog output                                     |       |                  |      |        |      |                  |

| Full scale signal output current                  |       | I <sub>OP</sub>  |      | +20    |      | mA               |

| Current at each output                            |       |                  | 5    | 15     | 25   | mA               |

| Load resistance (single ended)                    |       | RL               |      | 16.5   | 50   | Ω                |

| Output resistance                                 |       |                  |      | 330    |      | kΩ               |

| Output capacitance                                |       |                  |      | 22     |      | pF               |

| Gain error                                        |       |                  |      | 0.15   |      | %FS              |

| Output voltage (compliance) - Maximum             |       |                  | -1.0 |        | +0.5 | V                |

| Output voltage (compliance) - Best performance    |       |                  | -0.8 |        | +0.2 | V                |

| Output Power Supply Rejection Ratio               |       | PSRR             |      |        |      |                  |

| Due to variation in analog supply (External Vref) | 1     |                  |      | 0.01   |      | %                |

| Due to variation in analog supply (Internal Vref) | 1     |                  |      | 0.02   |      | %                |

| Internal Bandgap Reference                        |       |                  |      |        |      |                  |

| Reference voltage                                 |       | V <sub>BG</sub>  | 1.15 | 1.2    | 1.25 | V                |

| Reference output current                          |       | I <sub>BG</sub>  | 0    |        | 100  | μA               |

| Reference output voltage variation                | 1     | _                |      | 0.01   |      | %                |

| External Reference Input                          |       |                  |      |        |      |                  |

| Reference voltage                                 |       | V <sub>REF</sub> | 1.10 |        | 1.30 | V                |

| Reference input current                           |       | I <sub>BG</sub>  | -1   |        | +1   | μA               |

| Thermal                                           |       |                  |      |        |      |                  |

| Ambient Temperature                               |       | T <sub>A</sub>   | -40  | 25     | +85  | °C               |

| Storage Temperature                               |       | Τ <sub>S</sub>   | 5    |        | +30  | °C               |

| Package Thermal Resistance                        |       |                  |      |        |      |                  |

| Junction to PCB (top side)                        |       | $\theta_{J-PCB}$ |      | 4      |      | °C/W             |

| Junction to Ambient (estimate - PCB dependant)    | 2     | θ <sub>JA</sub>  |      | 20     |      | °C/W             |

2. Refer to Section 6.1

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

Production

# FUJITSU

## MB86064 Dual 14-bit 1GSa/s DAC

## 4.4 AC Specifications

| Doromotor                                     | Notoo | Symbol | Ratings |      |      | Units  |

|-----------------------------------------------|-------|--------|---------|------|------|--------|

| Parameter                                     | Notes |        | Min.    | Тур. | Max. | UTIILS |

| Spurious-Free Dynamic Range                   |       | SFDR   |         |      |      |        |

| Single tone at -1dBFS, 800MSa/s, DC to 400MHz | 1     |        |         |      |      |        |

| 20 MHz                                        |       |        |         | 75   |      | dBc    |

| 40 MHz                                        |       |        |         | 72   |      | dBc    |

| 70 MHz                                        |       |        |         | 66   |      | dBc    |

| 140 MHz                                       |       |        |         | 62   |      | dBc    |

| 300 MHz                                       |       |        |         | 58   |      | dBc    |

| Single tone at -1dBFS, 1GSa/s, DC to 500MHz   | 1     |        |         |      |      |        |

| 20 MHz                                        |       |        |         | 84   |      | dBc    |

| 40 MHz                                        |       |        |         | 80   |      | dBc    |

| 70 MHz                                        |       |        |         | 76   |      | dBc    |

| 140 MHz                                       |       |        |         | 68   |      | dBc    |

| 300 MHz                                       |       |        |         | 61   |      | dBc    |

| Single tone at -1dBFS, 800MSa/s, DC to 400MHz | 2     |        |         |      |      |        |

| 20 MHz                                        |       |        |         | 84   |      | dBc    |

| 40 MHz                                        |       |        |         | 79   |      | dBc    |

| 70 MHz                                        |       |        |         | 75   |      | dBc    |

| 140 MHz                                       |       |        | 70      | 76   |      | dBc    |

| 300 MHz                                       |       |        |         | 72   |      | dBc    |

| Single tone at -1dBFS, 1GSa/s, DC to 500MHz   | 2     |        |         |      |      |        |

| 20 MHz                                        |       |        |         | 84   |      | dBc    |

| 40 MHz                                        |       |        |         | 81   |      | dBc    |

| 70 MHz                                        |       |        |         | 77   |      | dBc    |

| 140 MHz                                       |       |        |         | 73   |      | dBc    |

| 300 MHz                                       |       |        |         | 74   |      | dBc    |

| Single tone at -1dBFS, 800MSa/s, ±100MHz      |       |        |         |      |      |        |

| 300 MHz                                       |       |        |         | 79   |      | dBc    |

| Inter-Modulation Distortion                   | 3     | IMD    |         |      |      |        |

| 4 tones, ea12dBFS, missing centre tone at     |       |        |         |      |      |        |

| 70MHz                                         |       |        |         | 89   |      | dBc    |

| 140MHz                                        |       |        | 75      | 85   |      | dBc    |

| 255MHz                                        |       |        |         | 75   |      | dBc    |

Page 30 of 52

Copyright © 2004 Fujitsu Microelectronics Europe GmbH

# FUĴITSU

| Nataa | Symbol                                   |                                                                   | Unite                                                                           |                                                                                                                                                                       |                                                                                                  |

|-------|------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Notes | Symbol                                   | Min.                                                              | Тур.                                                                            | Max.                                                                                                                                                                  | Units                                                                                            |

|       | ACLR                                     |                                                                   |                                                                                 |                                                                                                                                                                       |                                                                                                  |

|       |                                          |                                                                   |                                                                                 |                                                                                                                                                                       |                                                                                                  |

|       |                                          |                                                                   | 84                                                                              |                                                                                                                                                                       | dBc                                                                                              |

|       |                                          |                                                                   | 76                                                                              |                                                                                                                                                                       | dBc                                                                                              |

|       |                                          |                                                                   |                                                                                 |                                                                                                                                                                       |                                                                                                  |

|       |                                          | 69                                                                | 74                                                                              |                                                                                                                                                                       | dBc                                                                                              |

|       |                                          |                                                                   |                                                                                 |                                                                                                                                                                       |                                                                                                  |

|       | F <sub>clk</sub> - F <sub>sig</sub>      |                                                                   | 40                                                                              | 30                                                                                                                                                                    | dBc                                                                                              |

|       | F <sub>clk</sub> -<br>2.F <sub>sig</sub> |                                                                   | 57                                                                              | 50                                                                                                                                                                    | dBc                                                                                              |

|       | Notes                                    | ACLR<br>F <sub>clk</sub> - F <sub>sig</sub><br>F <sub>clk</sub> - | ACLR<br>ACLR<br>69<br>F <sub>clk</sub> - F <sub>sig</sub><br>F <sub>clk</sub> - | Min.         Typ.           ACLR         84           69         74           F <sub>clk</sub> - F <sub>sig</sub> 40           F <sub>clk</sub> - F <sub>sig</sub> 57 | Notes         Symbol         Min.         Typ.         Max.           ACLR         84         76 |

coupled output presenting  $33\Omega$  effective differential load, Filtered Sinewave clock unless otherwise specified.

1. Excludes  $f_{clk} \& f_{clk}$ -f<sub>out</sub> image

2. Excludes f<sub>clk</sub>, f<sub>clk</sub>-f<sub>out</sub> & f<sub>clk</sub>-2.f<sub>out</sub> images

3. 240kHz tone spacing with non-aligned phase alignment. Peak to rms = 6.4dB. 800MSa/s

## 4.5 Dynamic Performance

| Parameter                                                       | Neter | Carabal            |          |      |             |        |

|-----------------------------------------------------------------|-------|--------------------|----------|------|-------------|--------|

|                                                                 | Notes | Symbol             | Min.     | Тур. | Max.        | Units  |

| Analog Output                                                   |       |                    |          |      |             |        |

| CLK In to Analog Out delay (to 0.1%)                            |       | to                 |          | 4.1  |             | ns     |

| Output settling time (to 0.1%)                                  |       | t <sub>set</sub>   |          | 1.8  |             | ns     |

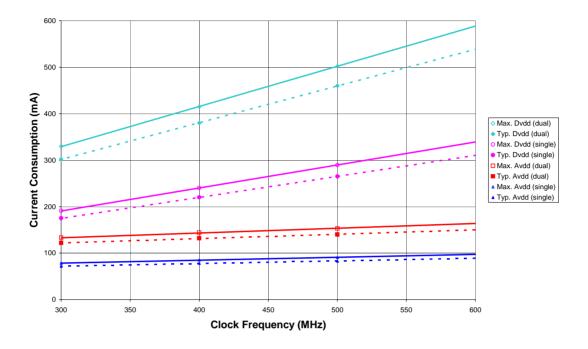

| Output rise time (10% to 90%)                                   |       | t <sub>r</sub>     |          | 0.6  |             | ns     |